Concept

In the domain of high-frequency trading (HFT), the velocity of information processing is the primary determinant of success. The interval between receiving market data and acting upon it ▴ a duration measured in microseconds and nanoseconds ▴ defines the boundary between profit and loss. The core challenge is not merely one of computation, but of physical and architectural limitations. General-purpose Central Processing Units (CPUs), while versatile, operate on a sequential instruction-based model.

This approach introduces inherent, unpredictable delays known as jitter, stemming from operating system interrupts, context switching, and layers of software abstraction. For an HFT system, this variability is an existential threat.

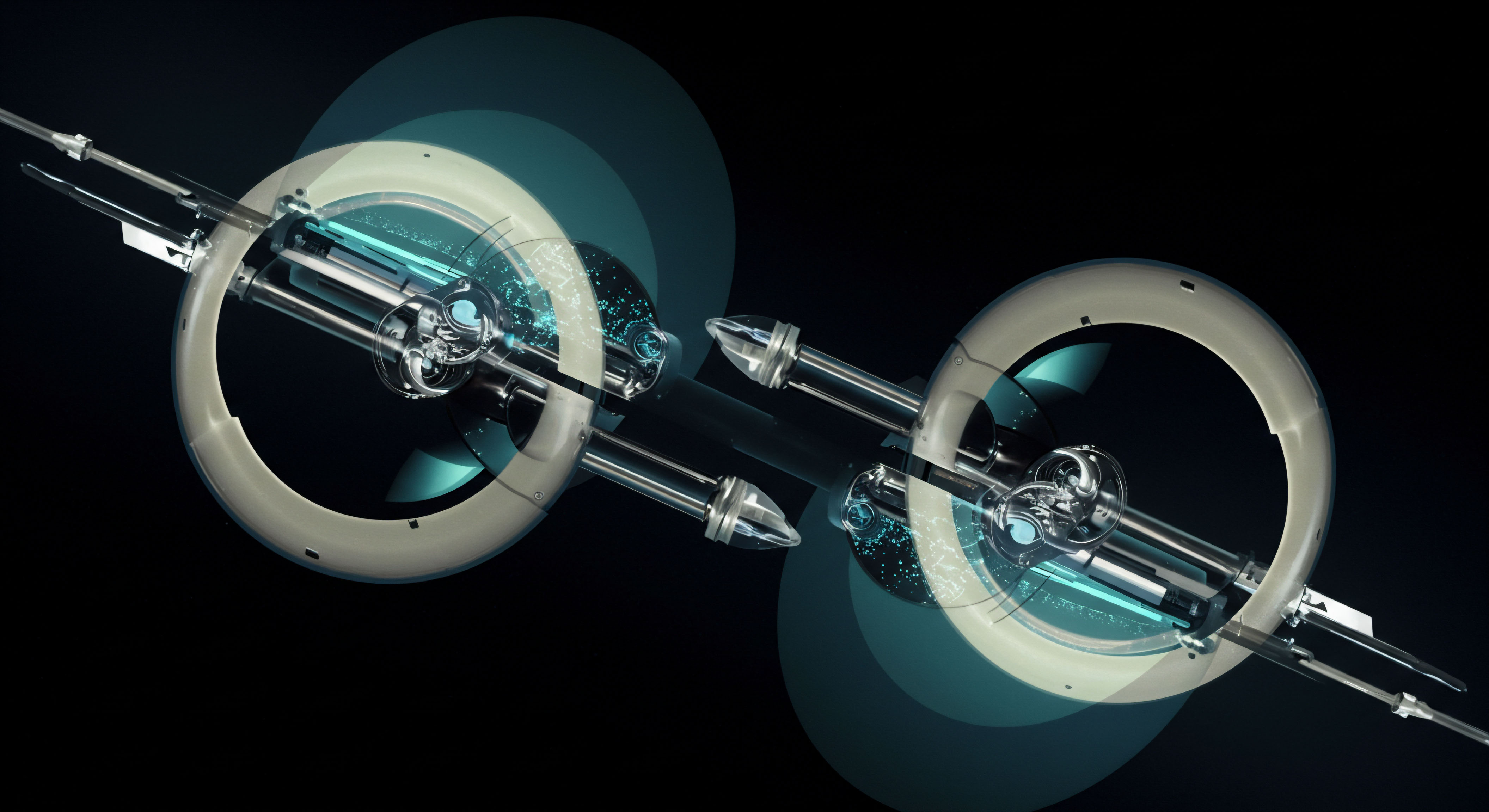

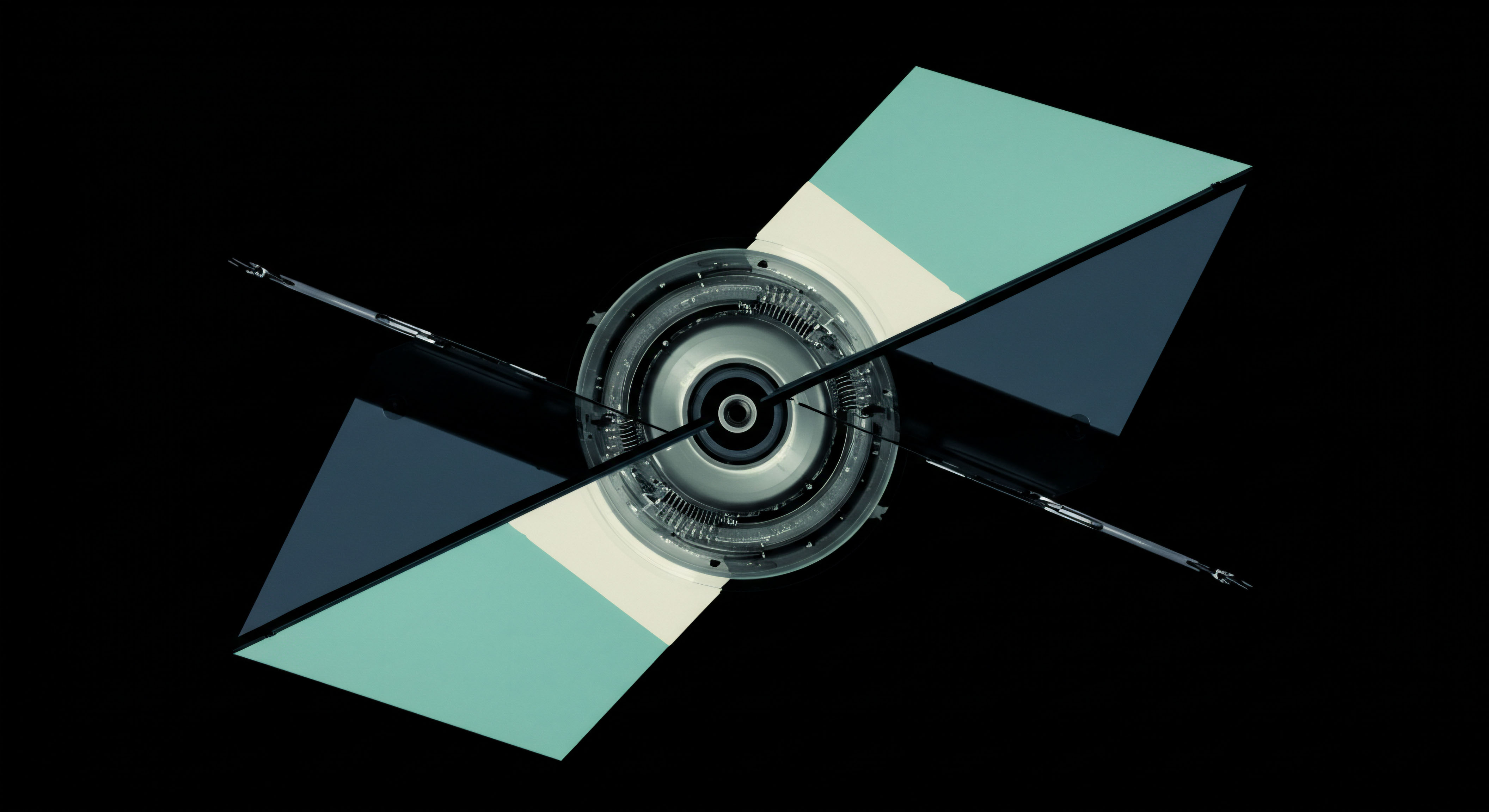

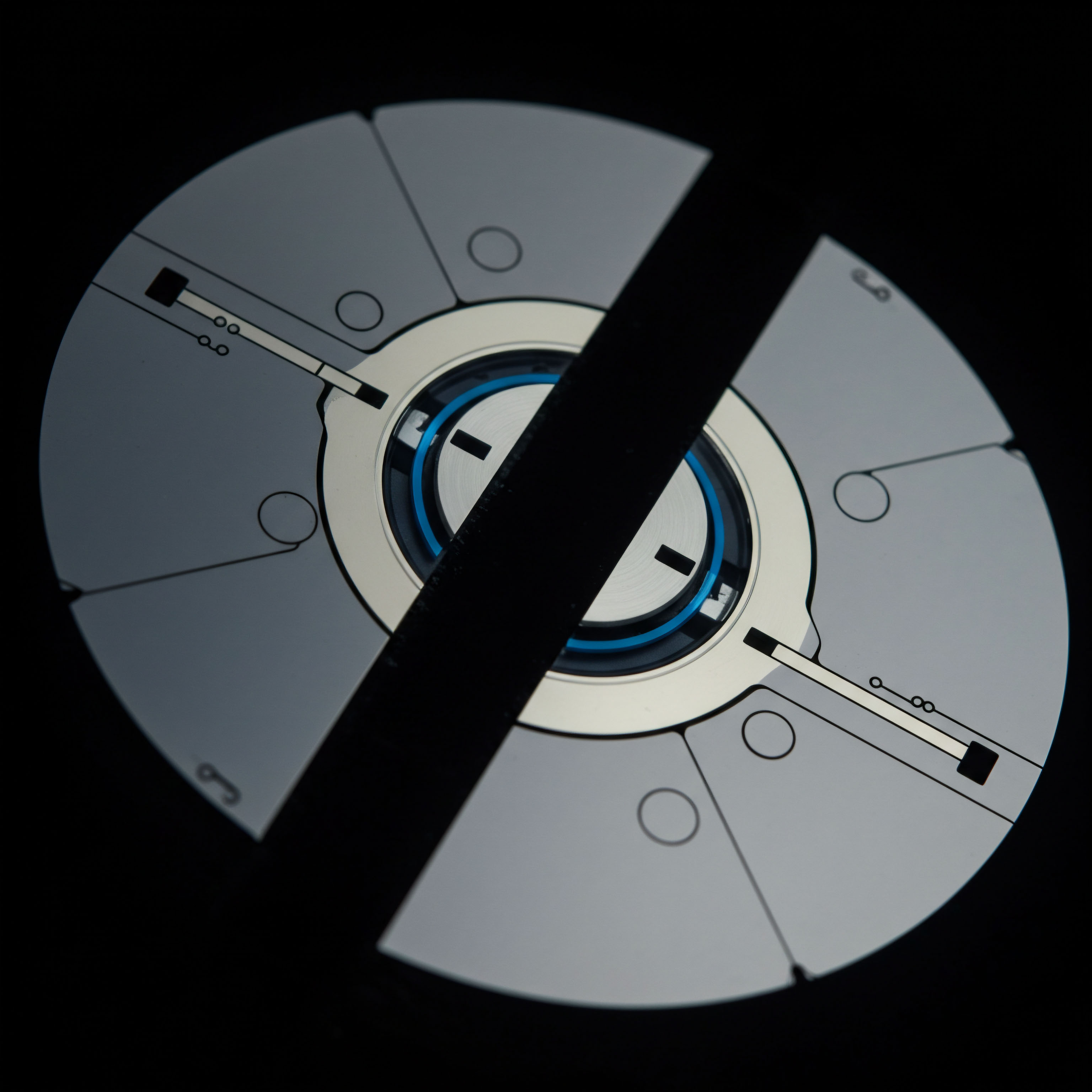

Field-Programmable Gate Arrays (FPGAs) provide a fundamentally different paradigm. An FPGA is a semiconductor device containing a matrix of configurable logic blocks (CLBs) and programmable interconnects. Instead of executing a sequence of software instructions, an FPGA is configured to become the circuit itself ▴ a hardware implementation of the trading algorithm. This transformation from a general-purpose processor to a specialized, task-specific digital circuit allows for a deterministic and massively parallel processing architecture.

The system is no longer running a program; the system is the program. This distinction is the foundational reason FPGAs are integral to modern low-latency data capture systems.

FPGAs reduce latency by processing data in hardware, executing multiple tasks in parallel and bypassing the software and operating system overhead inherent to CPUs.

The Deterministic Nature of Hardware

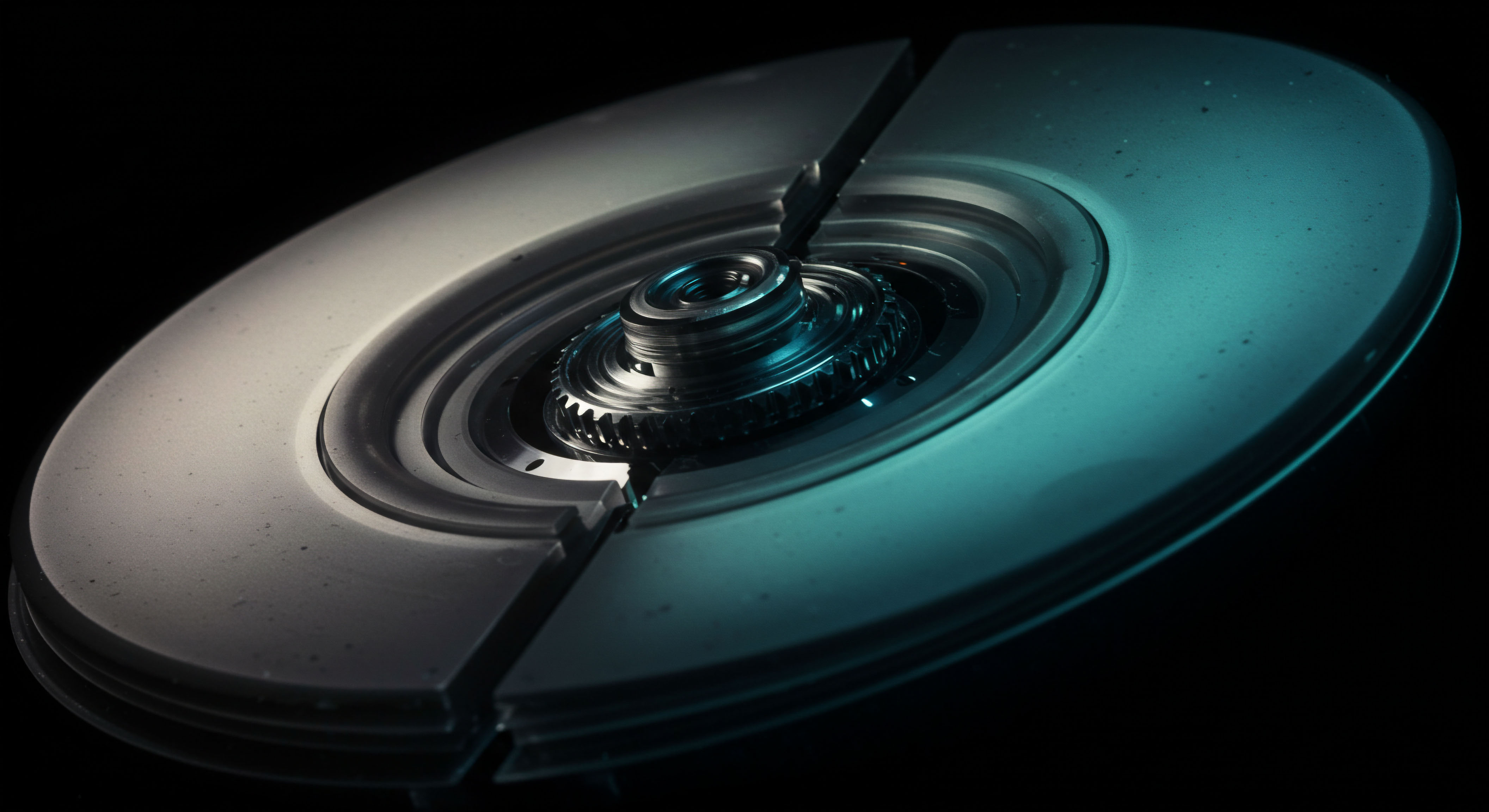

The primary advantage of an FPGA in an HFT context is its determinism. Because the logic is etched into the hardware configuration, the time taken to process a data packet is constant and predictable, irrespective of market data volume or other system tasks. A CPU-based system, conversely, will exhibit fluctuating processing times, especially during market volatility when data rates surge. This is because the CPU must juggle multiple processes, leading to queuing delays and unpredictable latency spikes.

An FPGA, dedicated to its specific task, processes each packet through the same physical logic gates every time, resulting in a fixed, ultra-low latency. This consistency allows HFT firms to build strategies based on a known, repeatable time budget for every single action.

Parallelism at the Gate Level

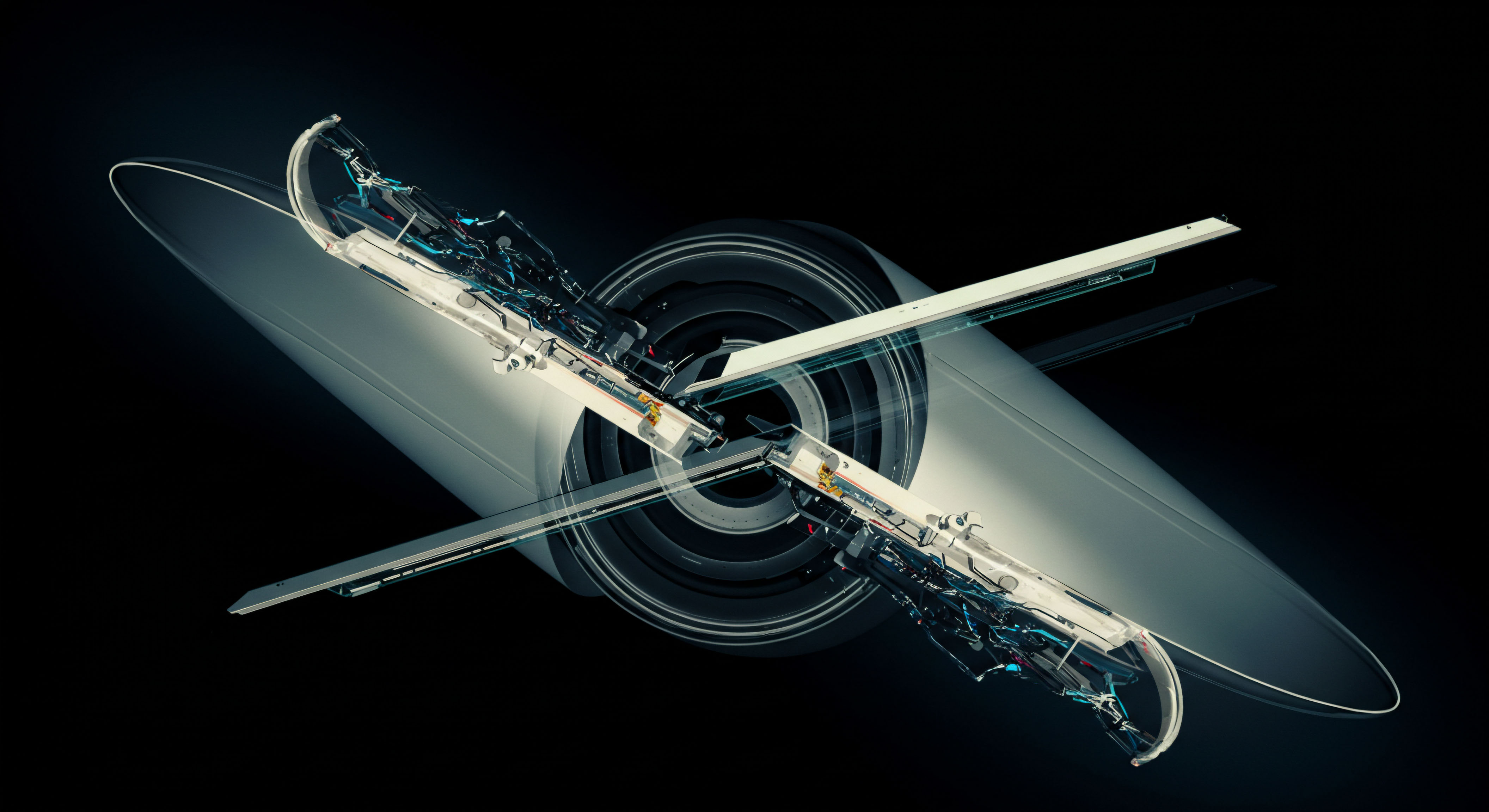

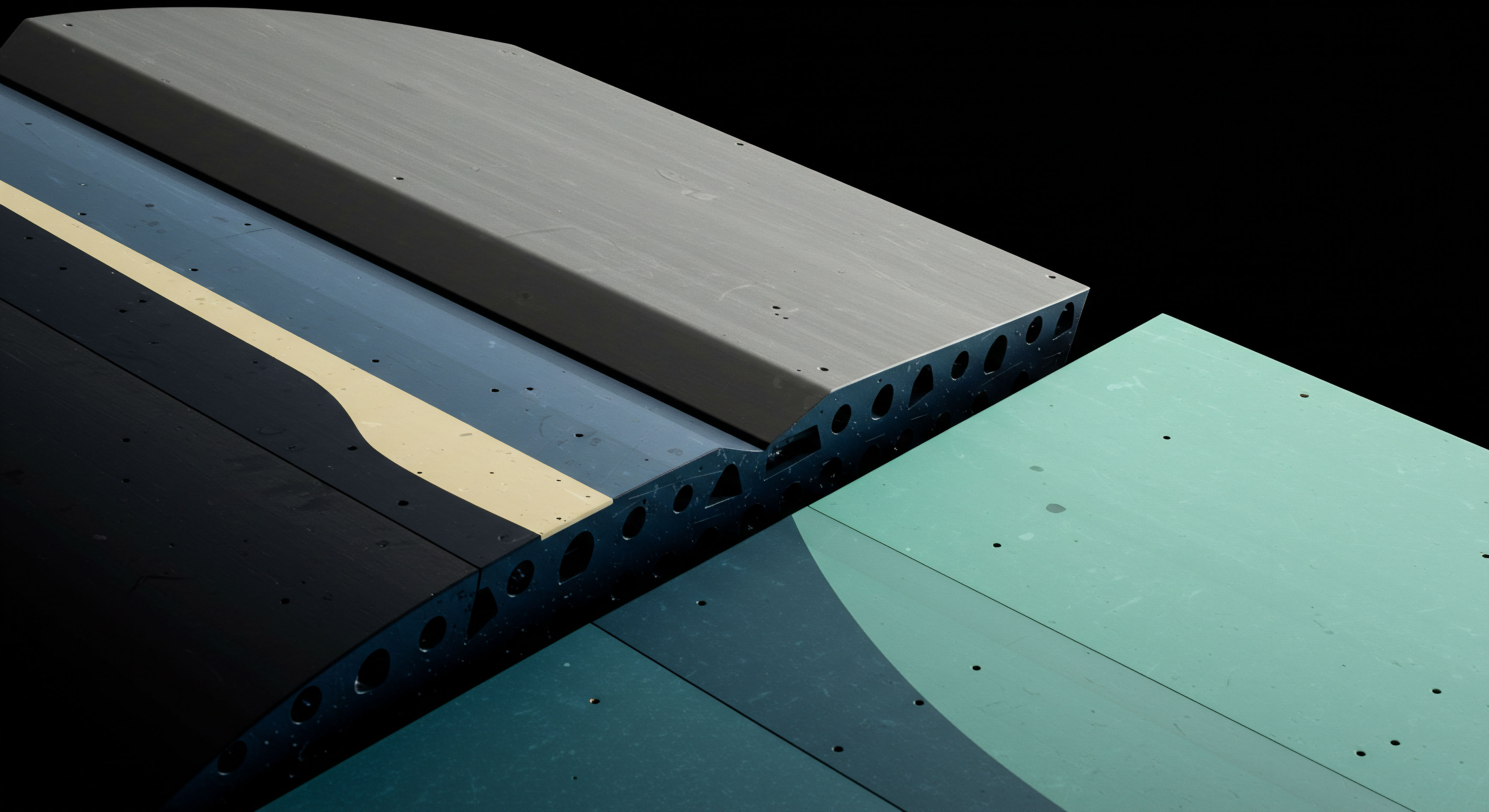

CPUs are fundamentally sequential, executing one instruction after another (albeit with multiple cores). FPGAs, by contrast, embody true parallelism. An entire algorithm, from network packet filtering to market data parsing and even order book construction, can be implemented as a pipeline of concurrent hardware logic. As a data packet enters the FPGA, it flows through these dedicated logic stages simultaneously.

Different functions do not compete for the same resources because they are physically separate circuits on the chip. This structure eliminates the bottlenecks inherent in sequential processing, allowing for sustained high throughput even under the most demanding market conditions. A single chip can process multiple data streams from different exchanges in parallel, a task that would cripple a CPU-based system with context-switching overhead.

Strategy

The strategic adoption of FPGAs in HFT data capture systems is centered on offloading latency-critical tasks from software to hardware. This is a deliberate architectural choice to move specific functions to a substrate that can execute them with superior speed and predictability. The objective is to construct a hybrid system where FPGAs handle the initial, high-velocity stages of data processing, preparing a refined data stream for the higher-level strategic logic that may still reside on a CPU. This division of labor leverages the strengths of each component, creating a system that is greater than the sum of its parts.

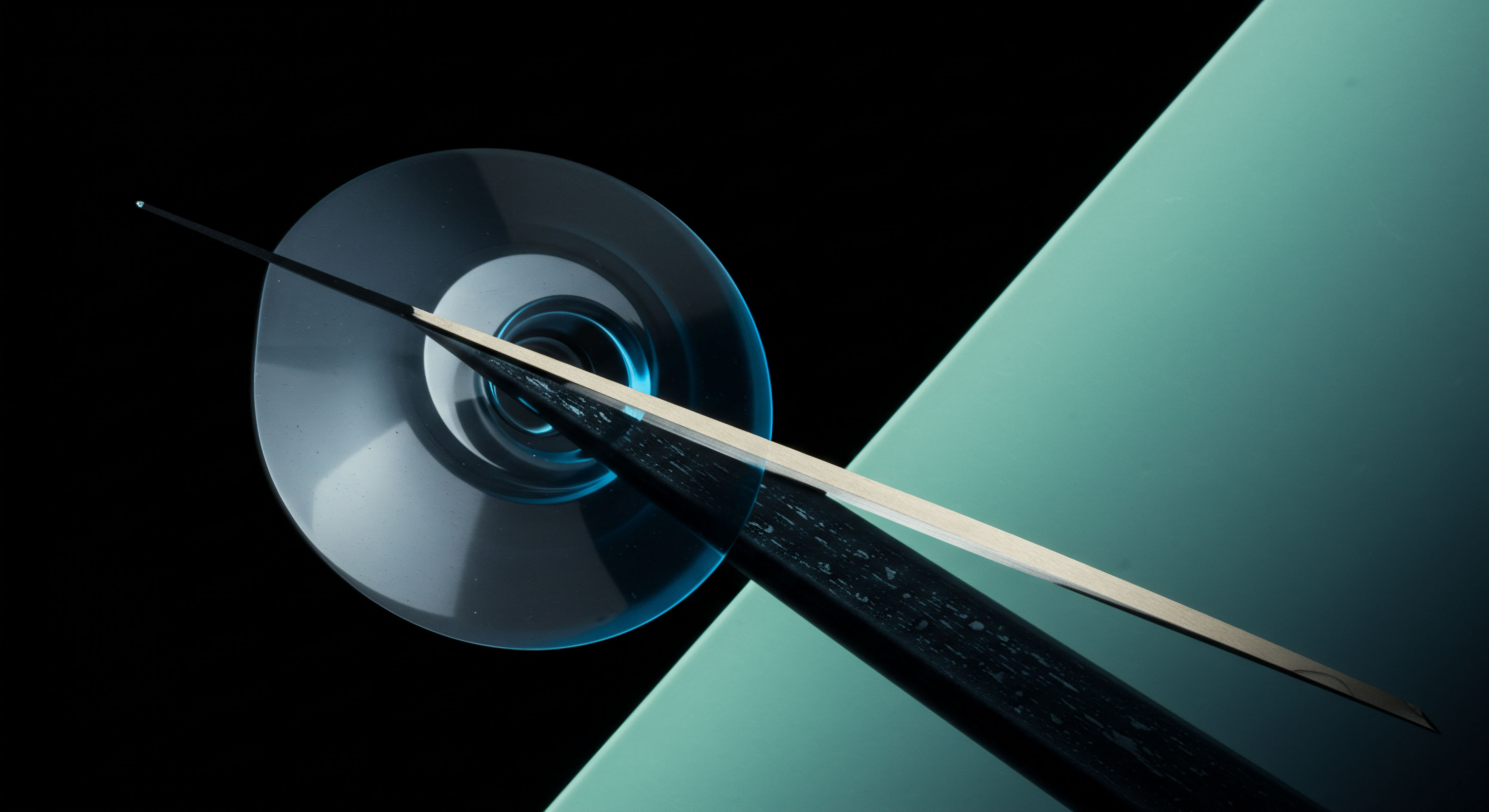

A core strategy involves using the FPGA as a “bump-in-the-wire” directly connected to the network feed. This placement allows the FPGA to intercept and process raw market data packets directly from the Ethernet connection, bypassing the server’s operating system kernel and network stack entirely. This technique, known as kernel bypass, eliminates a significant source of latency and jitter, often saving several microseconds per message. The FPGA performs tasks like UDP/IP stack termination, FAST protocol decoding, and message parsing in hardware before the data ever reaches the main processor.

By implementing critical data processing tasks directly in silicon, FPGAs provide a deterministic, ultra-low-latency path from network packet to actionable trading signal.

Hardware Offloading and Data Filtering

One of the most effective strategies is to use the FPGA for intelligent data filtering at the wire. Market data feeds are voluminous and often contain information that is irrelevant to a specific trading strategy. A CPU-based system would have to receive the entire data stream, process it, and then discard the unwanted information, wasting valuable cycles. An FPGA, however, can be programmed to filter packets in real-time based on criteria such as the instrument symbol.

This means the CPU is only presented with data that is relevant to its trading logic, reducing its processing load and allowing it to focus on more complex calculations. This pre-processing at network speeds is a significant strategic advantage, as it conserves precious downstream computational resources.

Comparative Latency Profile ▴ FPGA Vs. CPU

The strategic value of FPGAs becomes evident when comparing their performance metrics against traditional CPU-based systems for the initial data capture and processing stages. The table below provides an illustrative comparison.

| Processing Stage | Typical CPU Latency | Typical FPGA Latency | Latency Reduction |

|---|---|---|---|

| Packet Reception (Kernel Bypass) | 5-10 µs | ~500 ns | 90-95% |

| Market Data Decoding (e.g. FAST) | 2-5 µs | ~300 ns | 85-94% |

| Order Book Building (Simple) | 1-3 µs | ~200 ns | 80-93% |

| Total Initial Processing | 8-18 µs | ~1 µs | 87-94% |

The Hybrid Architecture Advantage

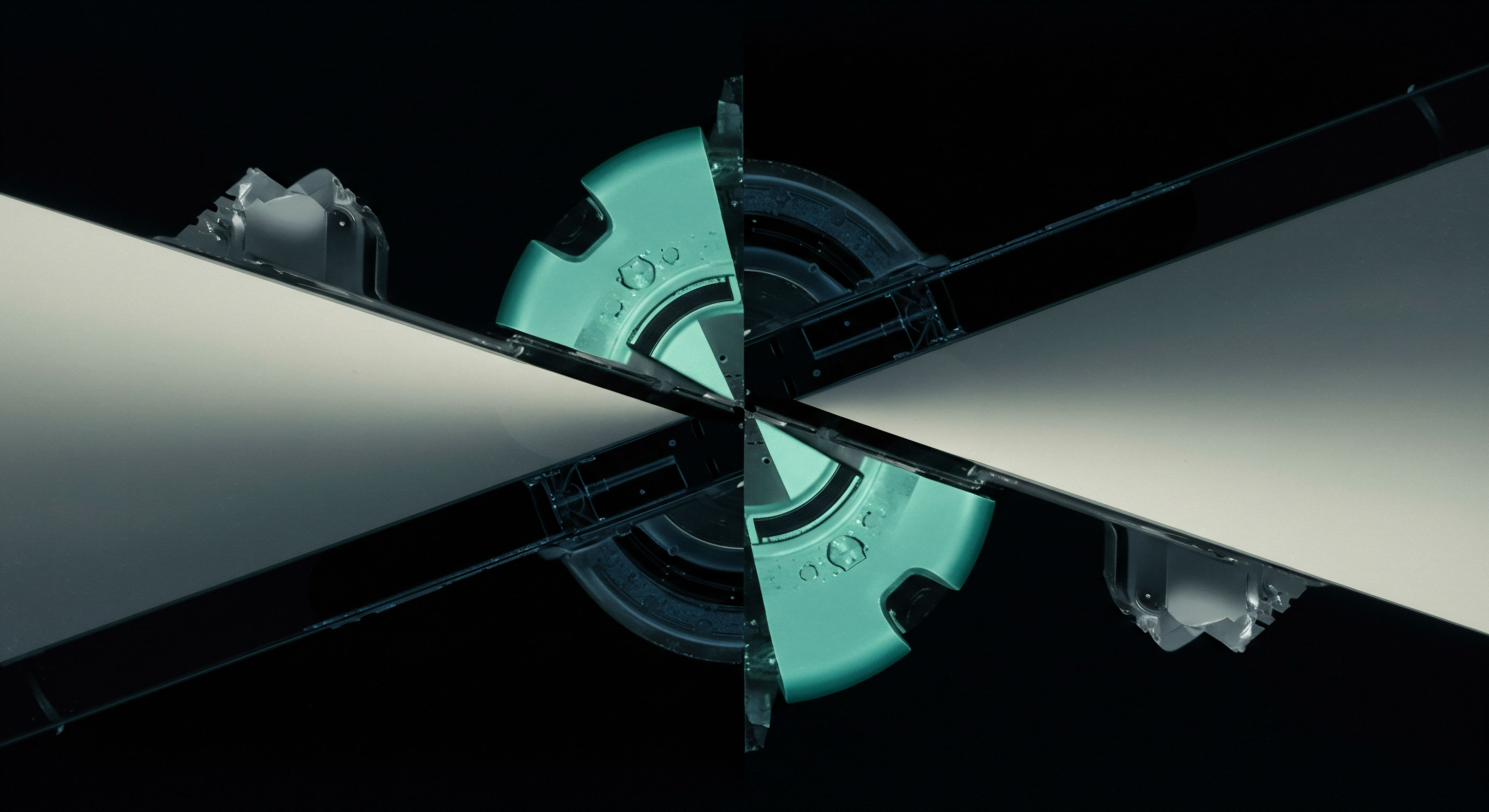

A sophisticated strategy involves creating a hybrid architecture that combines the strengths of both FPGAs and CPUs. In this model, the FPGA handles the deterministic, high-speed, and repetitive tasks of data capture and normalization. The CPU, freed from these low-level burdens, can then execute more complex, stateful trading strategies, perform risk analysis, or run machine learning models that are less suitable for hardware implementation.

This synergy allows firms to maintain flexibility in their strategy development (a strength of software) while achieving the raw speed of hardware execution. Some advanced systems even feature a hard CPU core integrated within the FPGA fabric, further tightening the integration and reducing communication latency between the hardware and software domains.

Execution

The execution of an FPGA-based data capture system is a complex engineering discipline that requires a fusion of hardware design, software integration, and deep market knowledge. It moves beyond theoretical advantages to the practical realities of implementation, where every nanosecond is accounted for in a meticulously designed data path. The goal is to create a seamless flow of information from the network wire to the trading logic with the absolute minimum of delay and variance.

The Operational Playbook

Deploying an FPGA solution is a multi-stage process that demands rigorous planning and specialized expertise. It is a departure from traditional software development cycles and requires a hardware-centric mindset.

- System Requirements Definition ▴ The initial phase involves identifying the precise functions to be offloaded to the FPGA. This includes specifying the target exchanges, the market data protocols (e.g. ITCH, SBE, FAST), and the filtering criteria. A detailed latency budget must be created, allocating nanoseconds to each stage of the hardware pipeline.

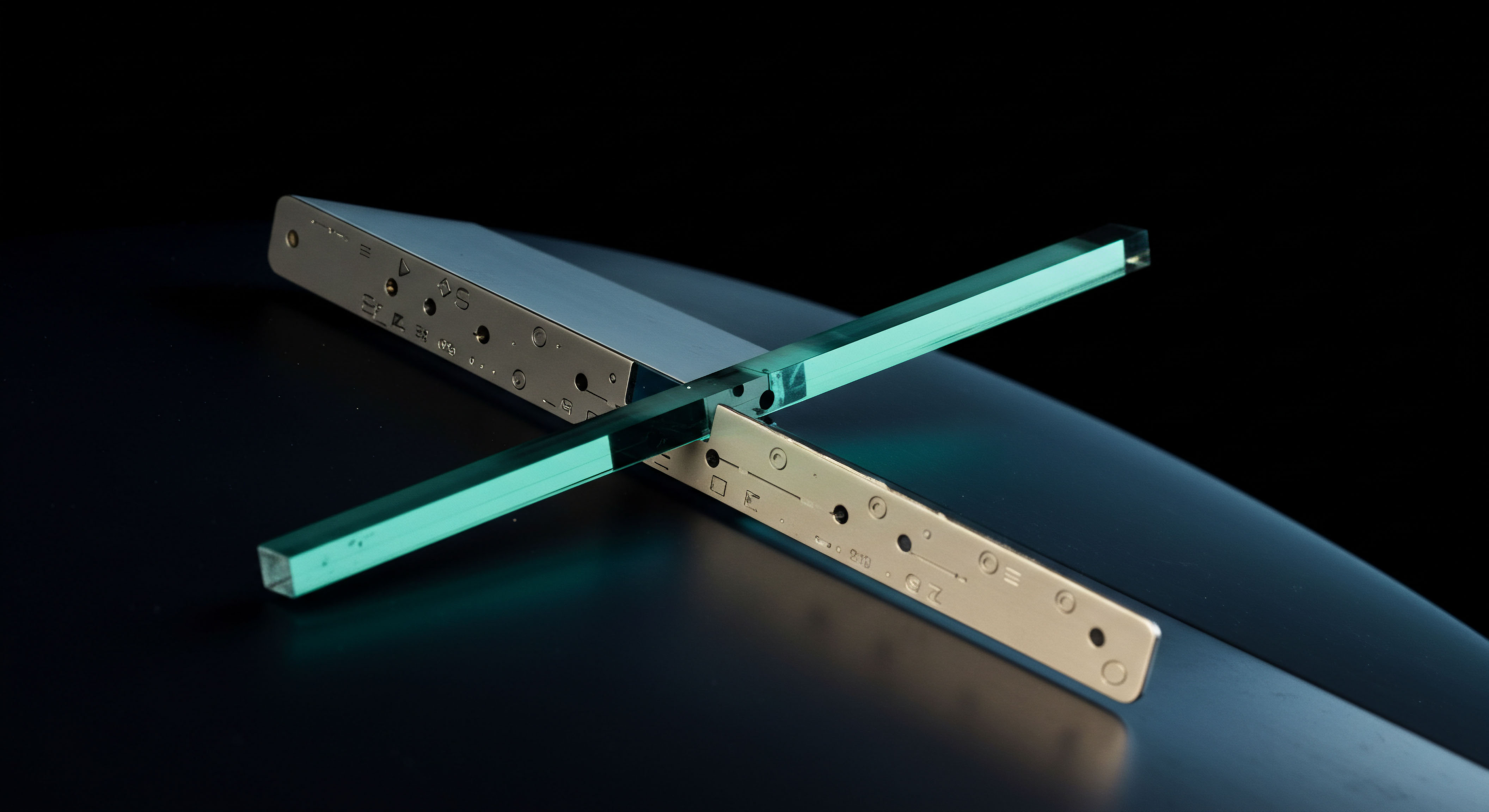

- FPGA Platform Selection ▴ Choosing the right hardware is essential. Factors to consider include the number of logic gates, available on-chip memory (Block RAM), the speed of the transceivers (for network connectivity), and the development environment provided by the vendor (e.g. Xilinx, Intel).

- Hardware Description Language (HDL) Development ▴ The core logic is typically written in a hardware description language like Verilog or VHDL. This code describes the digital circuits that will perform the tasks of packet parsing, filtering, and data normalization. This is a highly specialized skill, distinct from software programming.

- High-Level Synthesis (HLS) ▴ To accelerate development, many firms use High-Level Synthesis tools. HLS allows engineers to write algorithms in higher-level languages like C++ or OpenCL, which the tool then compiles into HDL. This can significantly reduce development time, though it may require manual optimization to achieve the lowest possible latency.

- Simulation and Verification ▴ Before deploying to the physical device, the FPGA design undergoes extensive simulation. This “testbench” environment feeds the design with recorded market data to verify its logical correctness and timing performance. Any errors in the hardware design can be far more costly to fix than software bugs.

- Integration and Deployment ▴ Once verified, the compiled hardware design (the “bitstream”) is loaded onto the FPGA card, which is typically a PCIe card installed in a server. The final step is to integrate the FPGA with the software part of the trading application, using a custom API to manage the low-latency data path between the two.

Quantitative Modeling and Data Analysis

The decision to implement an FPGA solution is driven by quantitative analysis. A latency budget analysis is fundamental to this process, as is a thorough cost-benefit model.

The ultimate measure of an HFT system is its tick-to-trade latency ▴ the time from a market event’s arrival at the data center to the corresponding order leaving for the exchange.

Latency Budget Breakdown

The following table models the latency contribution of each component in a hypothetical HFT system, comparing a purely software-based approach with an FPGA-accelerated hybrid system.

| System Component | Software-Only Latency (ns) | FPGA-Accelerated Latency (ns) | Notes |

|---|---|---|---|

| Network Ingress (NIC to App) | 4,000 | 250 | FPGA performs kernel bypass and delivers data directly to application memory. |

| Market Data Deserialization | 2,500 | 150 | FPGA decodes binary protocols in dedicated hardware pipelines. |

| Order Book Update | 1,500 | 100 | FPGA maintains the top of the book in on-chip memory. |

| Trading Strategy Logic | 500 | 500 | Assumes strategy logic runs on CPU in both scenarios. |

| Order Generation & Risk Check | 1,000 | 50 | FPGA can perform pre-trade risk checks in hardware. |

| Network Egress (App to NIC) | 3,000 | 200 | FPGA handles packet formation and hands off directly to the NIC. |

| Total Tick-to-Trade Latency | 12,500 ns (12.5 µs) | 1,250 ns (1.25 µs) | A 10x reduction in total latency. |

Predictive Scenario Analysis

Consider a mid-sized quantitative hedge fund, “Momentum Quantitative Strategies,” that specializes in statistical arbitrage. They identify a fleeting pricing discrepancy between a stock and its corresponding future, an opportunity that typically vanishes within 5-10 microseconds. Their existing CPU-based system has a P99 tick-to-trade latency of 12 microseconds, meaning they are too slow to capture a significant portion of these opportunities. They initiate a project to develop an FPGA-based data capture system.

The engineering team spends six months developing a solution that offloads the market data handling for the two relevant exchanges and performs the spread calculation directly on the FPGA. The new system is deployed, and post-launch analysis reveals the P99 latency has dropped to 1.5 microseconds. This 10.5-microsecond improvement fundamentally changes their strategy’s viability. They are now consistently among the first to react to these pricing discrepancies.

Within the first quarter of deployment, the strategy’s profitability increases by 40%, directly attributable to the latency reduction. The FPGA implementation has transformed a marginal strategy into a significant profit center, validating the substantial investment in hardware engineering. The success of this initial deployment provides the firm with a reusable, low-latency framework, which they can now adapt to other exchanges and strategies, creating a lasting competitive advantage.

System Integration and Technological Architecture

The FPGA is not a standalone device; it is a component within a larger, highly optimized technological ecosystem. Its integration is a critical aspect of the overall system design.

- Physical Connectivity ▴ The FPGA card is typically housed in a server co-located at the exchange’s data center. It connects directly to the raw market data feeds via fiber optic cables plugged into the card’s high-speed transceivers (e.g. 10/25/100 GbE).

-

Data Flow ▴ Raw Ethernet frames carrying market data enter the FPGA. The hardware logic performs the following sequence in a continuous pipeline:

- Ethernet, IP, and UDP headers are parsed.

- The payload, containing the exchange’s proprietary binary market data message, is extracted.

- The message is decoded, and relevant fields (price, quantity, order ID) are extracted.

- This information is used to update a representation of the order book stored in the FPGA’s fast on-chip memory.

- A trigger condition, representing the trading opportunity, is evaluated in hardware.

- CPU Interaction ▴ When a trigger is fired, the FPGA sends a small, highly specific notification to the trading application running on the host server’s CPU via the PCIe bus. This message might contain the calculated spread or simply an alert that a specific condition has been met. The CPU then performs any final confirmations and sends the order. In more advanced systems, the FPGA itself can construct and send the outbound order packet, reducing latency even further.

- Software API ▴ A lean software API provides the interface for the trading application to configure the FPGA (e.g. to tell it which symbols to watch) and to receive the low-latency signals from the hardware. This API is a critical piece of the puzzle, as a poorly designed interface can introduce software latency that negates the gains from the hardware.

References

- Leber, C. B. Geib, and H. Litz. “High Frequency Trading Acceleration Using FPGAs.” 2011 21st International Conference on Field Programmable Logic and Applications, 2011.

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- Lockwood, J. W. et al. “FPGA-based packet parsing for network intrusion detection.” Proceedings of the 2002 ACM/SIGDA tenth international symposium on Field-programmable gate arrays, 2002.

- Weinert, A. et al. “A survey on hardware-based low-latency processing of financial market data.” ACM Computing Surveys (CSUR), vol. 53, no. 1, 2020, pp. 1-37.

- de Bree, M. et al. “An FPGA-based low-latency solution for market data processing.” 2012 International Conference on Reconfigurable Computing and FPGAs (ReConFig), 2012.

- Vo, D. et al. “A quantitative analysis of the speedup factors of FPGAs over processors.” Proceedings of the 2004 ACM/SIGDA 12th international symposium on Field programmable gate arrays, 2004.

- Papadimitriou, K. et al. “High-level synthesis for high-frequency trading ▴ a case study.” 2013 23rd International Conference on Field programmable Logic and Applications, 2013.

Reflection

The Silicon Expression of Strategy

The integration of FPGAs into HFT systems represents a profound shift in how trading logic is conceived and executed. It marks the point where a trading strategy is no longer just a piece of software but becomes a physical artifact ▴ a bespoke circuit designed for a singular purpose. The knowledge gained about this technology prompts a critical examination of one’s own operational framework. It compels a shift in perspective from viewing technology as a support function to seeing it as the very medium in which strategy is expressed.

Understanding the mechanics of hardware acceleration is the first step. The true strategic potential, however, is realized when this understanding is integrated into a holistic view of the market. The ability to control latency at the nanosecond level is not an end in itself.

It is a tool that unlocks new possibilities for discovering and capturing alpha. The ultimate edge lies not in possessing the technology, but in the intellectual framework that guides its application ▴ in the ability to envision a market opportunity and translate that vision into a precise, deterministic, and ruthlessly efficient silicon reality.

Glossary

High-Frequency Trading

Market Data

Fpga

Data Capture

Cpu-Based System

Order Book

Kernel Bypass

Verilog

High-Level Synthesis

Tick-To-Trade

Latency Reduction