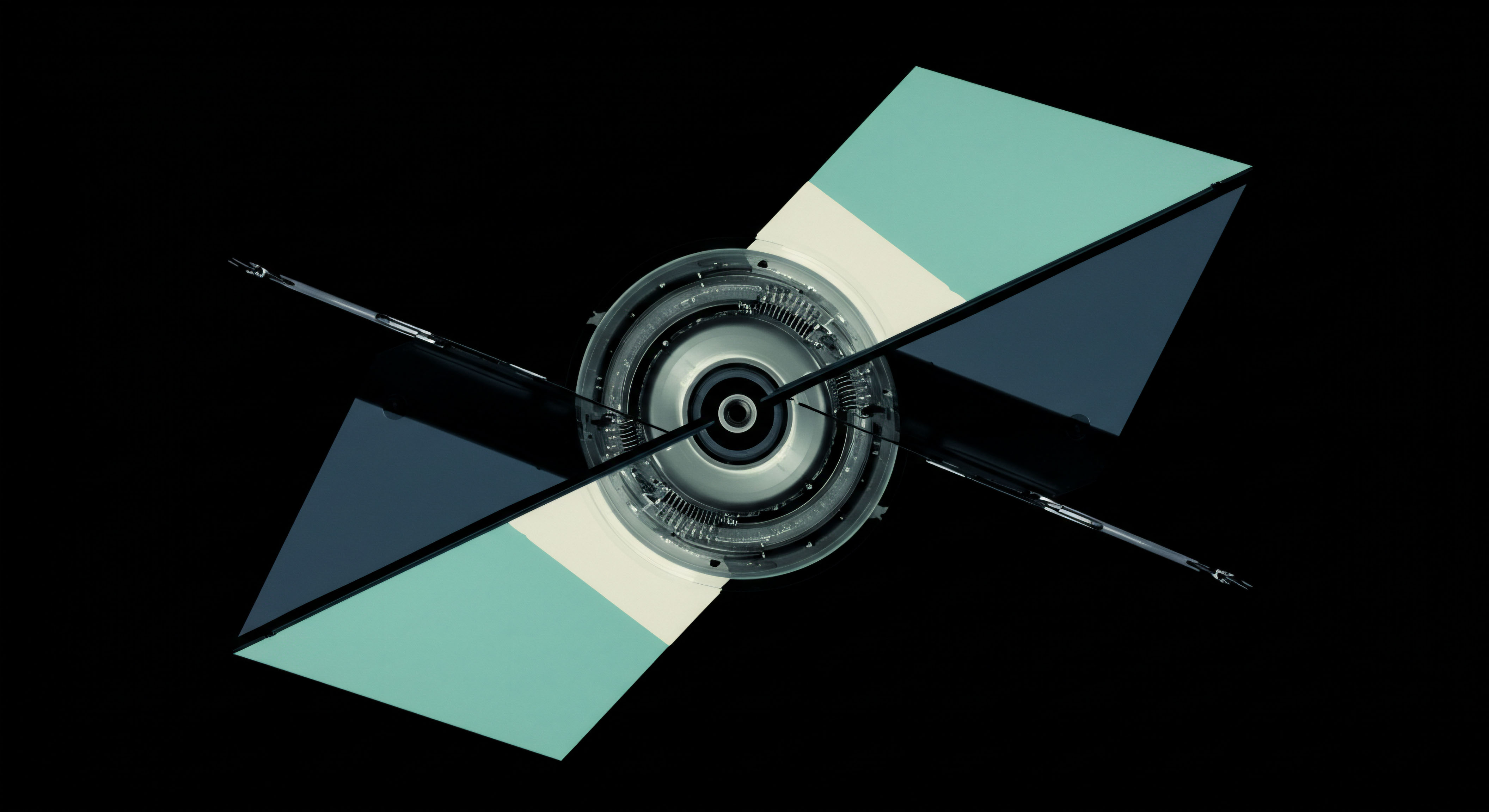

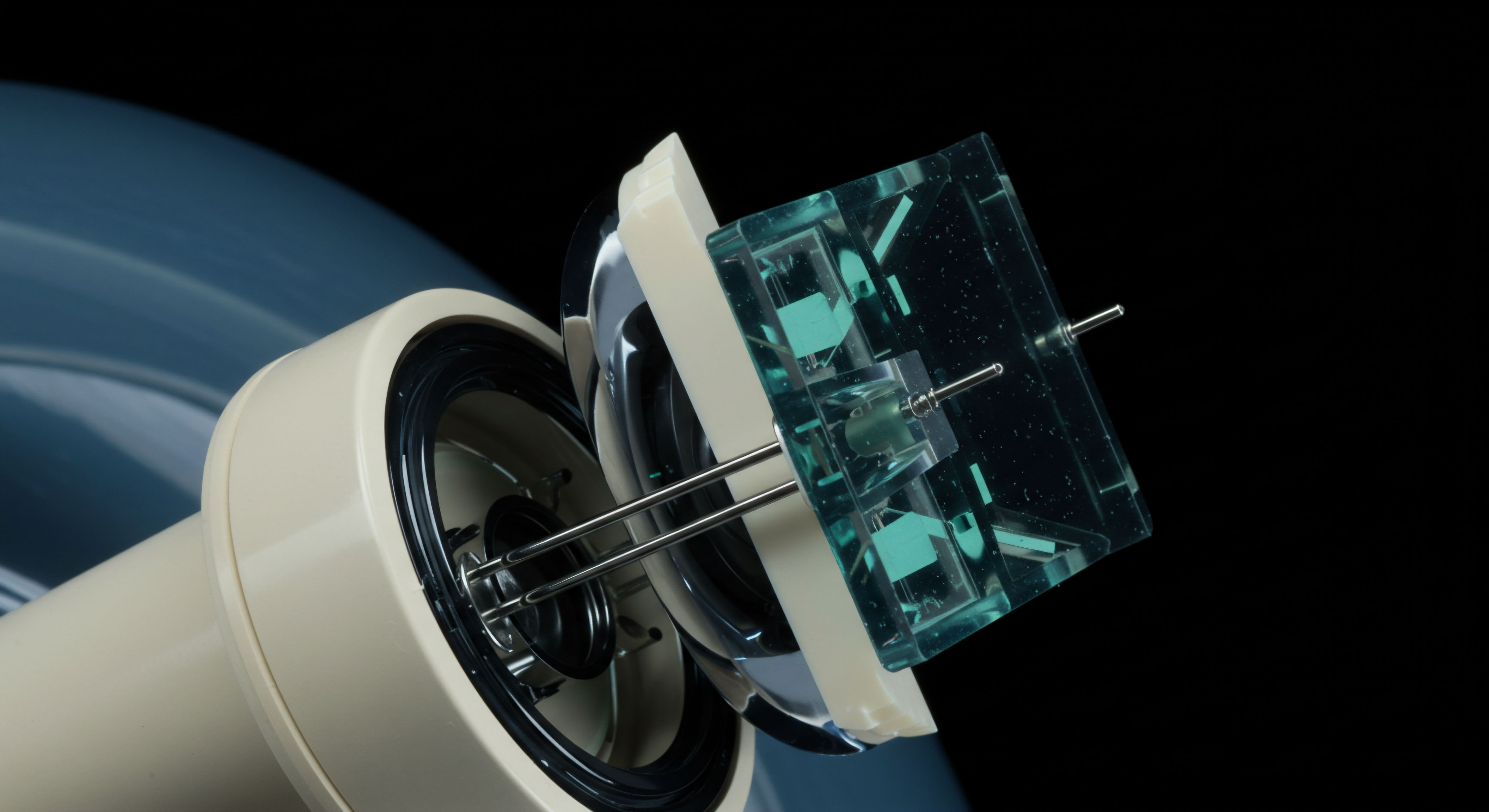

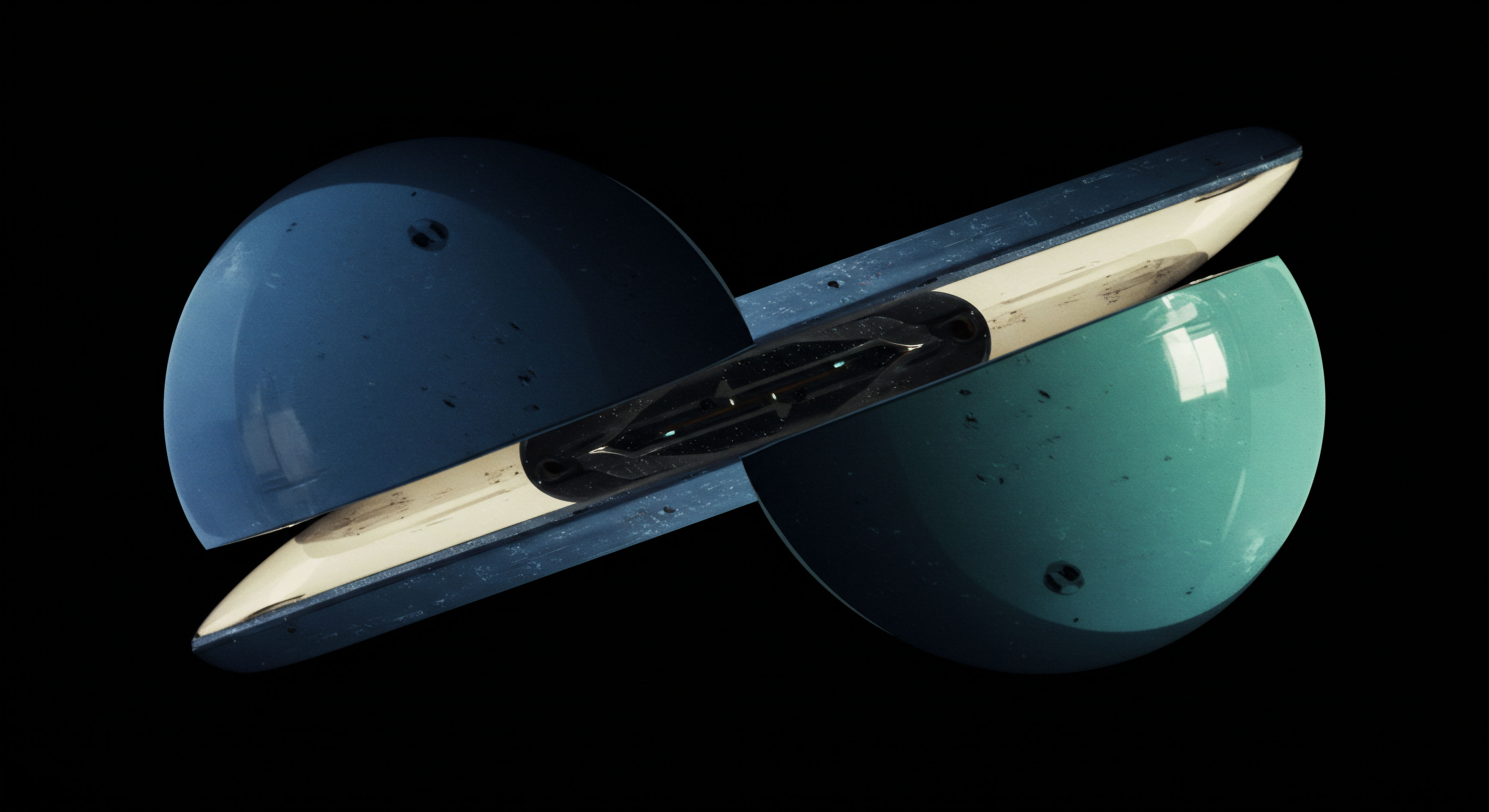

Concept

The Silicon Bedrock of Speed

In the domain of institutional trading, the velocity of information processing is a primary determinant of execution quality. The journey of a quote, from its conception within a pricing engine to its arrival at an exchange, is fraught with checkpoints. Each of these validation stages, however necessary for risk and compliance, introduces a delay. When these checks are performed in software running on general-purpose CPUs, the latency is measured in microseconds, an eternity in modern markets.

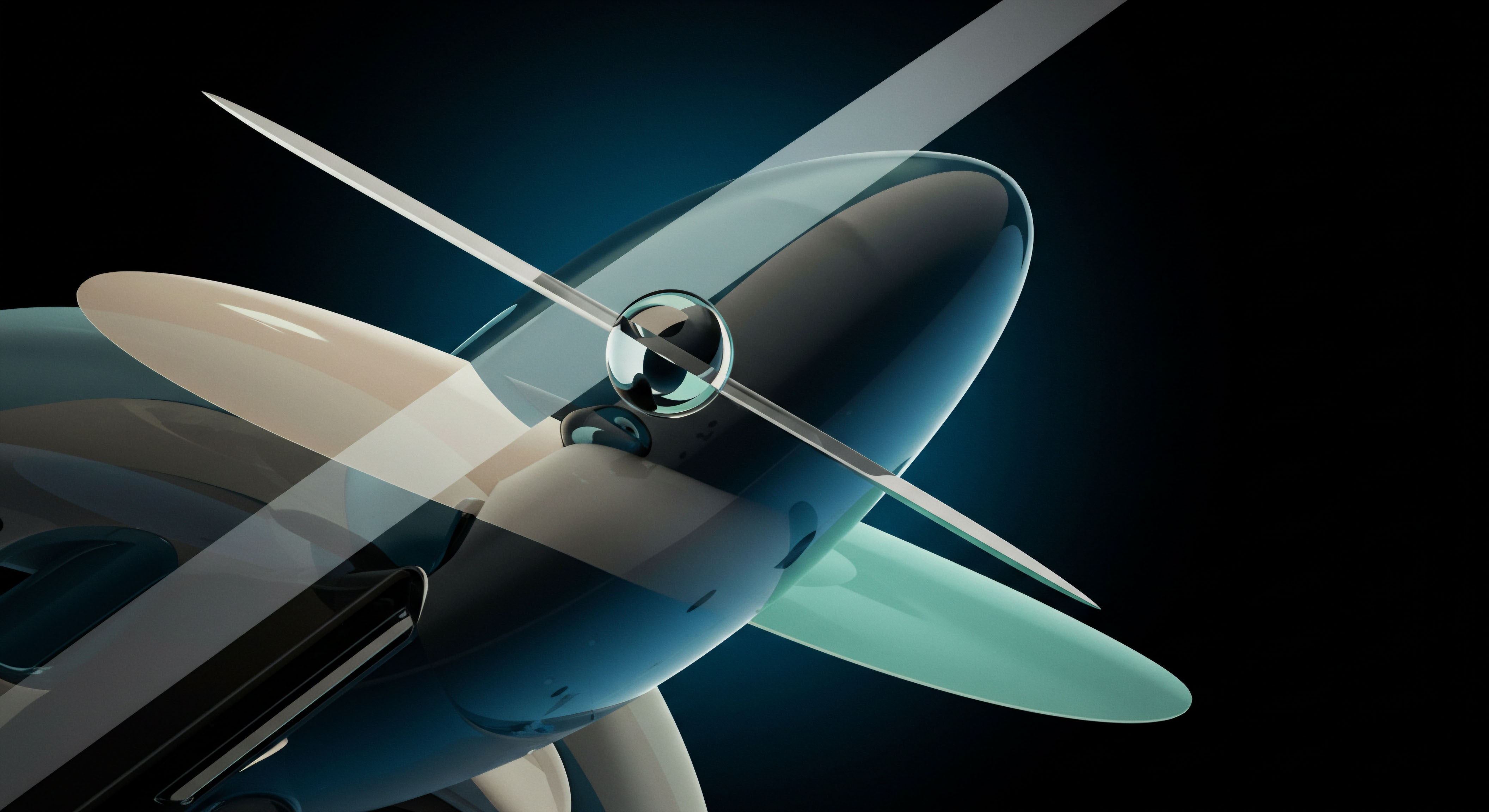

This delay is a function of the CPU’s sequential processing nature and the overhead of the operating system, which introduces non-deterministic jitter. An FPGA, or Field-Programmable Gate Array, fundamentally alters this paradigm by moving these critical validation tasks from software into configurable silicon. An FPGA is an integrated circuit that can be programmed in the field to perform specific, complex logical operations. This allows for the creation of a bespoke digital circuit perfectly tailored to the task of quote validation, executing checks in parallel at hardware speed. The result is a reduction in latency by orders of magnitude, from microseconds down to nanoseconds.

From Sequential Logic to Parallel Execution

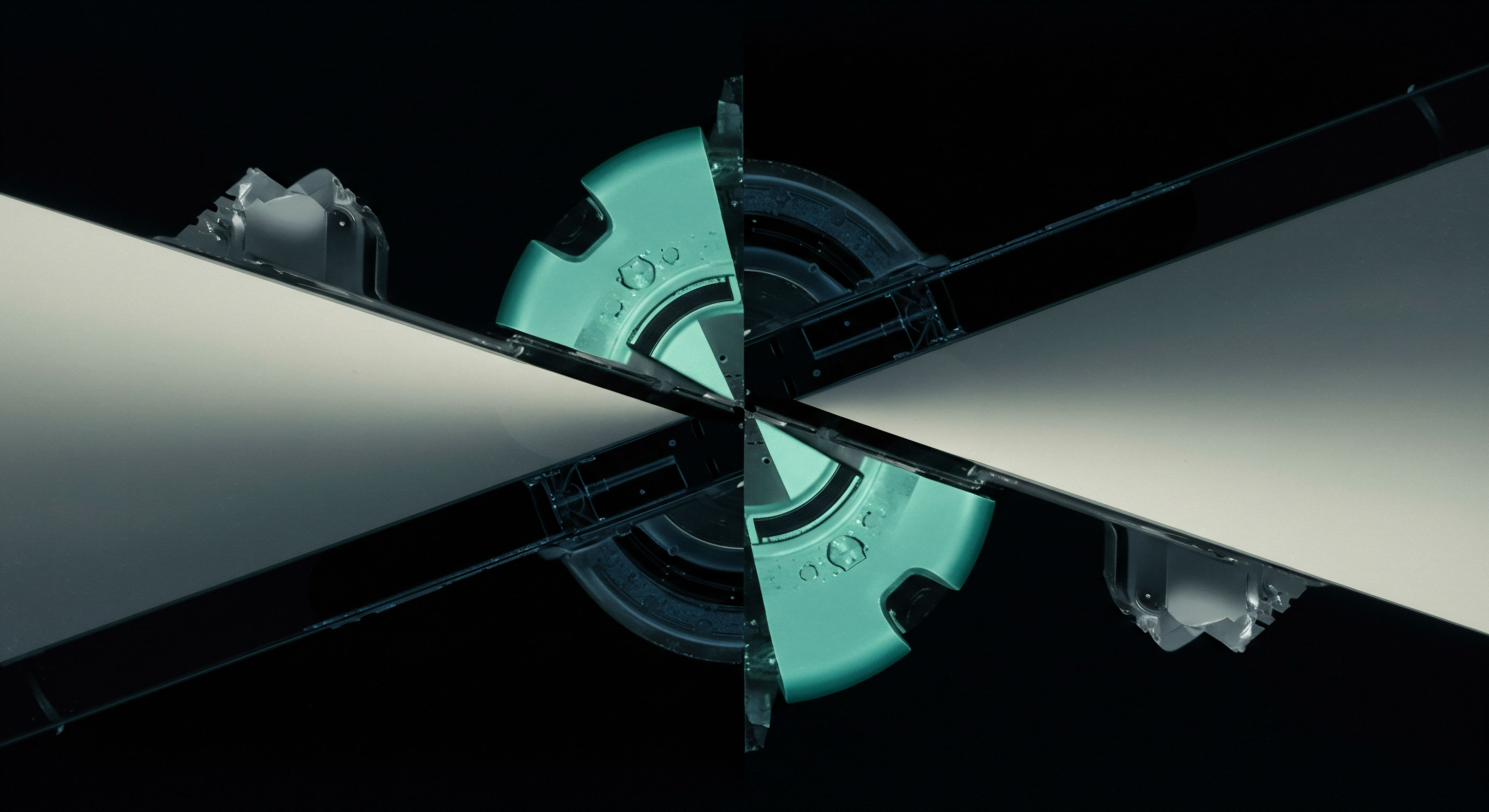

The core of an FPGA’s power lies in its inherent parallelism. A CPU processes instructions in a linear, sequential fashion, even with multiple cores. It must handle context switching, operating system interrupts, and other background tasks that create unpredictable delays. A quote validation system running on a CPU must check a series of conditions one by one ▴ Does the quote exceed a certain notional value?

Does it breach position limits? Does it comply with exchange rules? Each question is asked and answered in sequence. An FPGA, conversely, can be configured to ask all these questions simultaneously.

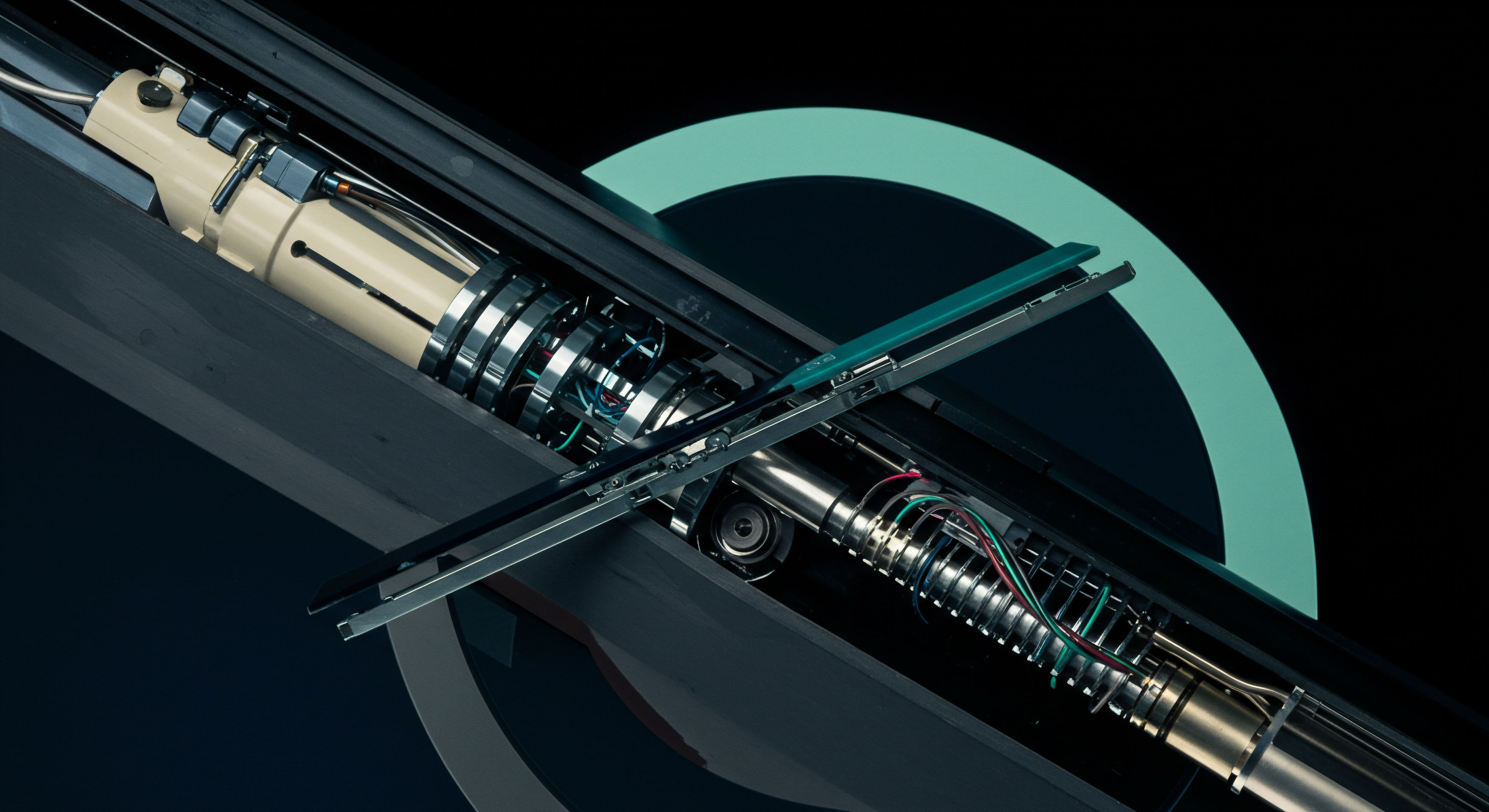

The logic gates are physically wired to perform these checks in parallel pipelines. As market data flows into the chip, it is instantly routed through thousands of dedicated logic blocks, each performing its specific validation task concurrently. This architectural difference is the primary driver of the dramatic latency reduction. It transforms the validation process from a sequential software queue into a parallel, deterministic hardware function.

FPGAs achieve ultra-low latency by transitioning quote validation from the unpredictable, sequential world of software to the deterministic, parallel environment of custom hardware logic.

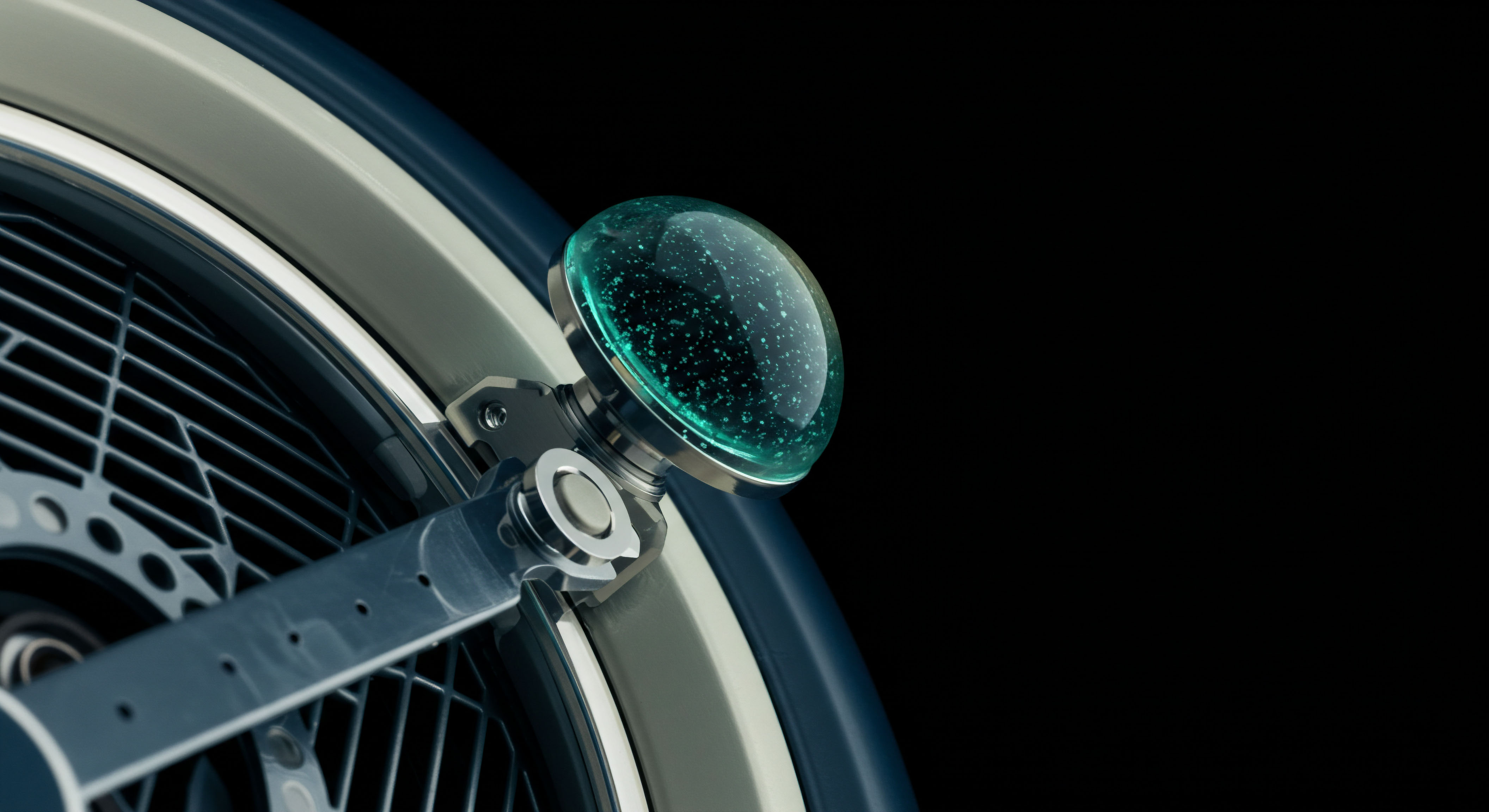

The Anatomy of a Quote Validation System

A quote validation system serves as a critical pre-trade risk and compliance gateway. Its primary function is to inspect every outbound quote or order to ensure it adheres to a predefined set of rules before it can reach the market. This process is essential for preventing costly errors and ensuring regulatory compliance.

The system is a non-negotiable component of any institutional trading infrastructure, safeguarding the firm from both financial and reputational damage. The checks performed are comprehensive and multi-layered, encompassing a range of parameters that must be verified in real-time.

- Fat-Finger Checks ▴ This is a basic but critical validation to prevent typographical errors. The system checks if the quote’s price or quantity is drastically outside of expected bounds, such as a price that is a certain percentage away from the current market or a quantity that is abnormally large.

- Position and Credit Limits ▴ The system verifies that the quote, if executed, would cause the firm’s overall position in the instrument to exceed established limits. It also checks against credit limits allocated to the specific trading desk or client.

- Regulatory Compliance ▴ The system enforces rules mandated by regulatory bodies. This can include checks for compliance with SEC Rule 15c3-5 in the U.S. which governs market access and risk management controls, or MiFID II in Europe.

- Instrument-Specific Rules ▴ The validation system ensures the quote conforms to the rules of the specific exchange or trading venue it is being sent to. This includes checks on tick size, lot size, and order type validity.

Executing these checks in software adds significant latency, creating a direct conflict between the need for robust risk management and the demand for high-performance execution. FPGAs resolve this conflict by embedding the rule-checking logic directly into the hardware, allowing for near-instantaneous validation without compromising on the rigor of the checks.

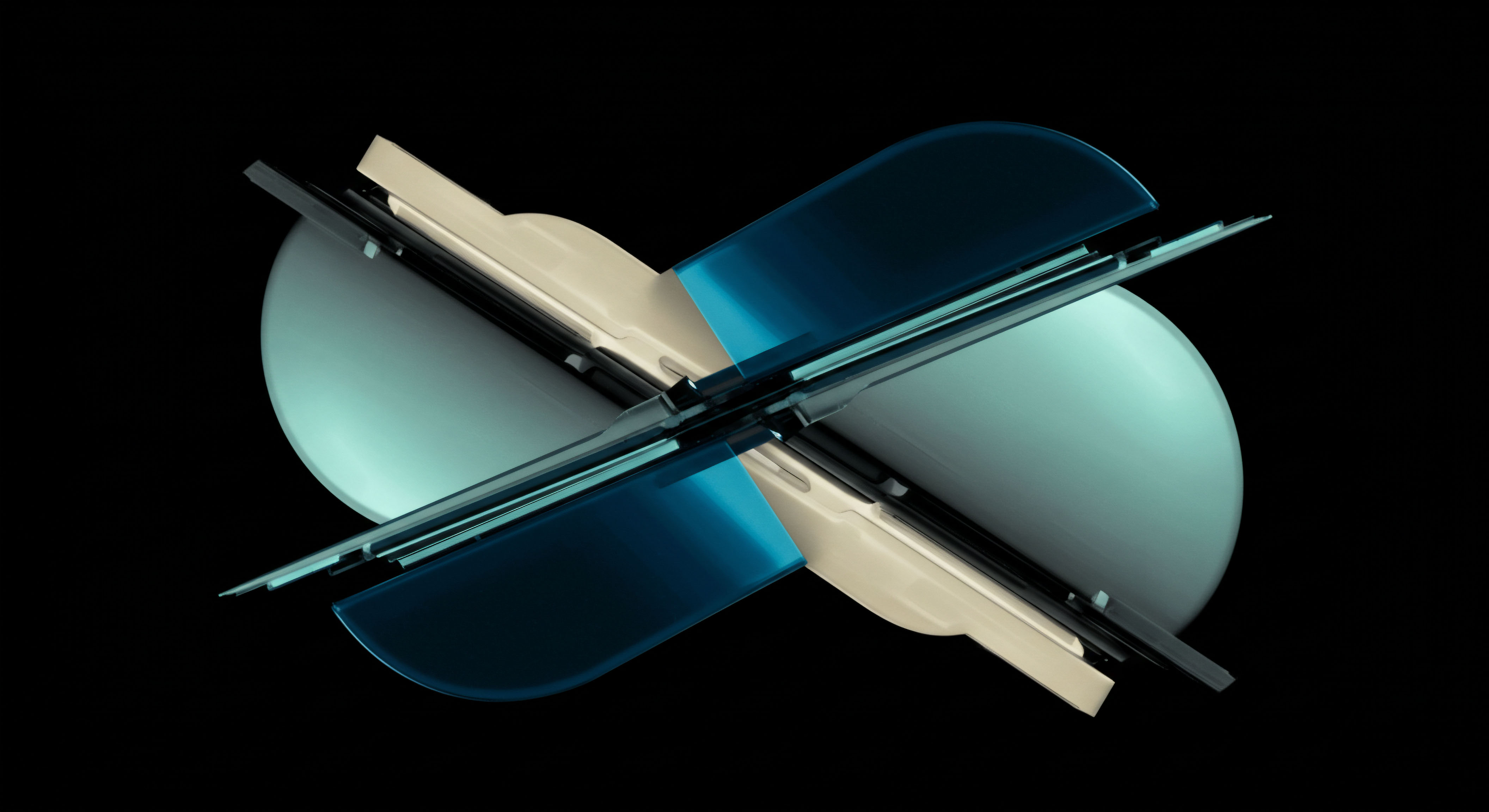

Strategy

The Strategic Imperative of Determinism

The strategic decision to employ FPGAs in quote validation systems is rooted in the pursuit of deterministic latency. In CPU-based systems, latency is variable and unpredictable. Factors like operating system scheduling, cache misses, and resource contention create a wide distribution of response times. For a high-frequency trading firm, this jitter is as detrimental as high average latency.

An FPGA-based system, by contrast, offers a predictable, repeatable processing time. Each quote traverses the same physical logic paths, resulting in a consistent, ultra-low latency. This determinism allows firms to build more reliable and aggressive trading strategies, knowing that their risk controls will operate within a precise time budget. The strategic advantage is twofold ▴ it allows the firm to be faster to market with its quotes, increasing the probability of favorable execution, and it provides a stable foundation upon which to build complex, latency-sensitive algorithms.

A Comparative Latency Analysis

The performance differential between CPU-based and FPGA-based quote validation is stark. While a highly optimized software solution might achieve latencies in the tens of microseconds, an FPGA can perform the same checks in hundreds of nanoseconds or less. This difference of two orders of magnitude is strategically significant in markets where price opportunities are fleeting. The following table provides an illustrative comparison of typical latency budgets for various validation tasks, highlighting the profound impact of moving these functions into hardware.

| Validation Task | Typical CPU-Based Latency (µs) | Typical FPGA-Based Latency (ns) | Order of Magnitude Improvement |

|---|---|---|---|

| Market Data Packet Ingestion & Parsing | 5 – 15 µs | 100 – 300 ns | ~50x |

| Fat-Finger & Notional Value Check | 2 – 5 µs | 50 – 100 ns | ~40x |

| Position Limit Verification | 10 – 25 µs | 200 – 500 ns | ~50x |

| Regulatory Compliance Check (e.g. SEC 15c3-5) | 8 – 20 µs | 150 – 400 ns | ~53x |

| Total End-to-End Latency | 25 – 65 µs | 500 – 1300 ns (0.5 – 1.3 µs) | ~50x |

Systemic Integration and Workflow Optimization

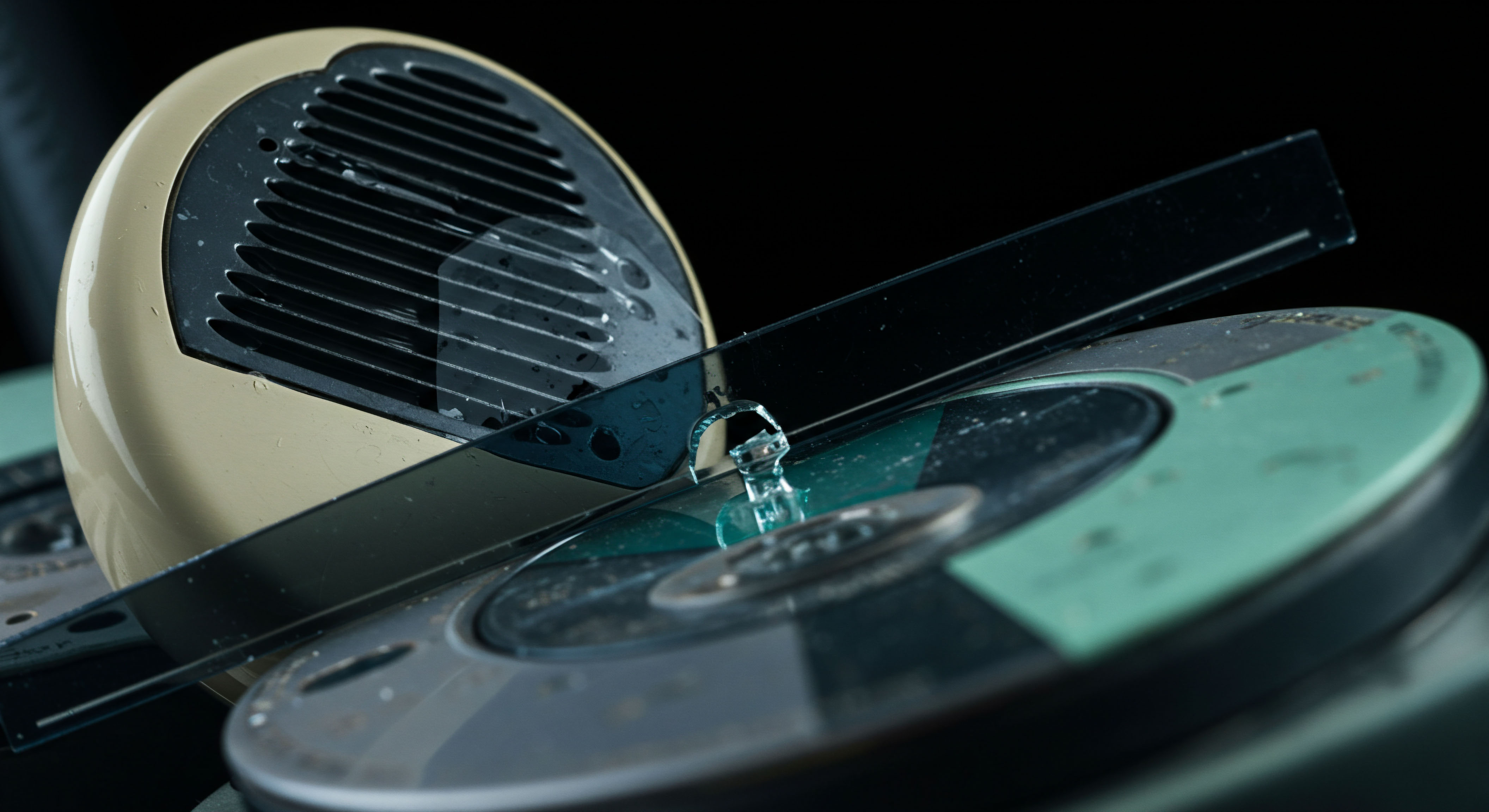

Integrating FPGAs into a trading system is a strategic architectural decision that extends beyond simple hardware acceleration. The FPGA becomes a central component of the tick-to-trade path, often residing on a Smart Network Interface Card (SmartNIC) that processes data directly from the network feed. This placement allows the FPGA to perform its validation functions before the data even reaches the host server’s CPU, a technique known as OS bypass.

This minimizes the latency introduced by the server’s operating system and network stack. The optimized workflow for a quote validation system leveraging an FPGA follows a clear, efficient path.

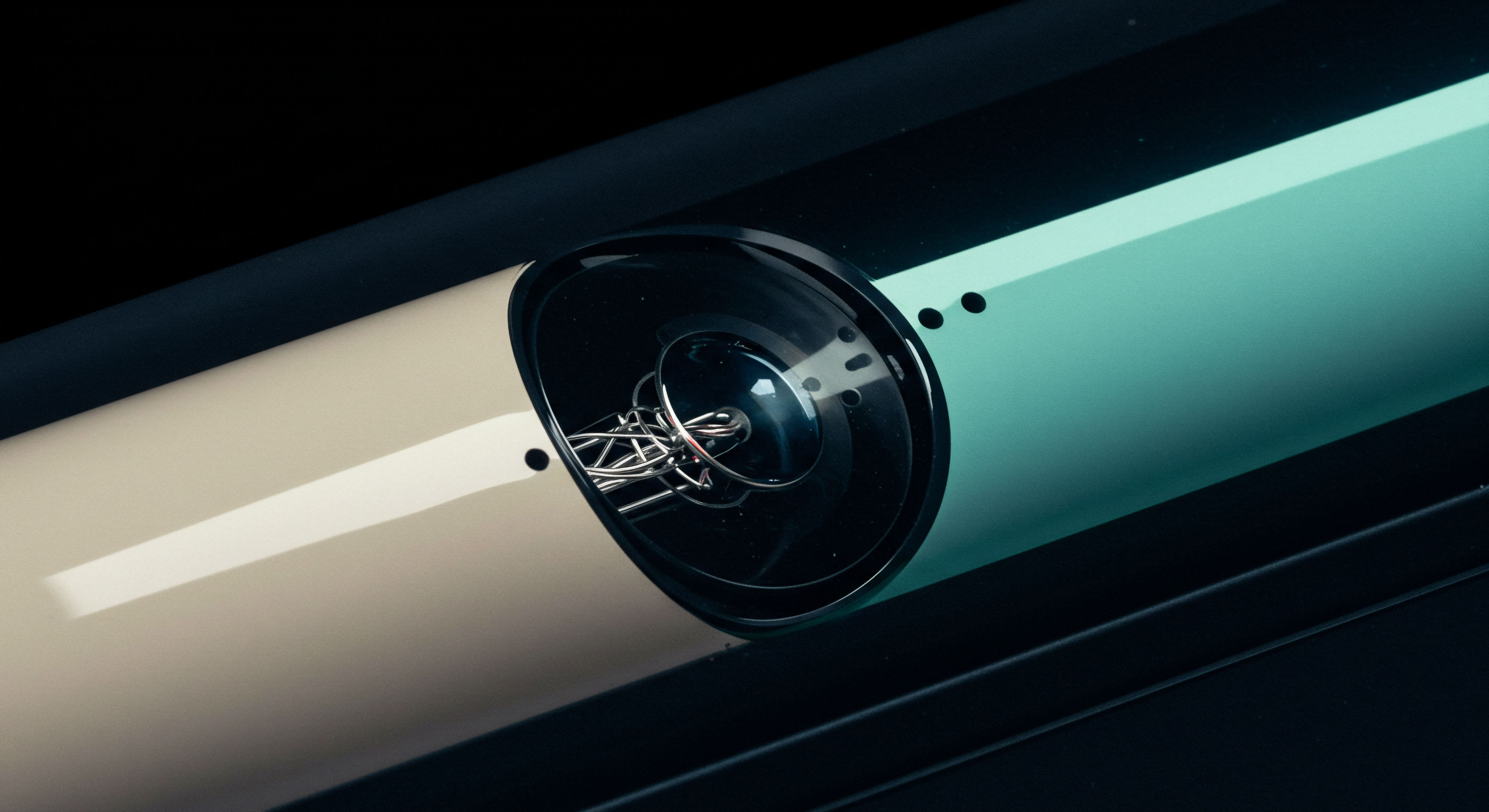

- Direct Market Data Ingestion ▴ The FPGA, via the SmartNIC, receives market data packets directly from the exchange network feed.

- Hardware-Based Parsing ▴ The FPGA’s dedicated logic immediately parses the packets, extracting the relevant fields (price, quantity, etc.) without involving the CPU.

- Parallel Validation Pipeline ▴ The extracted data is fed into the parallel risk-checking pipeline. All validation checks (position, price, compliance) are performed simultaneously.

- Decision and Forwarding ▴ If all checks pass, the FPGA can be programmed to forward the outbound order packet directly to the exchange network, again with minimal CPU involvement. If a check fails, the packet is dropped or flagged, and a rejection message is sent to the trading application.

- Logging and Auditing ▴ The FPGA logs all actions with high-precision timestamps, providing a detailed audit trail for compliance and analysis.

This streamlined workflow, enabled by the strategic placement and capabilities of the FPGA, ensures that the critical path for latency-sensitive orders is almost entirely contained within the hardware, providing a significant competitive advantage.

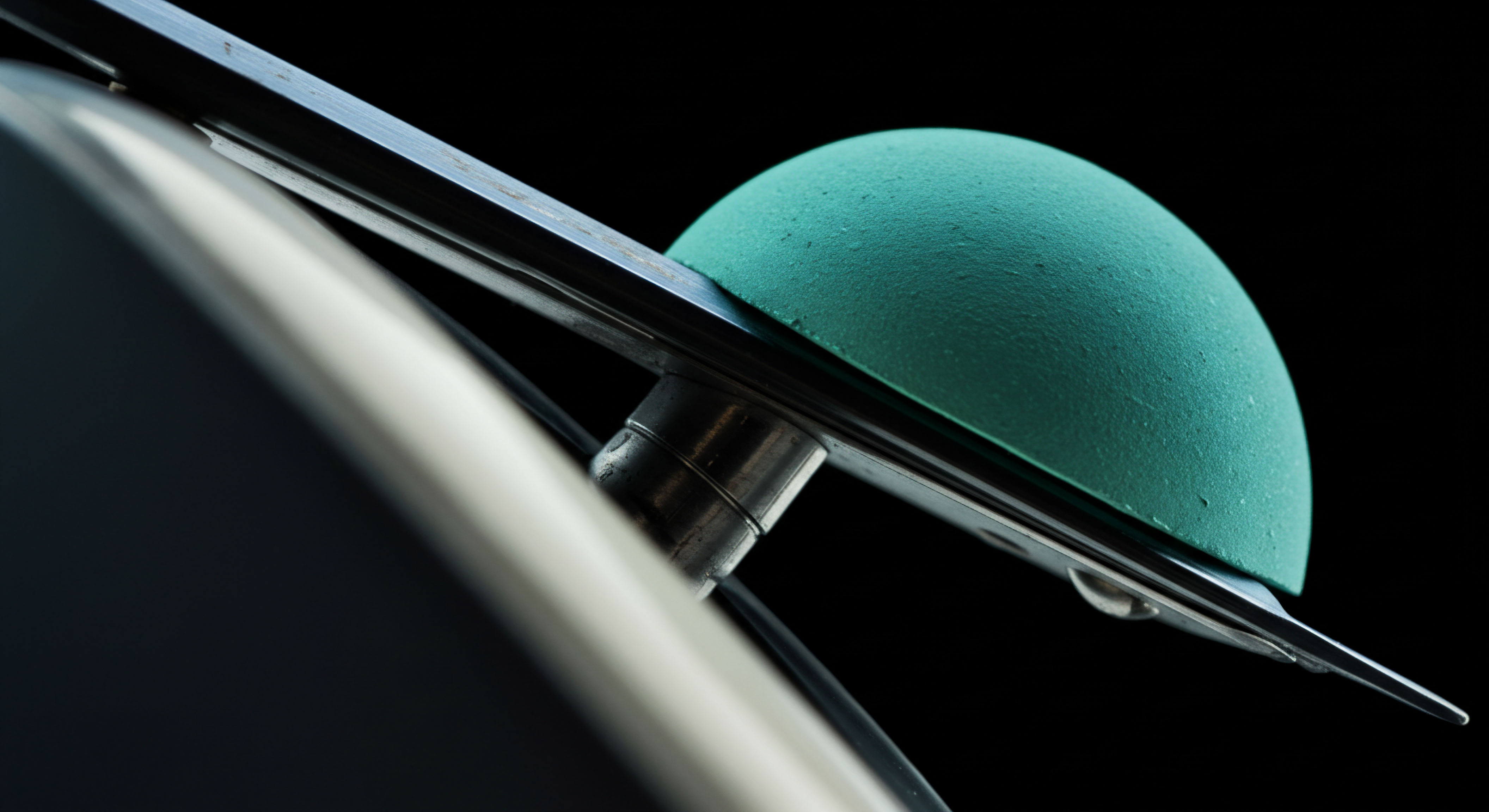

Execution

The Implementation Blueprint for Hardware Acceleration

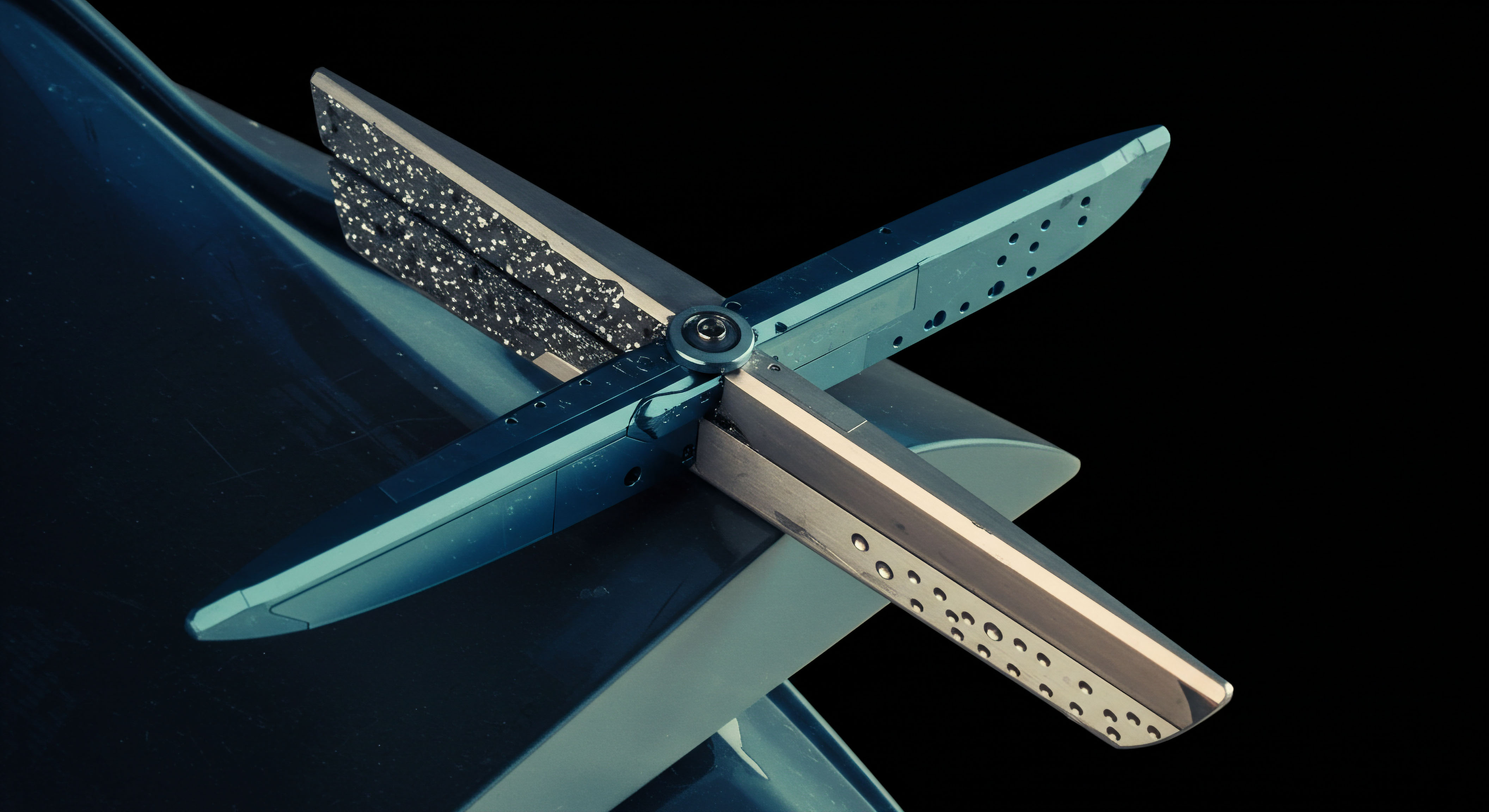

The execution of an FPGA-based quote validation system requires a specialized development process that differs significantly from traditional software engineering. The process involves designing digital circuits using a Hardware Description Language (HDL), such as Verilog or VHDL. These languages are used to describe the behavior of the electronic circuits that will be programmed onto the FPGA.

The development workflow is rigorous and methodical, focusing on creating a highly optimized and verifiable design. The goal is to translate the complex logic of pre-trade risk checks into a physical circuit layout that executes with maximum efficiency and determinism.

By embedding compliance and risk checks directly into the hardware fabric, FPGAs offer a deterministic solution to the latency challenges of modern trading.

The implementation involves several distinct phases, from high-level design to physical deployment. Each step requires a deep understanding of both the financial logic and the underlying hardware architecture. This convergence of expertise is what allows for the creation of a system that is both functionally correct and performant at the nanosecond level. The process ensures that the final design is not only fast but also robust and reliable, capable of operating in a high-stakes production trading environment.

- High-Level Synthesis (HLS) ▴ This modern approach allows developers to write algorithms in higher-level languages like C++ and then synthesize them into HDL. HLS can accelerate the development cycle, making FPGA technology more accessible to firms without large, dedicated hardware engineering teams.

- Simulation and Verification ▴ Before programming the FPGA, the HDL code is extensively simulated to verify its logical correctness. This is a critical step to ensure that the risk checks behave as expected under all possible market conditions. Testbenches are created to bombard the design with a wide range of valid and invalid scenarios.

- Synthesis and Place-and-Route ▴ The verified HDL code is then synthesized, a process that translates the code into a netlist, which is a description of the logic gates and their interconnections. The place-and-route tool then takes this netlist and maps it onto the physical resources of the specific FPGA chip, optimizing for timing and performance.

- Hardware Deployment and Testing ▴ Once the design is synthesized and placed, the resulting bitstream is loaded onto the FPGA. The hardware is then tested in a lab environment, often using network traffic replay systems to validate its performance with real-world data before it is deployed into the live trading environment.

A Granular Analysis of a Pre-Trade Risk Check

To fully appreciate the efficiency of an FPGA, one must examine the execution of a risk check at the nanosecond level. Each step of the process, from the moment a network packet arrives at the NIC to the moment a decision is made, can be precisely measured. The following table breaks down the latency budget for a comprehensive pre-trade risk check performed entirely within an FPGA, demonstrating the power of hardware-level parallelism and pipelining.

| Micro-Task | Description | Typical Latency (ns) |

|---|---|---|

| Packet Reception (PHY Layer) | The physical receipt of the first byte of the incoming network packet. | 5 – 10 ns |

| Header Parsing (MAC/IP/TCP) | Parallel extraction of network and transport layer headers. | 15 – 30 ns |

| FIX Message Deserialization | Extraction and decoding of financial protocol message fields (e.g. symbol, price, quantity). | 40 – 80 ns |

| Symbol Lookup | Matching the instrument symbol to internal risk parameters stored in on-chip memory (BRAM). | 20 – 40 ns |

| Notional Value Calculation | Concurrent multiplication of price and quantity. | 10 – 20 ns |

| Parallel Limit Checks | Simultaneous comparison against fat-finger, notional value, and position limits. | 15 – 30 ns |

| Decision Logic | Aggregation of all check results to produce a final approve/reject decision. | 5 – 10 ns |

| Total Pipeline Latency | End-to-end time for a single quote to traverse the validation pipeline. | 110 – 220 ns |

Quantitative Impact on Execution Quality

The reduction in latency afforded by FPGAs has a direct and quantifiable impact on a firm’s profitability. In competitive, latency-sensitive markets, even a microsecond advantage can significantly improve the probability of capturing a favorable price. This can be modeled by considering the relationship between latency, price volatility, and fill probability. A lower latency system can react to new market information faster, placing orders before the price moves adversely.

This translates to reduced slippage, which is the difference between the expected price of a trade and the price at which the trade is actually executed. The cumulative effect of these small improvements over millions of trades can be substantial.

References

- Choudhary, Pankaj, et al. “A survey on field programmable gate array ▴ an embedded system.” International Journal of Computer Applications 975 ▴ 8887, 2012.

- Coffey, Todd. “High-frequency trading.” Handbook of quantitative finance and risk management. Springer, Boston, MA, 2010. 1471-1479.

- Harris, Larry. Trading and exchanges ▴ Market microstructure for practitioners. Oxford University Press, 2003.

- Hau, Harald. “The role of high-frequency traders in electronic markets.” Financial stability, monetary policy and central banking. 2011. 199-209.

- Hasbrouck, Joel, and Gideon Saar. “Low-latency trading.” Journal of Financial Markets 16.4 (2013) ▴ 646-679.

- Lok, H. H. “FPGA implementation of a high speed low latency FIX engine.” (2010).

- Brogaard, Jonathan, Terrence Hendershott, and Ryan Riordan. “High-frequency trading and price discovery.” The Review of Financial Studies 27.8 (2014) ▴ 2267-2306.

Reflection

The Systemic Commitment to Velocity

Adopting FPGAs for quote validation is a declaration of a firm’s commitment to operating at the fundamental speed of the market. It reframes latency reduction from an incremental IT upgrade to a core strategic principle. The implementation of such a system forces a re-evaluation of the entire trading architecture, compelling a holistic view of the data path from the exchange to the execution logic. This process often reveals secondary bottlenecks and inefficiencies, leading to a more streamlined and robust operational framework.

The knowledge gained through this process becomes a durable asset, informing future architectural decisions and fostering a culture of engineering excellence. The ultimate outcome is a trading system that is not just faster, but more coherent, deterministic, and resilient. It represents a foundational investment in the capacity to compete effectively in the evolving landscape of electronic markets.

Glossary

Quote Validation

Fpga

Quote Validation System

Validation System

Pre-Trade Risk

High-Frequency Trading

Deterministic Latency

Hardware Acceleration

Tick-To-Trade

Smartnic

Verilog