Concept

The Physicality of a Digital Signal

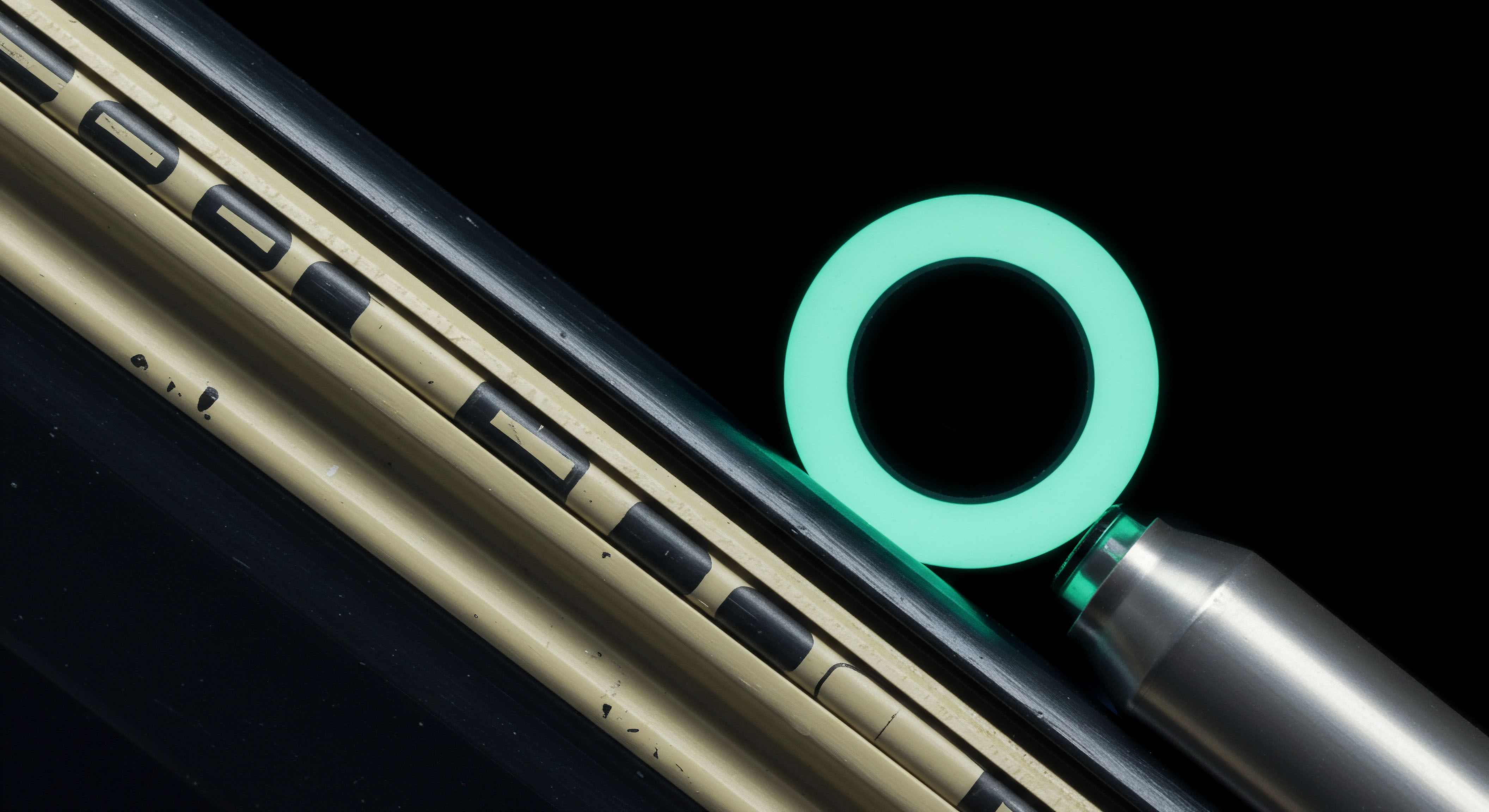

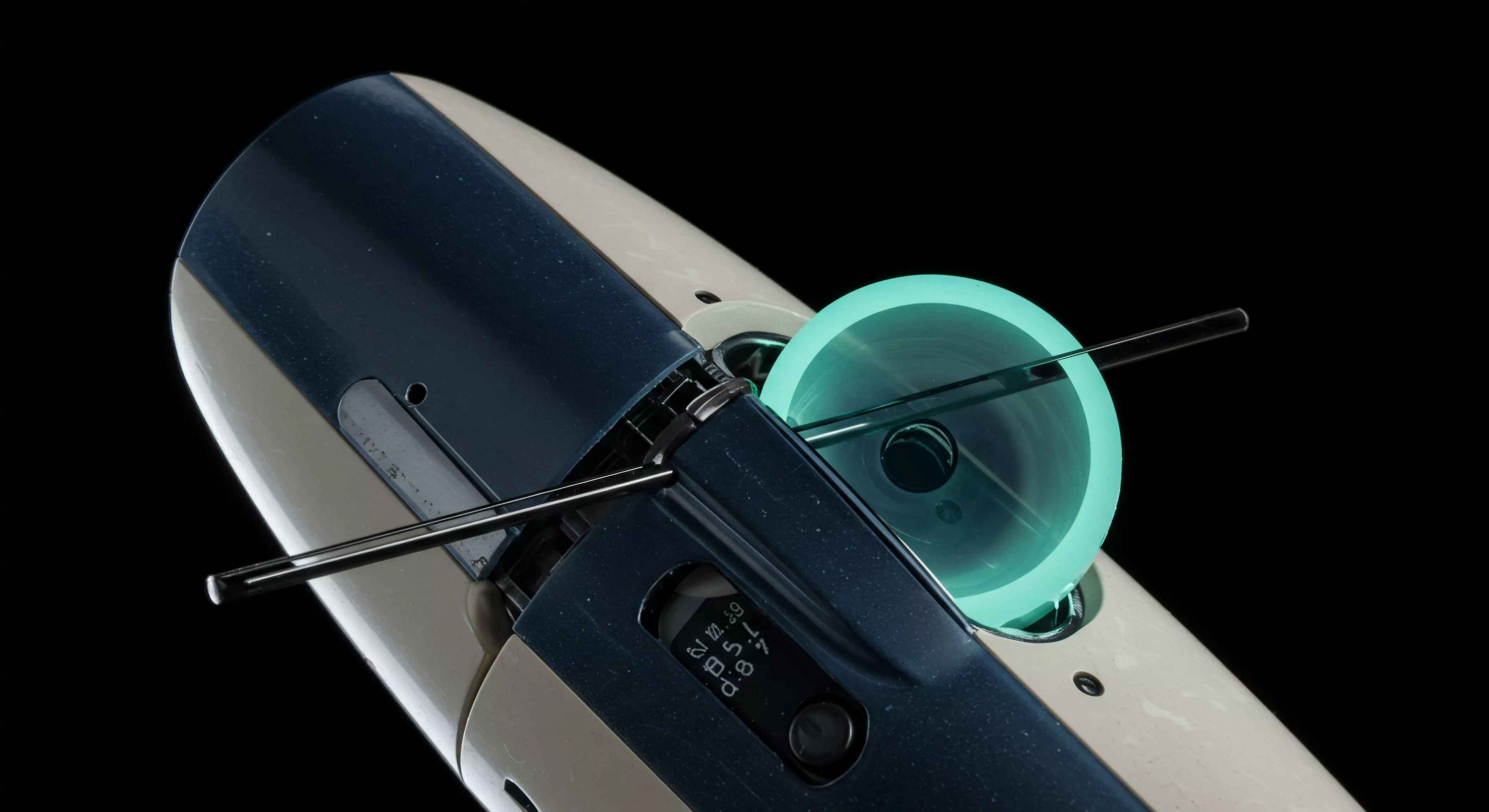

In the world of institutional trading, a quote is a physical reality before it is a piece of financial information. It is a pulse of light in a fiber optic cable, a packet of electrons traversing a silicon chip. The process of validating this quote ▴ ensuring its integrity, confirming its source, and checking it against a litany of risk parameters ▴ is a physical process constrained by the laws of physics. The speed of light in fiber dictates the absolute minimum time for data to travel from an exchange to a trading venue’s systems.

From that point forward, every nanosecond of delay is a function of the architecture chosen to interpret that signal. Real-time quote validation is the system’s first line of defense and its first opportunity for action. It is the digital immune system of a trading apparatus, responsible for filtering corrupted, malicious, or erroneous data packets before they can trigger a catastrophic trading decision. The speed at which this validation occurs directly determines the quality of the market view and the ability to act on fleeting opportunities. A slower validation process means the trading logic is operating on an older, potentially irrelevant version of reality, increasing risk and conceding advantage to faster participants.

From Serial Instruction to Parallel Execution

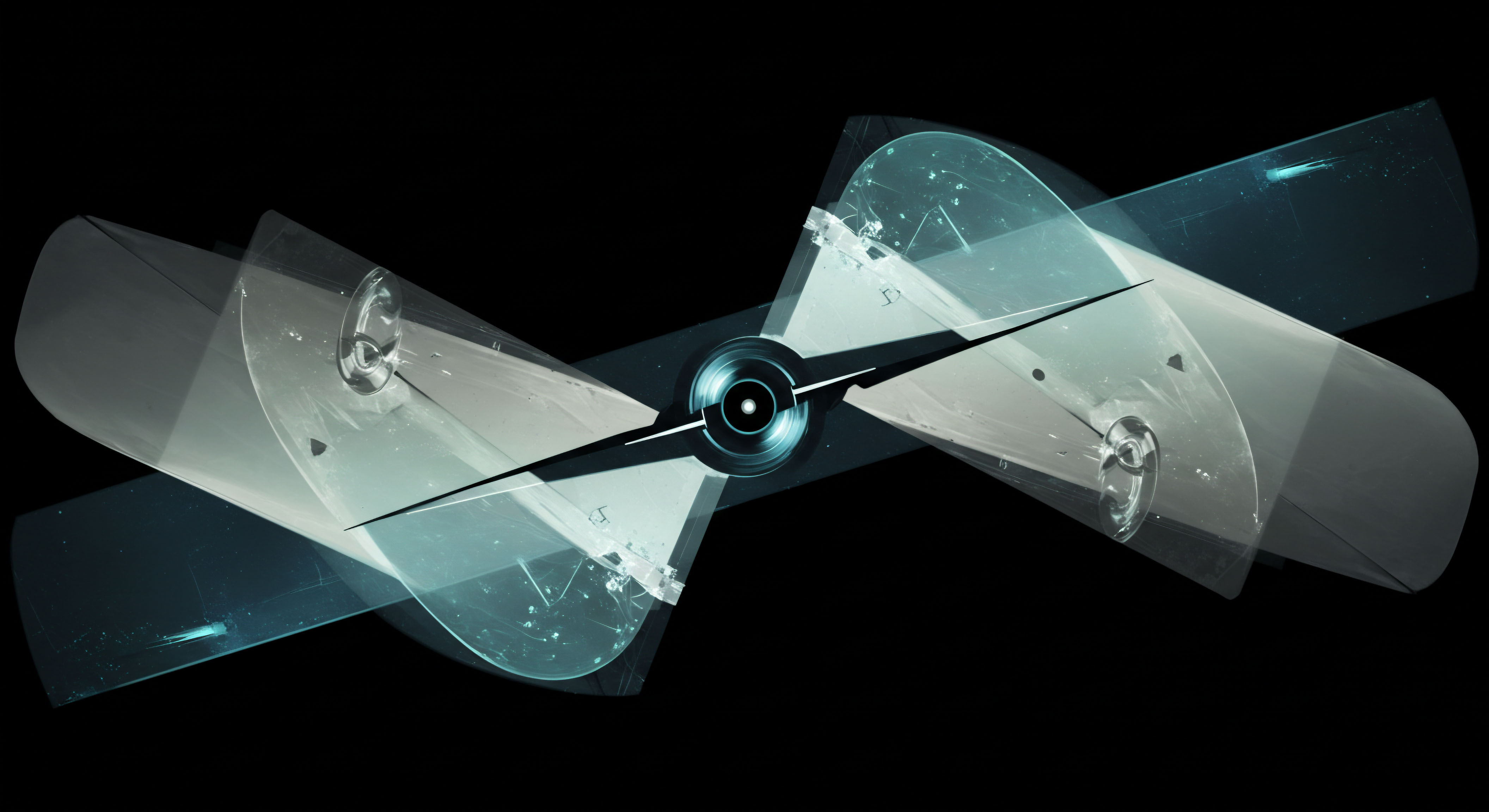

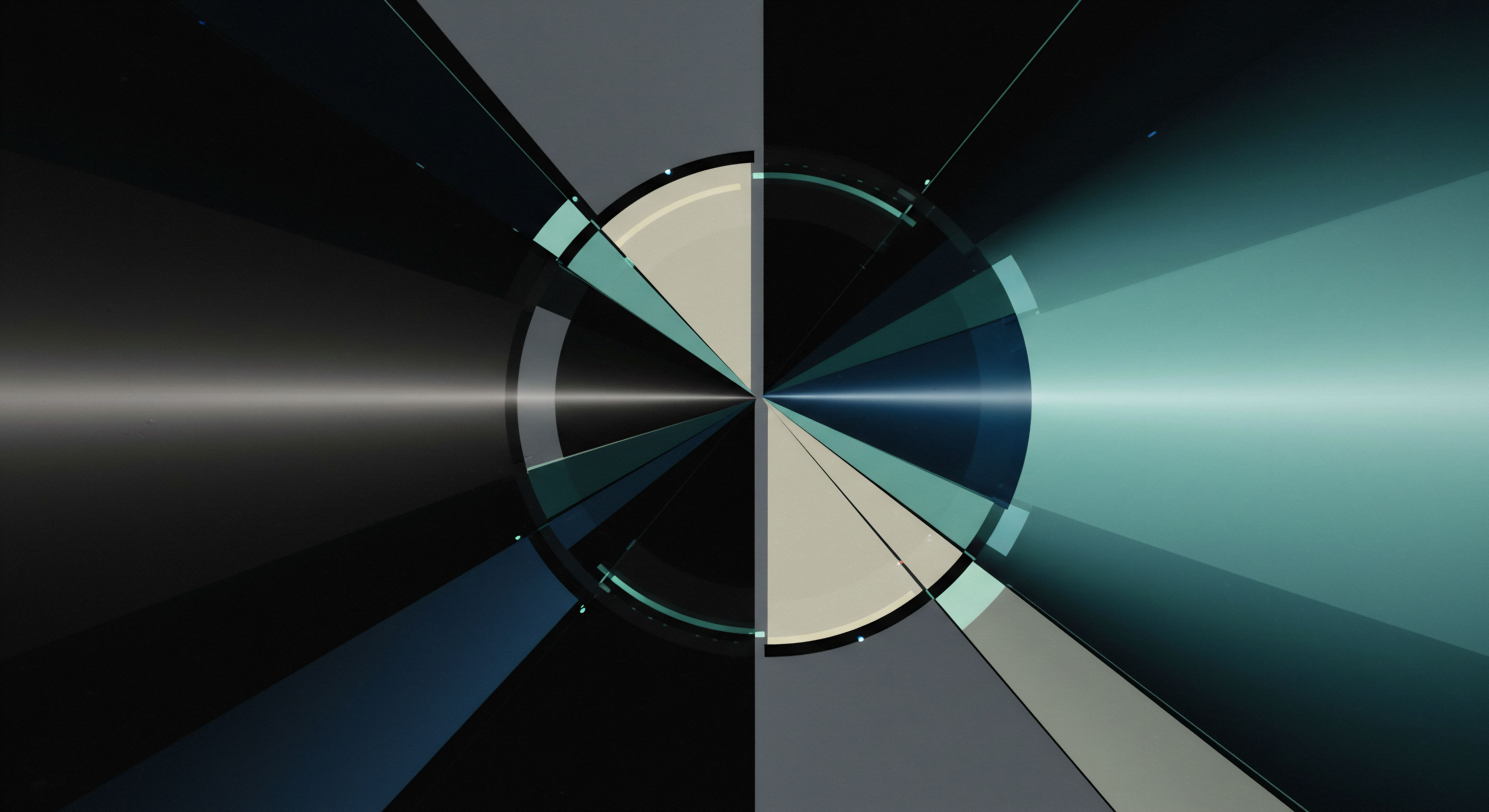

Traditional quote validation operates on a central processing unit (CPU), a marvel of engineering designed for general-purpose, sequential tasks. A CPU processes instructions one after another, an approach that is highly flexible but introduces inherent latency when dealing with the massive, parallel firehose of modern market data. Each validation check ▴ for format, price bands, source, and consistency ▴ must wait its turn in a queue. Hardware acceleration technologies, specifically Field-Programmable Gate Arrays (FPGAs), fundamentally alter this paradigm.

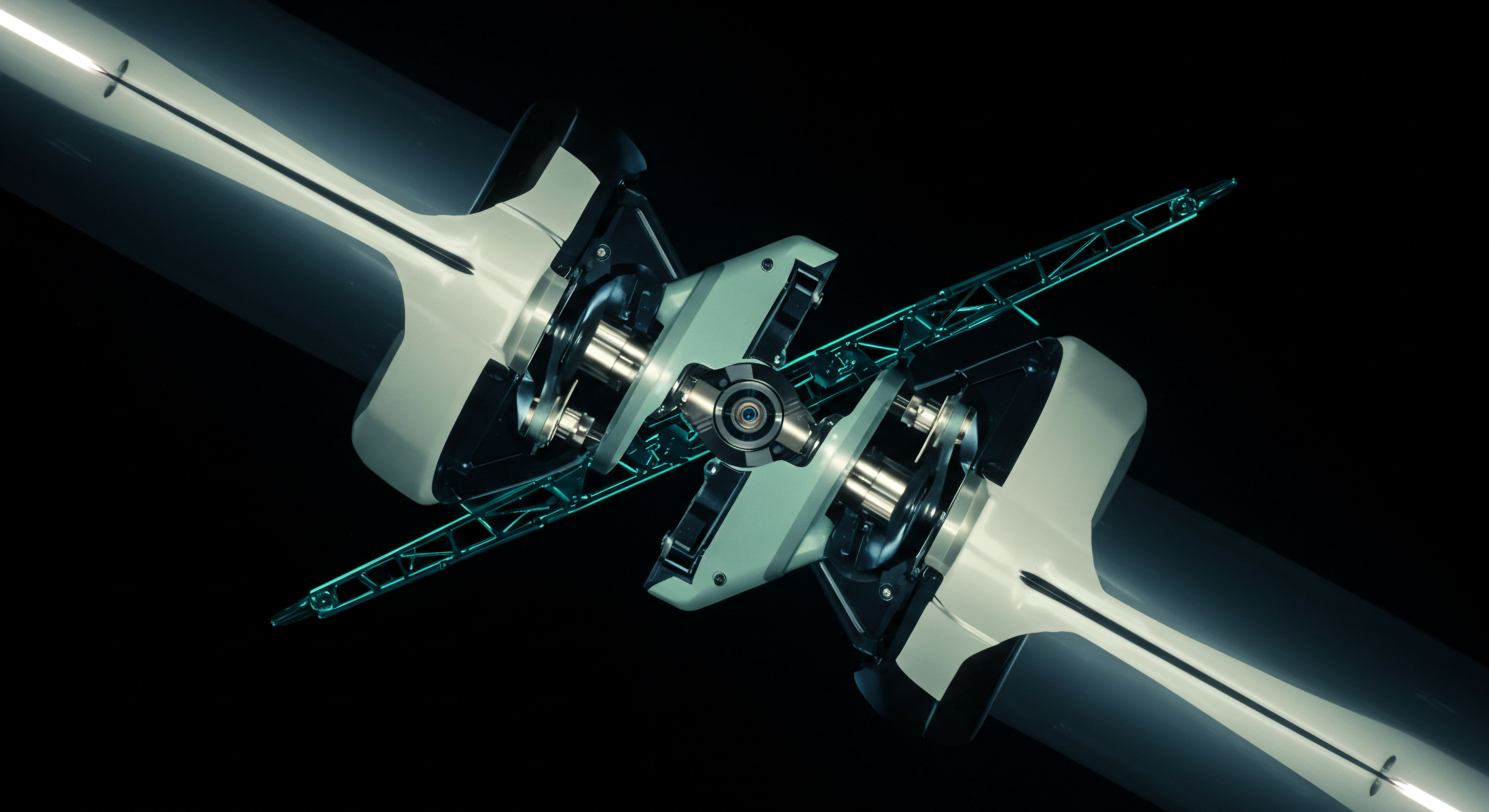

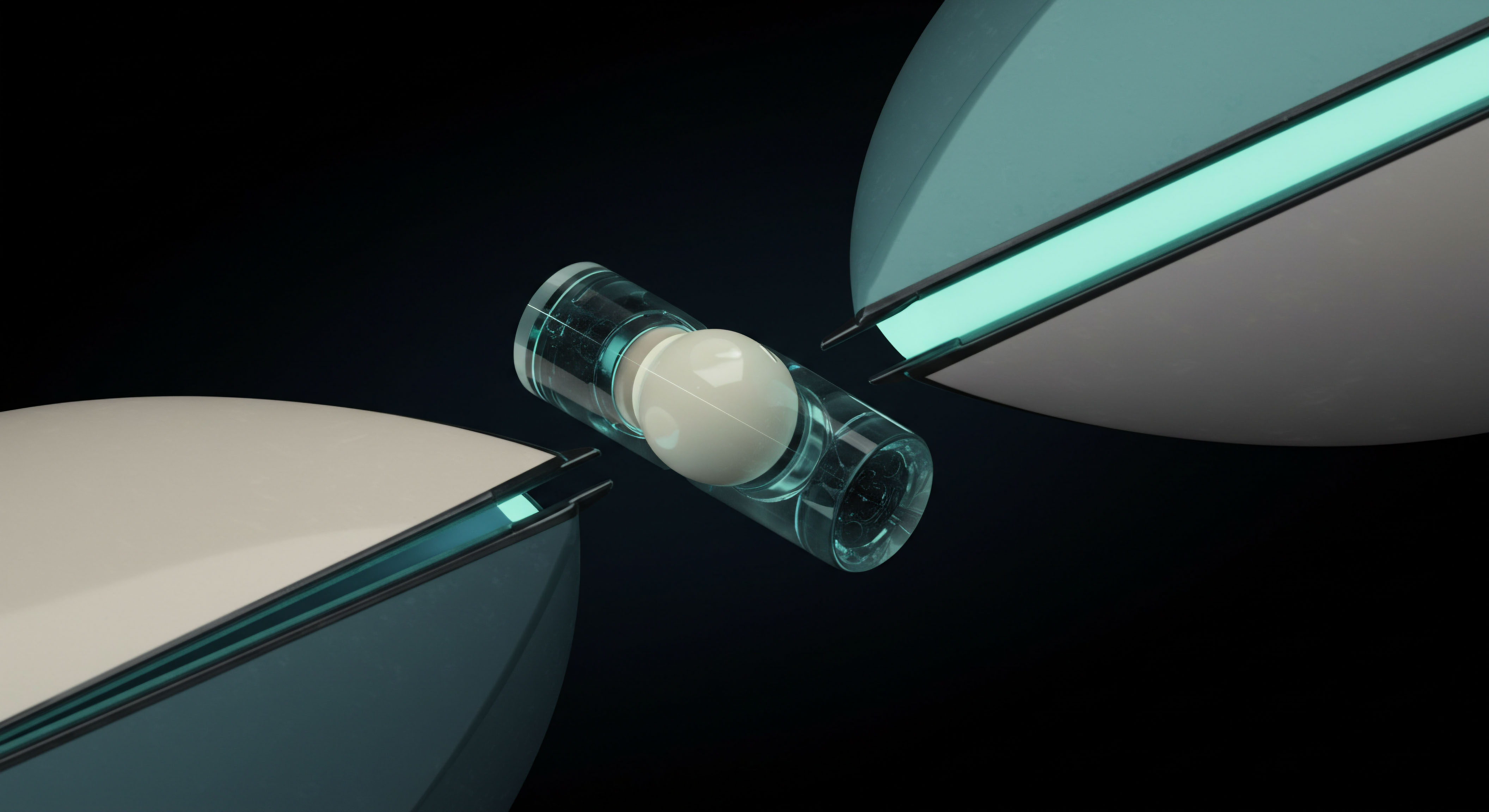

An FPGA is a silicon chip that can be configured at the hardware level to perform a specific task. Instead of executing a sequence of software instructions, the validation logic is etched directly into the chip’s circuitry. This allows for a massively parallel approach where multiple validation checks occur simultaneously. The arrival of a data packet triggers a cascade of concurrent operations, shrinking the validation timeline from microseconds to nanoseconds. This is the core architectural divergence ▴ moving from a flexible but sequential process to a specialized, parallel one.

Hardware acceleration transforms quote validation from a sequential software task into a parallel, deterministic hardware function, dramatically reducing latency.

Determinism as a Strategic Asset

A critical, often misunderstood, aspect of hardware acceleration’s influence is the concept of determinism. In a software-based system running on a general-purpose operating system, the time taken to process a quote can vary based on other system activities ▴ a phenomenon known as jitter. This unpredictability is a source of risk. An FPGA-based validation system, by contrast, is deterministic.

Because the logic is baked into the hardware and isolated from other tasks, the time it takes to validate a quote is constant and predictable, regardless of market data volume or other system loads. This consistency is a profound strategic advantage. It allows for more precise calibration of trading algorithms and risk models, knowing that the latency of the validation layer is a fixed variable. This transforms the validation process from a potential source of unpredictable delays into a reliable, foundational component of the entire trading infrastructure, enabling firms to build more sophisticated and aggressive strategies on a bedrock of predictable performance.

Strategy

Choosing the Engine of Acceleration

The strategic decision to implement hardware acceleration is followed by a critical choice of technology. The primary contenders are CPUs, Graphics Processing Units (GPUs), and FPGAs, each presenting a distinct profile of performance, flexibility, and cost. A CPU offers the highest flexibility and lowest development barrier, but its sequential processing nature creates a latency floor that is unacceptable for many high-frequency strategies. GPUs, with their thousands of cores, excel at parallelizing a single instruction across massive datasets, making them powerful for certain types of quantitative analysis but less suited for the bespoke, multi-step logic of quote validation.

FPGAs represent the pinnacle of low-latency performance. They provide the ability to create custom digital circuits tailored to the exact steps of the validation process, achieving near-zero-latency execution of these tasks. The trade-off is higher development complexity and cost. The strategic choice depends on the firm’s latency sensitivity, trading strategy, and engineering resources.

A Comparative Framework for Acceleration Technologies

Selecting the appropriate hardware is a matter of aligning technological capabilities with specific strategic objectives. The table below outlines the key operational characteristics of each technology in the context of real-time quote validation.

| Metric | CPU (Central Processing Unit) | GPU (Graphics Processing Unit) | FPGA (Field-Programmable Gate Array) |

|---|---|---|---|

| Processing Model | Sequential (Serial) | Massively Parallel (SIMD) | Massively Parallel (Custom Logic) |

| Typical Latency | Microseconds (µs) | Tens of Microseconds (µs) | Nanoseconds (ns) |

| Determinism | Low (High Jitter) | Medium | High (Very Low Jitter) |

| Flexibility | Very High | Medium | Low to Medium |

| Development Cost | Low | Medium | High |

| Power Efficiency | Medium | Low | High |

| Optimal Use Case | General trading logic, less latency-sensitive strategies | Complex calculations on large data sets (e.g. options pricing) | Ultra-low latency tasks ▴ data feed handling, quote validation, pre-trade risk checks |

System Integration the Offload Model

A common and effective strategy for leveraging hardware acceleration is the “offload model.” In this architecture, the FPGA is not intended to run the entire trading strategy. Instead, it is deployed as a specialized co-processor. The raw market data feed, arriving over Ethernet, is routed directly to the FPGA. The FPGA performs the initial, latency-critical tasks ▴ decoding the network packets (UDP/TCP), parsing the market data protocol (like FAST or FIX), and executing the entire quote validation sequence.

Once a quote is validated and deemed safe, it is passed over a high-speed PCIe bus to the main server’s CPU. The CPU is then free to perform the higher-level, more complex tasks it excels at, such as strategy decision-making, position management, and historical data analysis. This hybrid approach combines the strengths of both technologies ▴ the FPGA handles the speed-sensitive, repetitive tasks at the wire level, while the CPU provides the flexibility to adapt and evolve complex trading logic. This creates a system that is both incredibly fast and strategically agile.

The offload model uses FPGAs for wire-level data processing and validation, freeing CPUs for complex, higher-level trading strategy execution.

The Impact on Market Microstructure Interaction

The adoption of hardware acceleration for quote validation has a tangible impact on how a firm interacts with the market’s microstructure. With validation latencies reduced to nanoseconds, a trading system can maintain a more accurate and up-to-date view of the order book. This enables a class of strategies that are simply impossible with slower, software-based systems. These include:

- Liquidity Detection ▴ Identifying fleeting liquidity posted on an exchange and reacting before it is consumed by competitors.

- Statistical Arbitrage ▴ Capitalizing on minute, short-lived price discrepancies between correlated instruments across different venues.

- Market Making ▴ Providing liquidity with tighter spreads and faster quote updates, reducing adverse selection risk because the system can cancel or update quotes more quickly in response to market movements.

By compressing the validation phase of the trade lifecycle, hardware acceleration allows a firm to move its decision point closer to the “metal,” reacting to market events with deterministic, predictable speed. This is a fundamental shift in capability, moving from merely participating in the market to actively shaping and reacting to its finest-grained movements.

Execution

The Anatomy of a Hardware-Accelerated Validation Pipeline

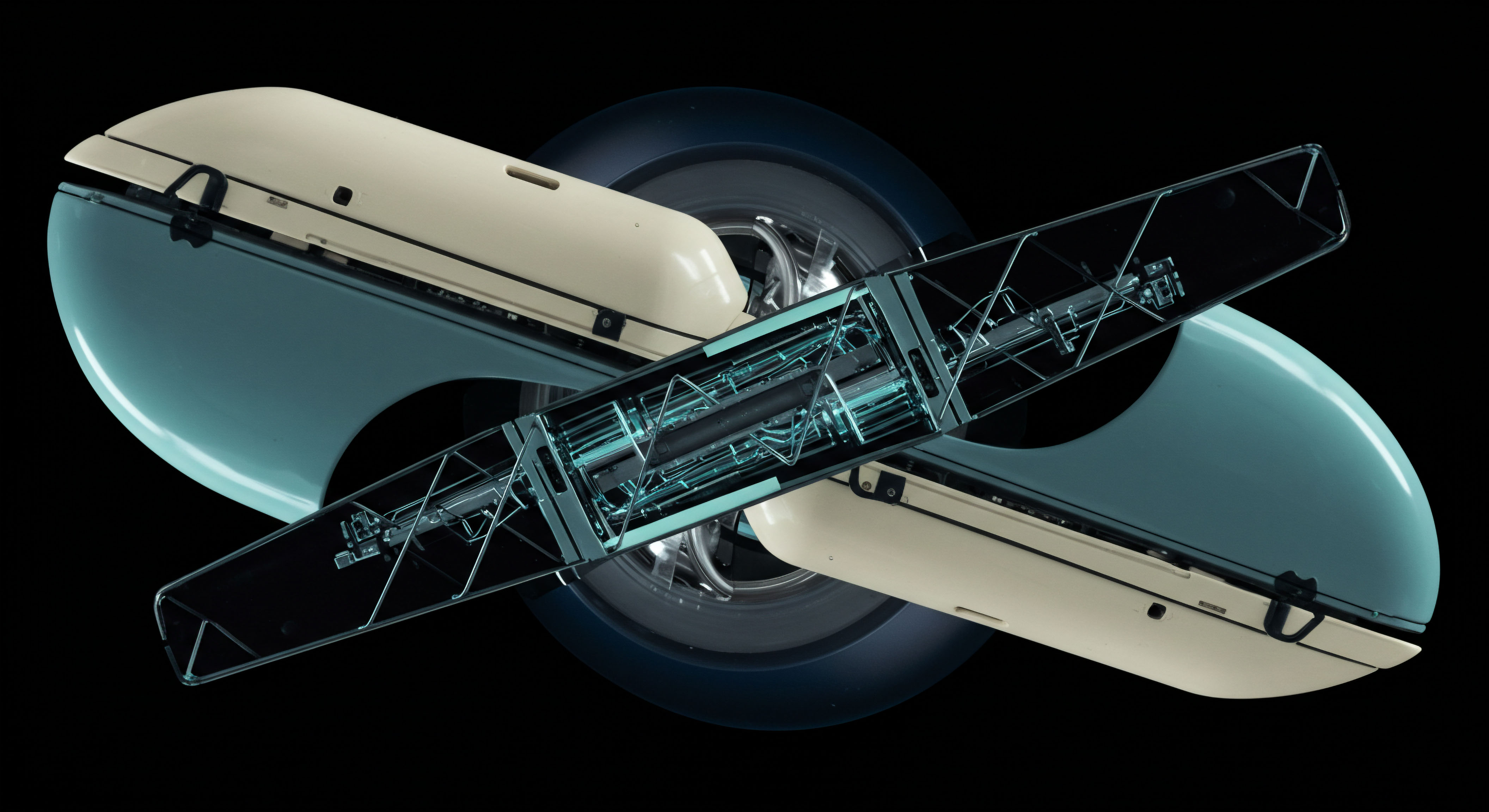

Executing quote validation on an FPGA involves designing a digital logic circuit that mirrors the necessary procedural checks. This circuit is often structured as a pipeline, where a data packet flows through a series of dedicated processing stages. Each stage operates in parallel and performs a specific validation task.

This architecture ensures maximum throughput and minimal latency, as a new packet can enter the pipeline at every clock cycle without waiting for the previous packet to be fully processed. The entire process, from photon to validated data, is a meticulously engineered sequence designed to eliminate any source of delay.

A Granular View of the Validation Stages

The following table breaks down the typical stages of an FPGA-based quote validation pipeline, providing hypothetical but realistic latency figures for each operation. These figures illustrate the nanosecond-level performance achievable when logic is implemented directly in hardware.

| Stage | Description | Typical Latency (Nanoseconds) |

|---|---|---|

| 1. Packet Ingress | Physical layer reception of the Ethernet frame from the fiber optic network. | 5 – 10 ns |

| 2. UDP/IP Stack Decode | Hardware-based decoding of the Ethernet, IP, and UDP headers to extract the market data payload. | 20 – 40 ns |

| 3. Protocol Parsing (FAST/FIX) | Parsing the specific exchange protocol to identify message type, symbol, price, and size fields. | 50 – 150 ns |

| 4. Symbol Lookup | Matching the incoming instrument symbol against an on-chip list of tradable securities. | 10 – 20 ns |

| 5. Price Band Validation | Checking if the quote’s price falls within a pre-defined, acceptable range to filter out erroneous data. | 5 – 10 ns |

| 6. Stale Quote Check | Verifying the timestamp of the quote against a high-precision clock to discard delayed data. | 5 – 10 ns |

| 7. Pre-Trade Risk Checks | Applying fundamental, mandated risk checks (e.g. fat-finger errors, max order size) directly in hardware. | 15 – 30 ns |

| 8. Data Egress to CPU | Passing the validated, parsed data over the PCIe bus to the host server for strategy processing. | 40 – 80 ns |

| Total Pipeline Latency | Cumulative time from network wire to CPU memory. | ~150 – 350 ns |

Operationalizing the Validation Logic

The process of implementing and managing a hardware-accelerated validation system requires a specialized workflow that combines hardware engineering with quantitative finance. The operational steps are distinct from a pure software development lifecycle.

- Strategy Definition ▴ The quantitative team defines the precise validation rules required for their trading strategies. This includes defining price bands, acceptable symbol sets, and other parameters.

- High-Level Synthesis (HLS) ▴ Engineers write the validation logic in a high-level language like C++ or C. An HLS compiler then translates this code into a hardware description language (VHDL or Verilog) that describes the digital circuit. This accelerates the development process compared to writing raw VHDL/Verilog.

- Synthesis and Place-and-Route ▴ The hardware description is synthesized into a netlist, which is a map of the logic gates and connections. A place-and-route tool then physically maps this circuit onto the FPGA’s available resources, optimizing for timing and performance.

- Simulation and Verification ▴ The resulting design is rigorously tested in a simulation environment using recorded market data. This step is critical to ensure the logic is bug-free and that its latency characteristics meet the design specifications.

- Deployment and Monitoring ▴ The configured FPGA is deployed in a server, typically co-located at the exchange’s data center. Real-time monitoring tools are used to track the FPGA’s performance, latency, and error rates, providing continuous feedback on its operational status.

The total latency of an FPGA validation pipeline, from network wire to CPU memory, can be compressed to a few hundred nanoseconds.

Risk Management at the Hardware Level

A profound consequence of hardware-accelerated validation is the ability to embed critical risk checks directly into the hardware fabric. In a traditional system, pre-trade risk checks are performed in software after the data has been received and processed by the CPU. This introduces a window of vulnerability where a flawed quote could potentially trigger an erroneous order before the software risk layer can intervene. By implementing these checks on the FPGA, they become an intrinsic part of the data ingestion pipeline.

A quote that fails a “fat-finger” check or exceeds a maximum order size parameter is discarded in nanoseconds, before it ever reaches the trading logic on the CPU. This hardens the entire trading system, providing a deterministic, ultra-fast layer of protection against both erroneous data and software-level failures. It is the ultimate implementation of risk management, operating at the speed of light.

References

- Gomola, A. & Szabó, C. (2012). High Frequency Trading Acceleration using FPGAs. In 2012 NORCHIP. IEEE.

- Hedge Think. (2025). Top Benefits of FPGA for High-Frequency Trading. Retrieved from Hedge Think.

- Vemeko FPGA. (2025). How to Use FPGAs for High-Frequency Trading (HFT) Acceleration?. Retrieved from Vemeko FPGA.

- Velvetech. (2025). In Pursuit of Ultra-Low Latency ▴ FPGA in High-Frequency Trading. Retrieved from Velvetech.

- Gupta, S. & Malss, K. (2016). High Frequency Trading Acceleration Using FPGAs. ResearchGate. Unpublished manuscript.

Reflection

The New Topography of Time

The integration of hardware acceleration redefines the temporal landscape of trading. When validation and risk management shrink to the nanosecond scale, the operational bottlenecks shift. The focus moves from the speed of computation within the server to the speed of light in the fiber connecting it to the exchange. The system’s performance becomes a function of physics and geography as much as of code and silicon.

This prompts a deeper series of questions for any trading entity. What is the true latency profile of your entire execution stack, from signal to settlement? Where are the hidden sources of jitter and delay in your software, your network, and your internal data pathways? Understanding the influence of hardware acceleration is the first step. The next is to view your own operational framework through this new lens, recognizing that in the modern market, every nanosecond is a piece of territory to be mapped, understood, and controlled.

Glossary

Quote Validation

Trading Logic

Hardware Acceleration

Market Data

Fpga

Order Book

Statistical Arbitrage

High-Level Synthesis

Pre-Trade Risk Checks