Concept

An institutional trader’s reality is defined by the physics of the market. When a packet containing critical market data leaves an exchange’s matching engine, it begins a race measured in nanoseconds. The journey across fiber optic cables is just the first leg. The true challenge begins the moment that packet arrives at your network interface card.

Within your system, a cascade of events unfolds, each adding a time penalty. The operating system’s network stack, the kernel’s context switching, the CPU’s instruction pipeline ▴ all of these layers of abstraction introduce delays. In a central limit order book (CLOB) system, where the price queue is a brutal competition of first-in, first-out, these delays represent a direct and quantifiable opportunity cost. The core of the problem is that general-purpose computing architectures, like CPUs, are designed for flexibility.

They process tasks through a sequential interpretation of instructions. This sequential nature, even when augmented by multiple cores, creates a fundamental bottleneck when reacting to market events.

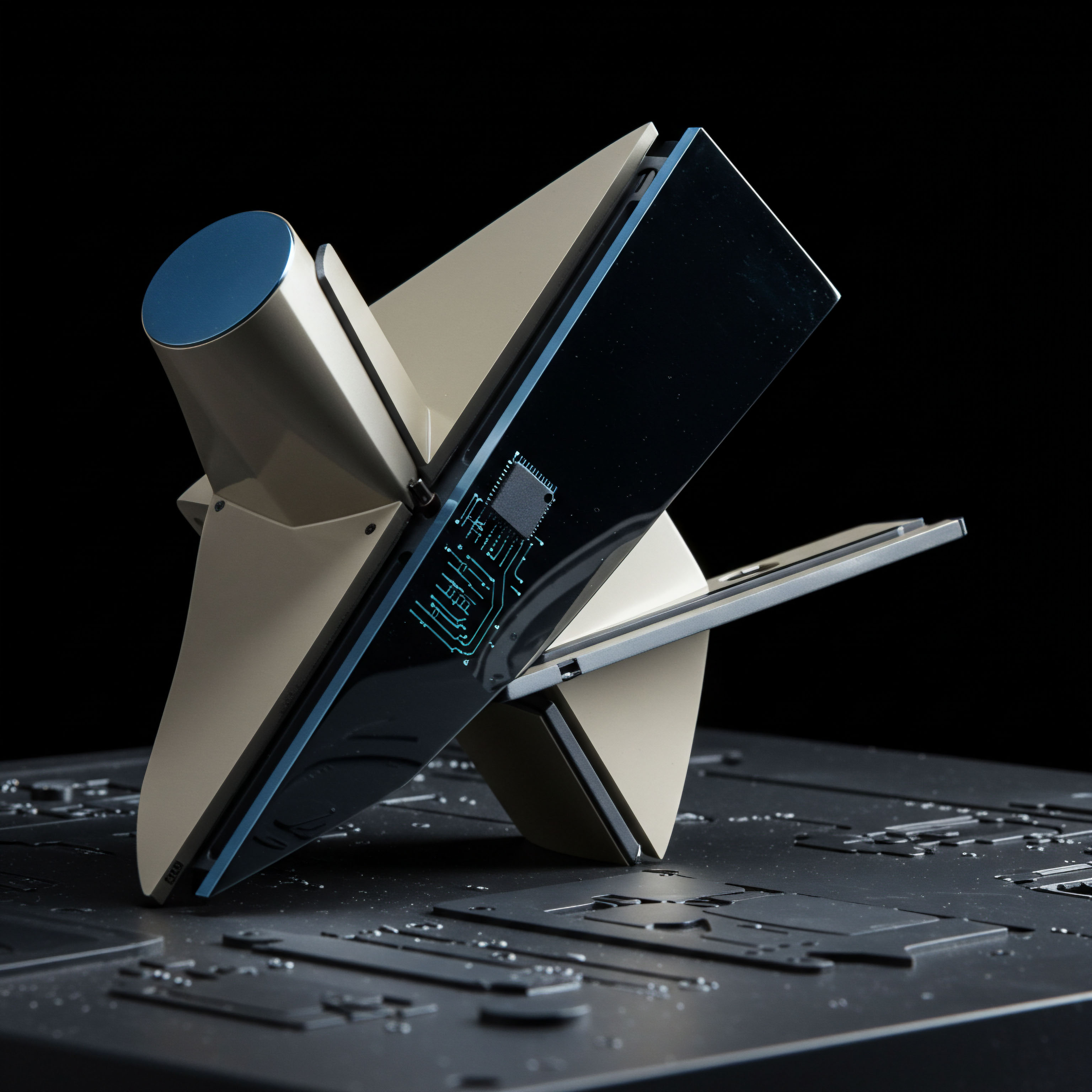

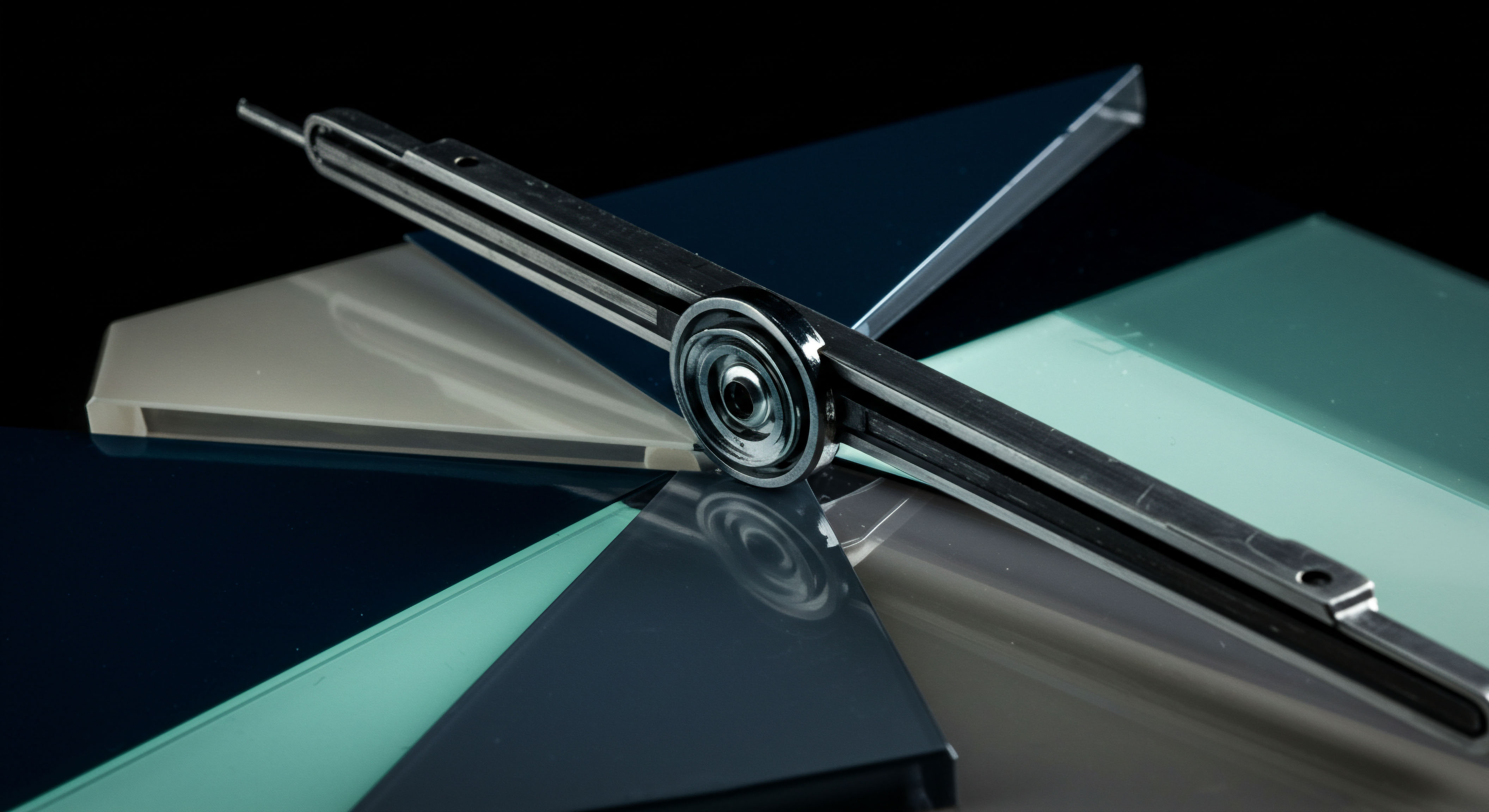

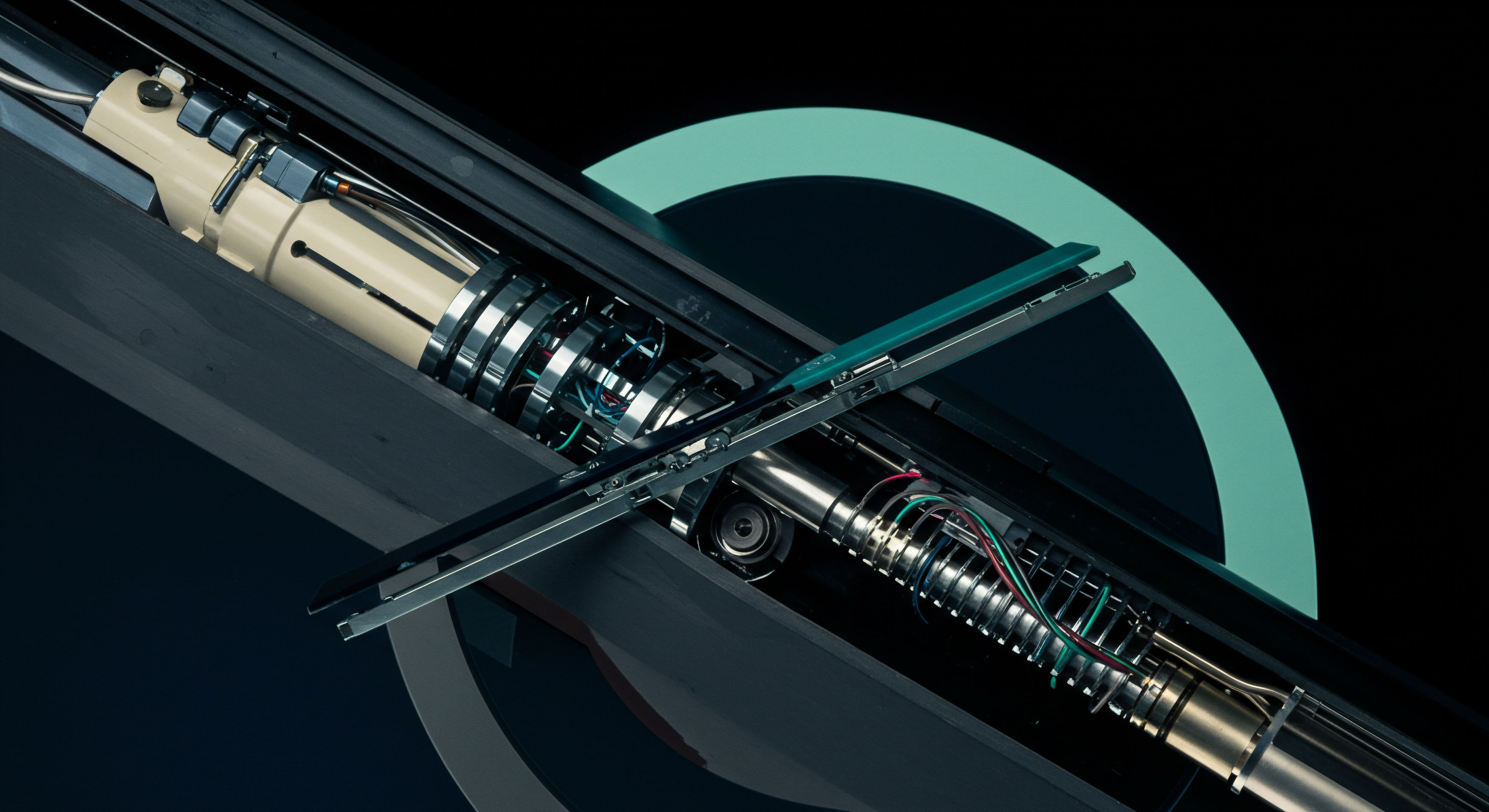

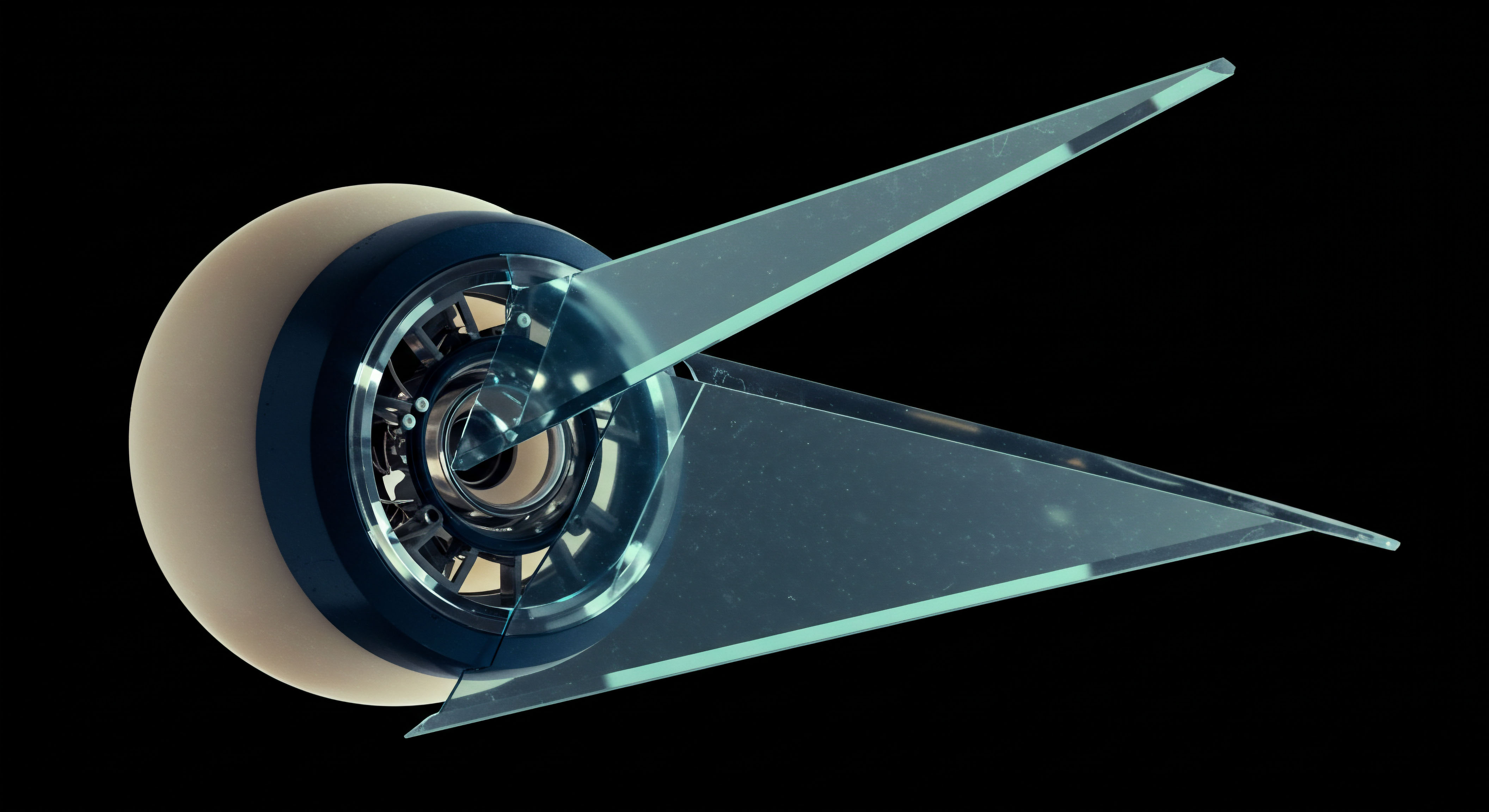

Hardware acceleration technologies, specifically Field-Programmable Gate Arrays (FPGAs), approach this problem from a completely different physical reality. An FPGA does not run a software application in the traditional sense. Instead, its internal logic gates and memory blocks are configured to become a hardware implementation of the required processing task. The application is synthesized directly into a custom digital circuit.

This architectural distinction is the source of its profound latency advantage. The layers of abstraction inherent in a CPU-based system ▴ the operating system, the drivers, the instruction decoding ▴ are eliminated. An FPGA connects directly to the network interface, processing raw data packets at wire speed. The logic for parsing a market data feed, updating an order book, and executing pre-trade risk checks is etched into the silicon’s configuration.

This results in a processing path that is not only orders of magnitude faster but also deterministic. The time taken to process one packet is identical to the time taken to process the next, removing the performance jitter that plagues software systems under heavy load. This determinism provides a stable and predictable foundation upon which high-frequency strategies can be built, transforming the race for liquidity from a game of chance into a contest of engineering precision.

A Field-Programmable Gate Array reduces latency by transforming a trading algorithm from a sequence of software instructions into a dedicated, physical hardware circuit, eliminating layers of computational overhead.

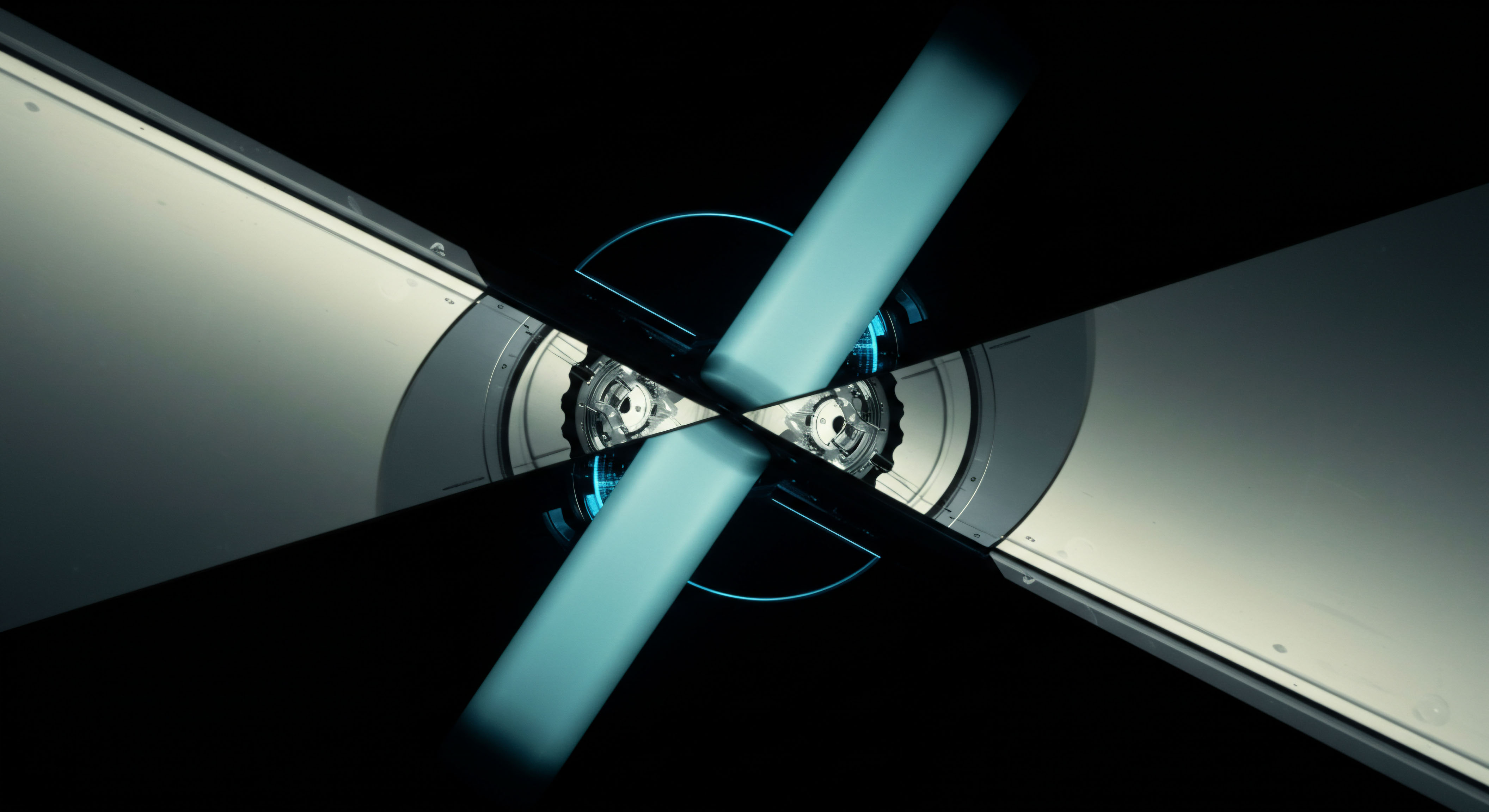

This direct hardware implementation allows for a degree of parallelism that is impossible to achieve in a conventional CPU architecture. A CPU core must handle tasks serially, fetching and executing one instruction at a time. An FPGA, by contrast, can be designed to perform thousands of operations simultaneously in a single clock cycle. Imagine a circuit designed specifically to parse the multiple fields of a market data message.

While a CPU would need to execute a series of instructions to read each field sequentially, an FPGA can have dedicated logic blocks that process every field in parallel. This massive parallelism is the key to handling the immense data volumes of modern markets without queuing delays. The system’s reaction time becomes a function of the circuit’s path length, measured in nanoseconds, rather than the execution time of a software program, measured in microseconds or milliseconds. It is a fundamental shift in how computational problems are solved in a trading context, moving from software emulation to direct hardware execution.

Strategy

The strategic adoption of FPGAs within a CLOB trading system represents a fundamental re-architecting of the entire execution stack. It is an acknowledgment that in latency-sensitive environments, the physical path of data is the primary determinant of success. The strategy extends beyond simply accelerating a single function; it involves a holistic redesign of how market data is ingested, processed, and acted upon. This requires a shift in thinking from software optimization to hardware-centric design, where the goal is to minimize the distance and the number of transformations data must undergo between the network wire and the trading decision.

The Architectural Shift from Sequential to Parallel Processing

A CPU-based system operates on a principle of sequential instruction execution. A processor core fetches an instruction, decodes it, executes it, and writes the result to memory. While modern CPUs have multiple cores and sophisticated pipelining to improve throughput, each core remains a sequential engine.

When a market data packet arrives, the CPU must execute a long series of instructions to handle the network protocol, parse the message format, and update the order book data structure. Each step happens in a sequence, creating a cumulative latency penalty.

An FPGA-based architecture enables a completely different model ▴ massive, task-specific parallelism. The logic of the FPGA can be configured to create numerous independent data paths that operate simultaneously. For example, upon the arrival of a market data packet, separate, dedicated circuits can concurrently perform:

- Packet Filtering ▴ A circuit can inspect the packet header to determine if it is relevant to the trading strategy, dropping irrelevant data without further processing.

- Protocol Decoding ▴ Multiple logic blocks can parse different fields of the message (e.g. symbol, price, quantity) at the same time.

- Order Book Update ▴ The parsed data can be used to update a representation of the order book stored in the FPGA’s own high-speed on-chip memory.

This parallel execution model means that the total processing time is determined by the longest single path (the critical path) through the circuit, a period which is vastly shorter than the sum of sequential operations in a CPU. This is the architectural foundation of the FPGA’s strategic advantage in high-frequency environments.

Determinism as a Strategic Asset

In quantitative trading, predictability is as valuable as speed. Software-based systems exhibit significant latency jitter, meaning the time they take to perform the same operation can vary widely. This variability arises from unpredictable events like operating system interrupts, task scheduling, cache misses, and network buffer management.

For a trading strategy that depends on precise timing, such as executing a multi-leg arbitrage across different venues, jitter can be catastrophic. An opportunity might be missed because the system was momentarily occupied with a background OS process.

Predictable, low-jitter performance is a core strategic benefit of FPGAs, as it allows for the reliable execution of complex, time-sensitive trading strategies.

FPGAs provide deterministic latency. Because the application is a physical circuit, the time it takes for a signal to travel from input to output is constant and predictable, down to the individual clock cycle. There is no operating system to cause preemption, no shared resources to create contention, and no instruction cache to miss. This deterministic nature is a powerful strategic asset.

It allows firms to model their execution performance with high precision, understand their exact position in the queue at the exchange, and build more complex strategies that rely on consistent, repeatable timing. Risk is reduced because the system’s behavior is known and reliable, even during periods of extreme market volatility when software systems are most likely to falter.

How Do Hardware Acceleration Approaches Compare?

Selecting the right processing architecture is a critical strategic decision. Each technology offers a different profile of performance, flexibility, and cost. The choice depends entirely on the specific requirements of the trading strategy and the firm’s technological capabilities.

| Attribute | CPU (Central Processing Unit) | GPU (Graphics Processing Unit) | FPGA (Field-Programmable Gate Array) |

|---|---|---|---|

| Primary Strength | Flexibility and ease of programming. Excellent for general-purpose, complex, and branching logic. | Massive data parallelism for large, uniform datasets. Ideal for machine learning model training. | Lowest possible latency, deterministic performance, and pipeline parallelism for streaming data. |

| Typical Latency | Microseconds to milliseconds (µs – ms). Highly variable due to OS and software overhead. | High latency for single operations due to data transfer overhead (PCIe bus). Optimized for throughput. | Nanoseconds to low microseconds (ns – µs). Highly deterministic and consistent. |

| Jitter | High. Unpredictable delays from system interrupts, context switches, and resource contention. | Moderate to High. Can be impacted by driver overhead and scheduling on the host CPU. | Extremely Low. Jitter is virtually nonexistent as operations are hardwired. |

| Development Complexity | Low. Vast ecosystem of high-level languages (C++, Python, Java) and development tools. | Medium. Requires specialized programming models like CUDA or OpenCL. | High. Requires hardware description languages (Verilog, VHDL) and a deep understanding of digital circuit design. |

| Use Case in Trading | Strategy development, risk management, post-trade analysis, and control of the overall system. | Training complex predictive models on historical data, backtesting, and some forms of risk calculation. | Market data parsing, order book management, pre-trade risk checks, and ultra-low-latency execution. |

Execution

The execution of an FPGA-based acceleration strategy is a meticulous process of hardware engineering and system integration. It involves identifying the most latency-critical components of the trading workflow and migrating them from software to dedicated hardware circuits. This process is not about replacing the CPU entirely, but about creating a hybrid system where each component performs the tasks for which it is best suited. The CPU handles complex, non-real-time logic, while the FPGA executes the time-critical data path with ruthless efficiency.

The Operational Playbook for Latency Reduction

Implementing an FPGA solution involves a systematic offloading of functions from the software domain to the hardware domain. The primary targets are tasks that lie directly on the critical path from market data ingress to order egress. A typical operational playbook would follow a sequence of targeted hardware implementations.

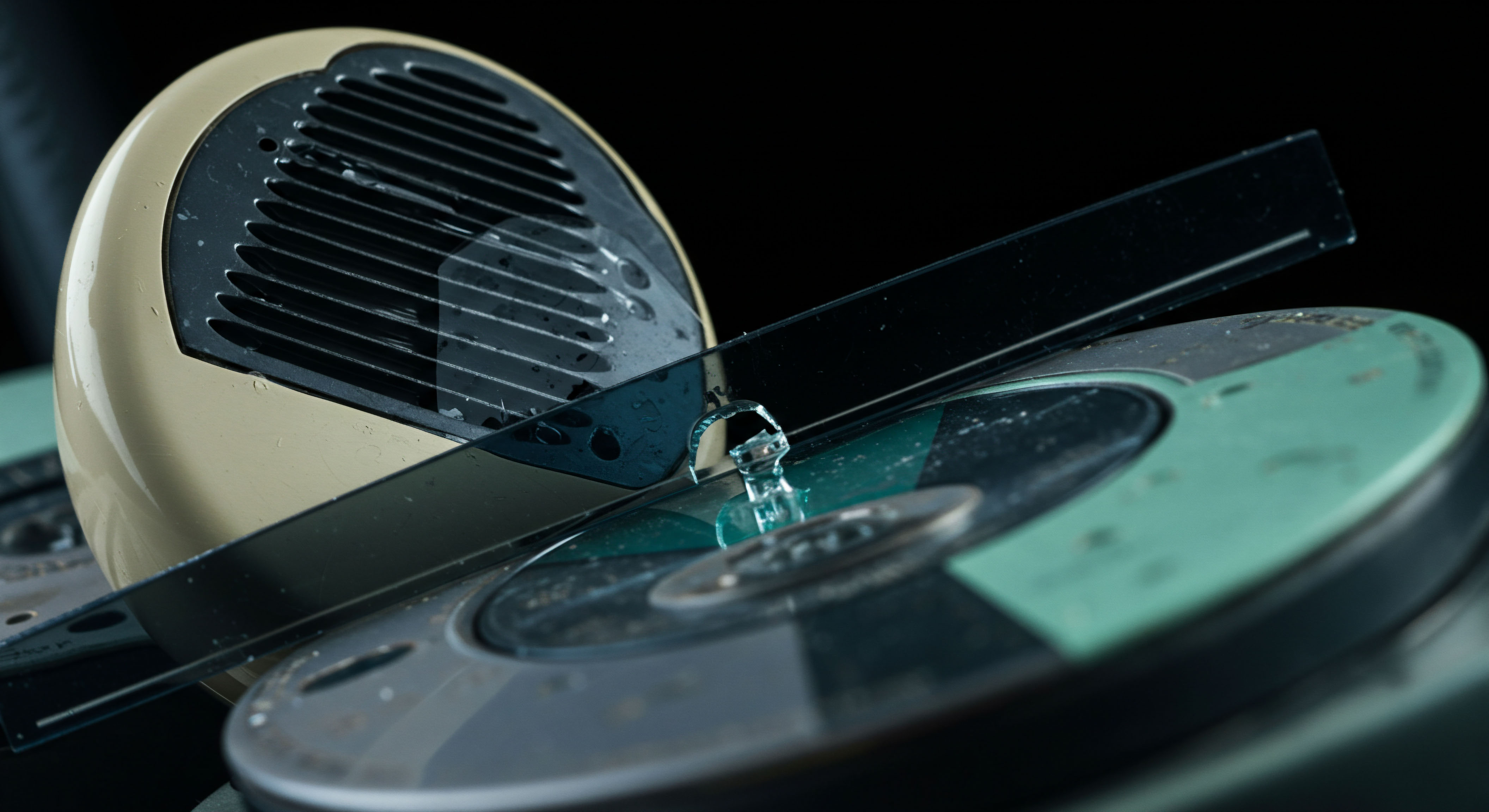

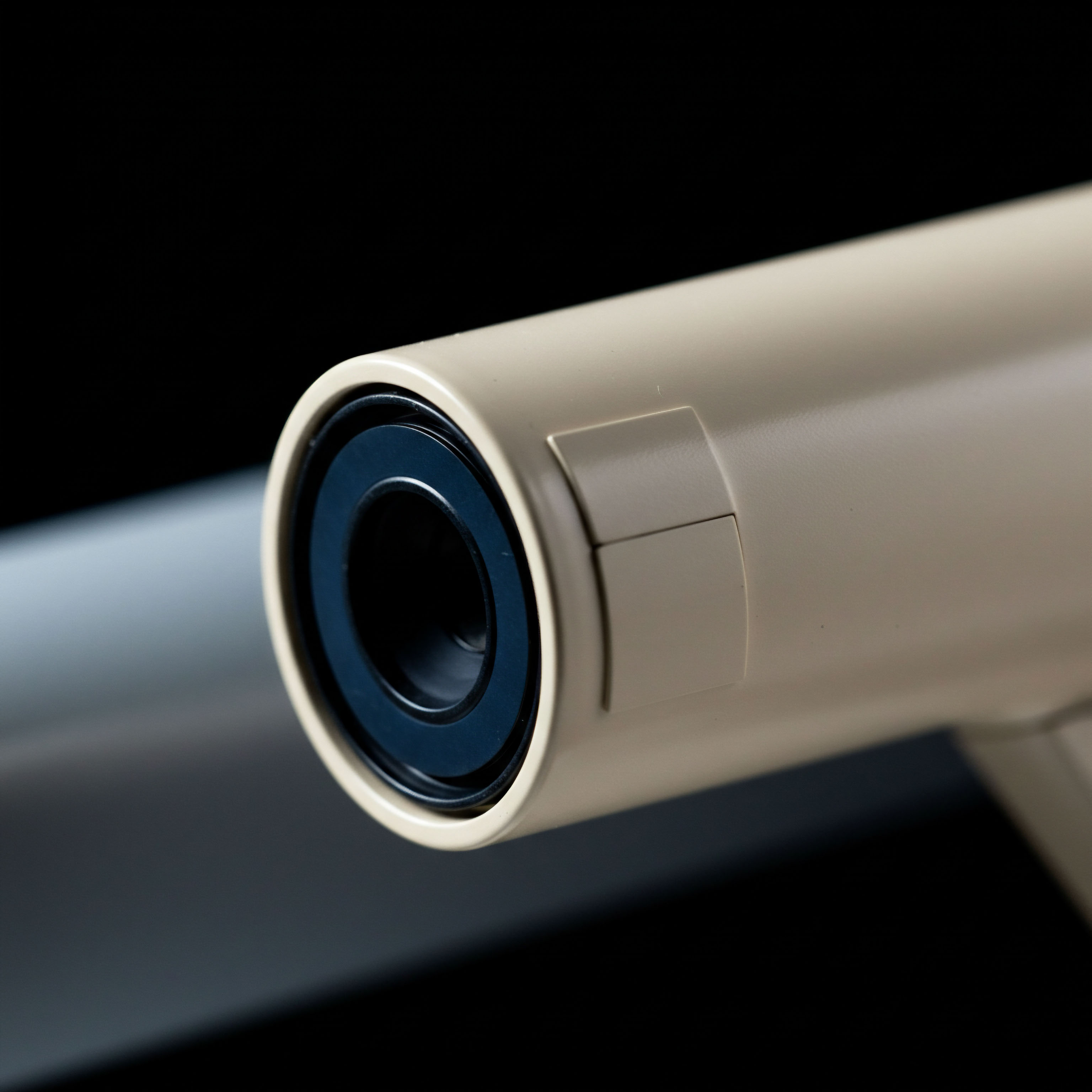

- Network Protocol Offloading ▴ The process begins at the physical network connection. In a software system, incoming Ethernet frames are passed by the Network Interface Card (NIC) to the operating system’s kernel. The kernel’s TCP/IP stack then processes the packet, which involves memory copies and context switches, adding significant latency. An FPGA-based system implements the entire network stack in hardware. The FPGA can parse Ethernet, IP, and UDP/TCP headers directly, presenting the application-level payload to the downstream logic without any involvement from the host CPU’s kernel. This step alone can save hundreds of microseconds.

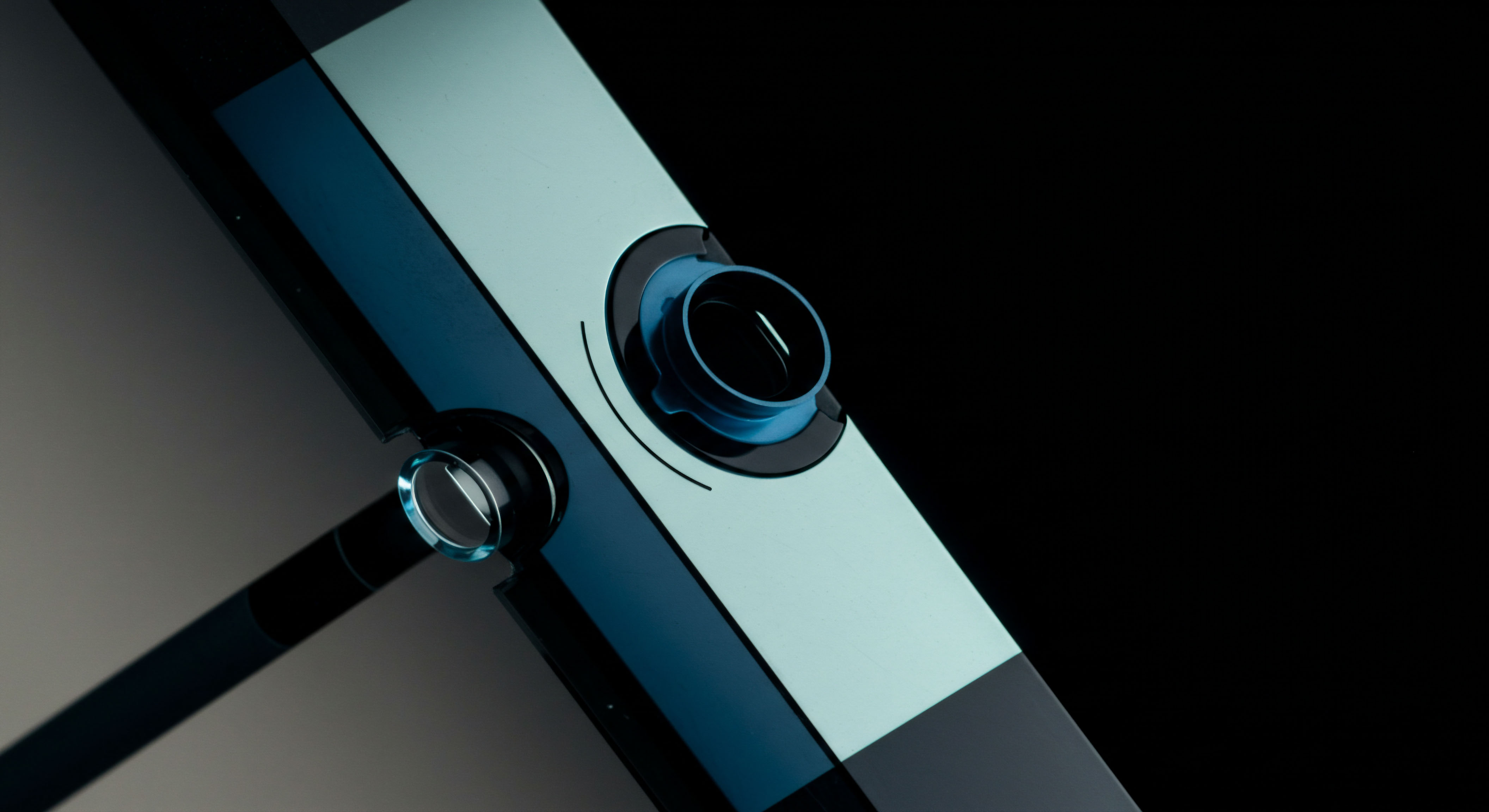

- Market Data Feed Parsing ▴ Exchanges disseminate market data using specialized, high-density protocols like FAST (FIX Adapted for Streaming) or proprietary binary formats. Parsing these protocols in software is CPU-intensive. An FPGA can be configured with a dedicated hardware decoder for the specific market data protocol being used. This decoder works at wire speed, extracting critical fields like ticker symbol, price, and size as the data streams in, with latencies as low as a few dozen nanoseconds.

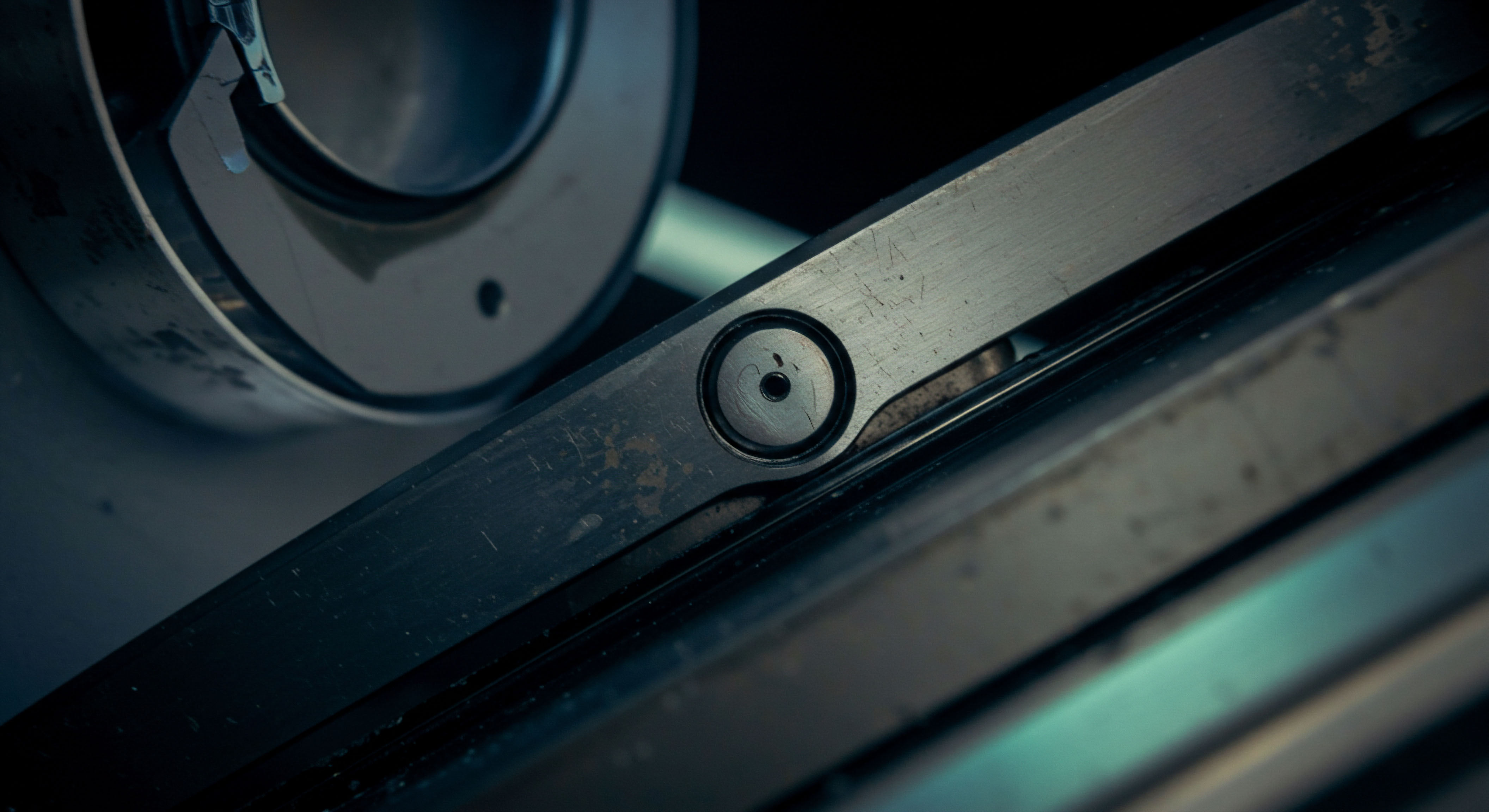

- On-Chip Order Book Management ▴ The central limit order book is the core data structure for any CLOB-based strategy. Maintaining this book in the CPU’s main memory (DRAM) creates a bottleneck. An FPGA contains blocks of extremely fast on-chip memory (BRAM or URAM). A complete, real-time copy of the most active price levels of the order book can be stored and managed directly within the FPGA. When a market data update is parsed, the order book logic can update the state of the book in a single clock cycle, providing an instantaneous view of the market.

- Hardwired Pre-Trade Risk And Execution Logic ▴ The final step before sending an order is executing the trading logic and applying risk checks. Simple, repetitive logic (e.g. “if the bid-ask spread for symbol XYZ is greater than $0.01, send a buy order”) can be implemented as a hardware circuit. Critical pre-trade risk checks, such as validating order size, price limits, and exposure, can also be hardwired into the FPGA. This allows the FPGA to make a trading decision and construct an outbound order packet autonomously, only passing exceptions or complex scenarios back to the host CPU.

Quantitative Modeling of Latency Reduction

The performance difference between a software-based and an FPGA-accelerated system is best understood through a quantitative breakdown of the tick-to-trade latency. The following table presents a hypothetical but realistic model of the time consumed at each stage of the process for a single market data event that triggers a trade.

| Processing Stage | Conventional CPU System Latency | FPGA-Accelerated System Latency | Commentary |

|---|---|---|---|

| Network Packet Ingress (NIC to App) | 5,000 – 20,000 ns | 0 ns (Handled in FPGA) | FPGA bypasses the OS kernel, eliminating driver and buffer copy delays. |

| Network Protocol Decoding (L2-L7) | 2,000 – 10,000 ns | 50 – 200 ns | Hardware decoders for Ethernet, IP, UDP, and the application protocol (e.g. FAST) run in a deep pipeline. |

| Order Book Update & State Access | 500 – 5,000 ns | 5 – 20 ns | Accessing on-chip BRAM/URAM is orders of magnitude faster than CPU cache or main memory. |

| Trading Logic Execution | 1,000 – 15,000 ns | 10 – 100 ns | Simple algorithmic logic becomes a combinatorial circuit with a fixed, minimal propagation delay. |

| Pre-Trade Risk Checks | 500 – 2,000 ns | 5 – 50 ns | Critical risk checks are implemented in parallel with the trading logic. |

| Outbound Order Packet Construction | 1,000 – 5,000 ns | 20 – 100 ns | The outbound packet is constructed in hardware and sent directly to the network PHY. |

| Total Tick-to-Trade Latency | 10 – 57 µs (Highly Variable) | 90 – 470 ns (Deterministic) | The FPGA-based system demonstrates a latency reduction of approximately 100x and removes performance jitter. |

Predictive Scenario Analysis

Consider a classic statistical arbitrage opportunity. A pricing dislocation appears between two highly correlated securities, Asset A and Asset B, on the same exchange. This opportunity is fleeting, likely to be corrected within microseconds. Two high-frequency trading firms, Firm S (Software-based) and Firm H (Hardware-accelerated), detect the event simultaneously.

At time T=0, the exchange disseminates a trade message for Asset A at an anomalous price. The packet arrives at the collocated servers of both firms. For Firm S, the packet is received by a standard NIC and handed to the Linux kernel. The kernel processes the network stack, resulting in a context switch and memory copies, delivering the data to the user-space application at T+7µs.

The C++ application then parses the FAST protocol message, taking another 4µs. It accesses its in-memory order book to confirm the state of Asset A and Asset B, a process that takes 1µs due to cache coherency traffic. The trading logic runs, confirms the arbitrage, and decides to sell Asset A and buy Asset B. This takes 5µs. Finally, the pre-trade risk checks are applied and the two outbound orders are constructed and sent back to the kernel, which consumes another 8µs before the packets leave the server. The first order from Firm S is sent at approximately T+25µs.

For Firm H, the story is entirely different. The same packet at T=0 is ingested directly by an FPGA. The hardware network stack and FAST decoder process the message in a pipeline, with the relevant fields available to the trading logic at T+150ns. The FPGA’s on-chip memory contains the relevant order book state, which is accessed in parallel with the decoding, taking 10ns.

The arbitrage logic is a hardwired circuit that evaluates the condition and triggers the outbound order logic in 20ns. The pre-trade risk checks are also implemented as parallel circuits and add no sequential delay. The two outbound order packets are constructed in hardware and sent to the wire by T+250ns. Firm H’s orders reach the exchange’s matching engine nearly 100 times faster than Firm S’s orders. In the world of CLOB priority, Firm H captures the full alpha of the opportunity, while Firm S’s orders arrive late and are either rejected or filled at a worse price after the arbitrage has been closed.

What Is the System Integration Architecture?

The integration of FPGAs creates a hybrid computing architecture where latency-critical functions are executed in hardware and complex, less time-sensitive tasks remain in software. This division of labor maximizes performance while retaining necessary flexibility.

- Physical Integration ▴ The FPGA resides on a specialized NIC or a PCIe accelerator card within a high-performance server. It is positioned directly between the external network connection and the host system’s CPU, allowing it to intercept and process data before the CPU is even aware of its arrival.

- Data Flow ▴ Raw market data flows from the exchange into the FPGA’s network port. The FPGA performs all the real-time processing ▴ filtering, decoding, book building, and executing simple trading logic. Only specific, necessary information is passed up to the host CPU over the low-latency PCIe bus. This could include processed market events, order acknowledgments, or alerts for conditions the FPGA cannot handle.

- CPU’s Role ▴ The host CPU is freed from the low-level processing and can focus on higher-level strategic functions. These include managing the overall trading strategy, performing complex calculations that are not suitable for hardware implementation, running historical analysis, and providing the primary interface for human traders to monitor and control the system.

- Software Interface ▴ A custom driver and API are required to manage the communication between the CPU and the FPGA. This software layer allows the trading application running on the CPU to configure the FPGA, receive data from it, and send commands (like instructing the FPGA to place a complex order that it cannot construct on its own).

References

- Kumar, Sandeep, et al. “Building Low-Latency Order Books with Hybrid Binary-Linear Search Data Structures on FPGAs.” 2022 25th Euromicro Conference on Digital System Design (DSD), 2022.

- Leber, Christian, et al. “High Frequency Trading Acceleration using FPGAs.” 2011 International Conference on Field-Programmable Technology, 2011.

- Reinders, James. “How FPGAs Accelerate Financial Services Workloads.” HPCwire, 2018.

- O’Hara, Maureen. “High frequency market microstructure.” Journal of Financial Economics, vol. 116, no. 2, 2015, pp. 257-270.

- Thomas, David, et al. “Network-Level FPGA Acceleration of Low Latency Market Data Feed Arbitration.” IEEE Transactions on Computers, vol. 64, no. 1, 2015, pp. 289-302.

Reflection

Engineering the Physicality of Alpha

The integration of hardware acceleration into a trading system is more than a technological upgrade; it is a philosophical shift. It compels a firm to view its entire operational framework not as a collection of software applications, but as a single, cohesive execution machine. The data path from the exchange to your decision engine is a physical system governed by the laws of physics and information theory. Every layer of abstraction, every software queue, every microsecond of processing time must be justified against the direct cost of lost opportunity.

When your algorithm is no longer software but a circuit, how does that change your perception of risk, strategy, and the very nature of alpha? The ultimate edge lies in designing a system where the path from information to action is as direct and deterministic as the laws of physics will allow.

Glossary

Market Data

Central Limit Order Book

Hardware Acceleration

Fpga

Pre-Trade Risk Checks

Market Data Feed

Jitter

Latency

Order Book

Trading Strategy

Deterministic Latency

Limit Order Book

Pre-Trade Risk

Trading Logic

Tick-To-Trade

High-Frequency Trading

Fast Protocol