Concept

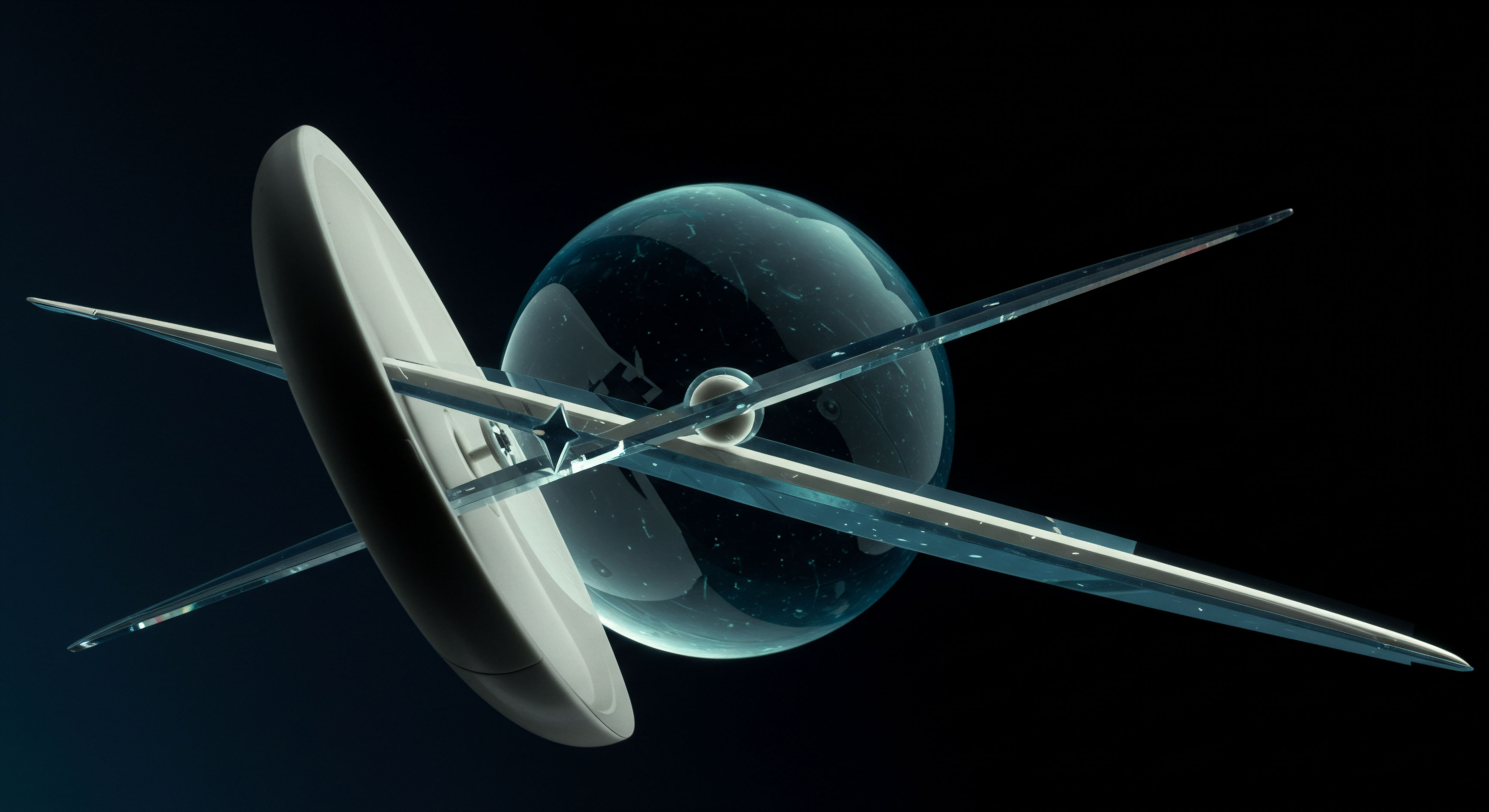

The architecture of a high-performance trading system is a direct reflection of a firm’s core philosophy on market interaction. The decision to integrate Field-Programmable Gate Arrays (FPGAs) with traditional Central Processing Units (CPUs) is a deliberate engineering choice that addresses the fundamental duality of modern electronic markets ▴ the non-negotiable requirement for microsecond-level speed and the equally critical need for strategic adaptability. A hybrid system is the physical manifestation of a two-pronged approach to market engagement.

It acknowledges that some trading functions are purely mechanistic and benefit from being etched into silicon for deterministic, near-instantaneous execution. Concurrently, it recognizes that alpha generation, risk management, and strategic evolution are fluid, cognitive processes that demand the flexibility and programmability of a conventional software environment.

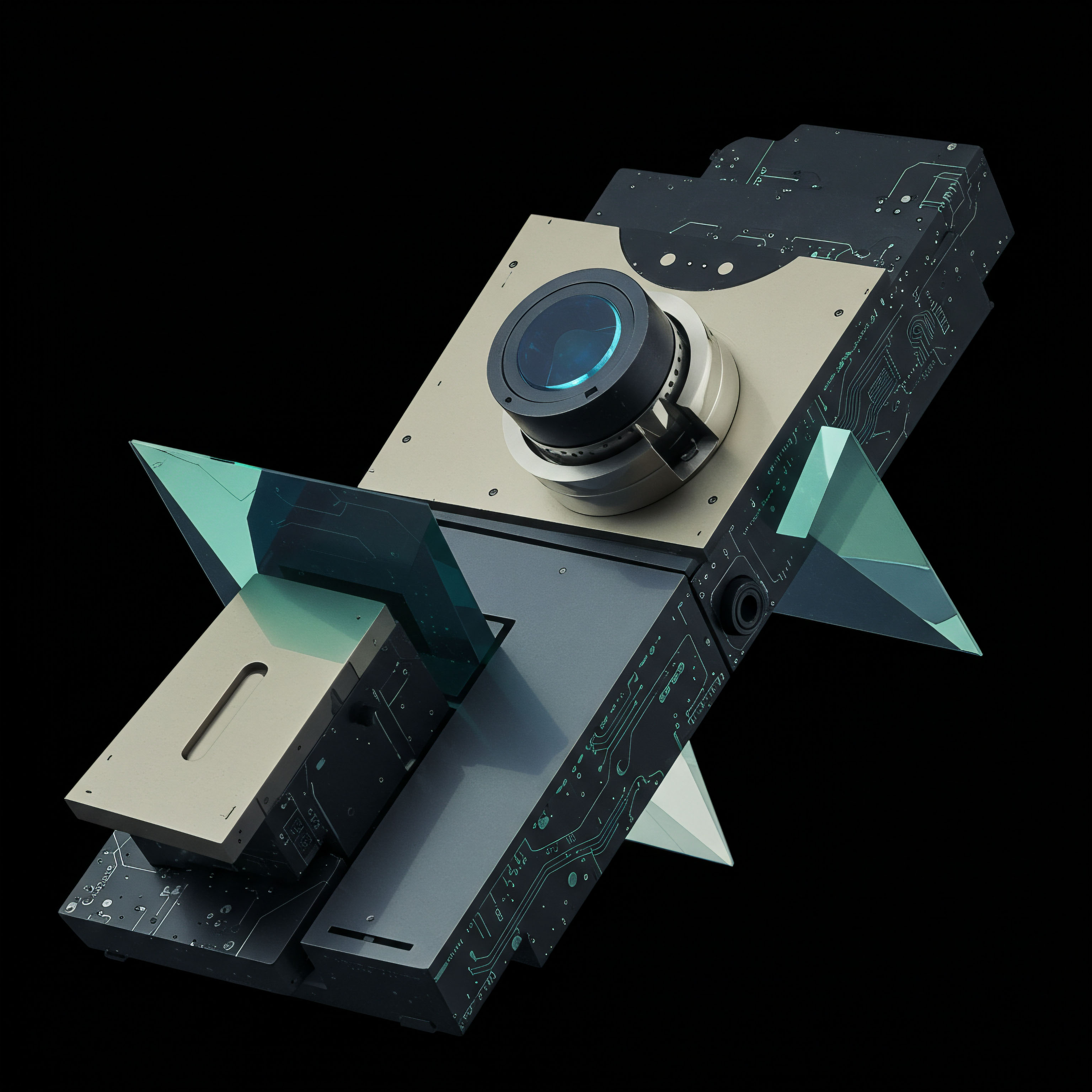

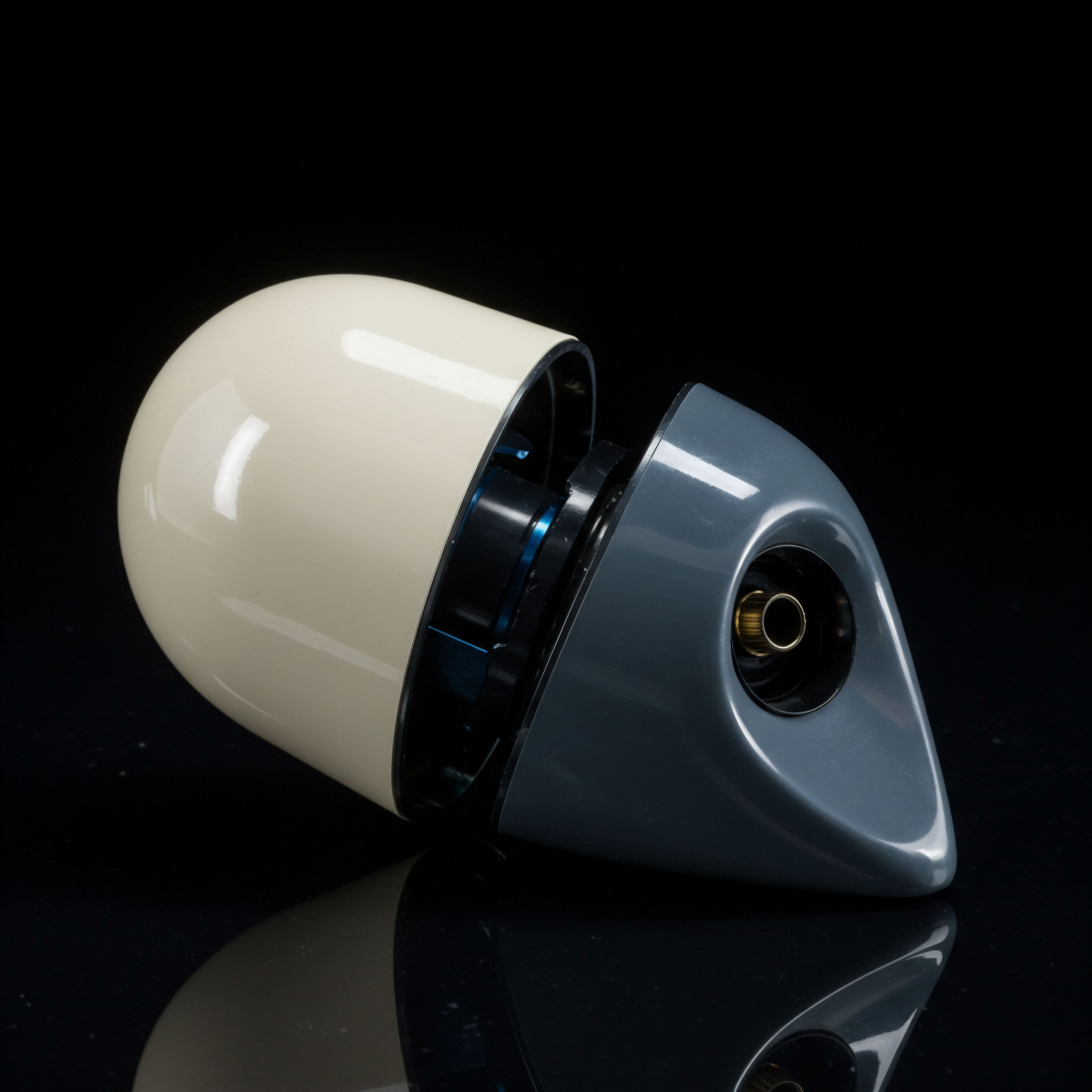

Viewing this through the lens of a systems architect, the CPU and FPGA are not competitors; they are specialized components within a unified execution chassis. The FPGA is the system’s reflex arc. It is placed at the very edge of the trading apparatus, directly interfacing with the torrent of market data from an exchange. Its purpose is singular ▴ to perform a small set of critical, repetitive tasks with the lowest possible latency.

This includes filtering raw data packets, normalizing different exchange protocols into a common internal format, and executing pre-defined, low-complexity orders. The logic is physically laid out in the hardware, allowing for massively parallel processing where every nanosecond is accounted for. This is where the battle for the top of the order book is won.

The CPU, in contrast, represents the system’s strategic brain. It operates on the pre-processed, clean data stream curated by the FPGA. Freed from the low-level, high-volume task of parsing raw market data, the CPU dedicates its resources to higher-order functions. This is where complex trading logic is developed, where quantitative models are calibrated, where portfolios are managed, and where new strategies are rapidly prototyped and backtested.

The software-based environment of the CPU provides the strategic flexibility necessary to adapt to changing market regimes, to deploy nuanced multi-leg orders, or to conduct sophisticated post-trade analysis. This functional segregation is the core principle of the hybrid model, creating an architecture that is both brutally fast and intellectually agile.

A hybrid CPU-FPGA system creates a symbiotic relationship where the FPGA handles deterministic, low-latency tasks at the hardware level, while the CPU manages complex, adaptive strategic logic in a flexible software environment.

Why Is This Hybridization Necessary in Modern Markets?

The evolution of market structure itself has driven the demand for such hybrid systems. In the past, a firm could compete primarily on the sophistication of its algorithms or the speed of its infrastructure. Today, sustained success requires excellence on both fronts. A pure software-based system running on a CPU, no matter how optimized, will always be handicapped by the inherent overhead of its operating system and sequential instruction processing when compared to an FPGA.

This can result in a critical latency disadvantage in highly competitive, co-located environments. Conversely, a pure FPGA-based system, while exceptionally fast for a specific task, is notoriously difficult and time-consuming to reprogram. Deploying a new strategy could take weeks or months of hardware engineering, a timeframe that is untenable in dynamic markets. A firm locked into a pure FPGA solution might win the speed race but lose the innovation war.

The hybrid architecture resolves this impasse. It provides a stable, ultra-low-latency foundation (the FPGA) upon which a dynamic, adaptable strategy layer (the CPU) can be built. This allows a trading firm to protect its existing high-frequency strategies that rely on sheer speed while simultaneously exploring new sources of alpha that require more complex logic.

It is a system designed for both offense and defense, optimizing for the present while providing the necessary framework to adapt for the future. This architectural choice is a profound statement about a firm’s intent to compete and endure across all market conditions.

Strategy

Adopting a hybrid CPU-FPGA architecture is a strategic commitment to a dual-mandate operational model. This model seeks to master two distinct temporal domains within trading ▴ the nanosecond-level domain of order execution and the human-timescale domain of strategy development and adaptation. The strategic framework is therefore built upon a clear and disciplined allocation of tasks, assigning each function to the computational resource best suited to its nature. This is a strategy of specialization, designed to extract the maximum possible performance from each component to create a cohesive and dominant trading system.

The Latency Arbitrage Strategy

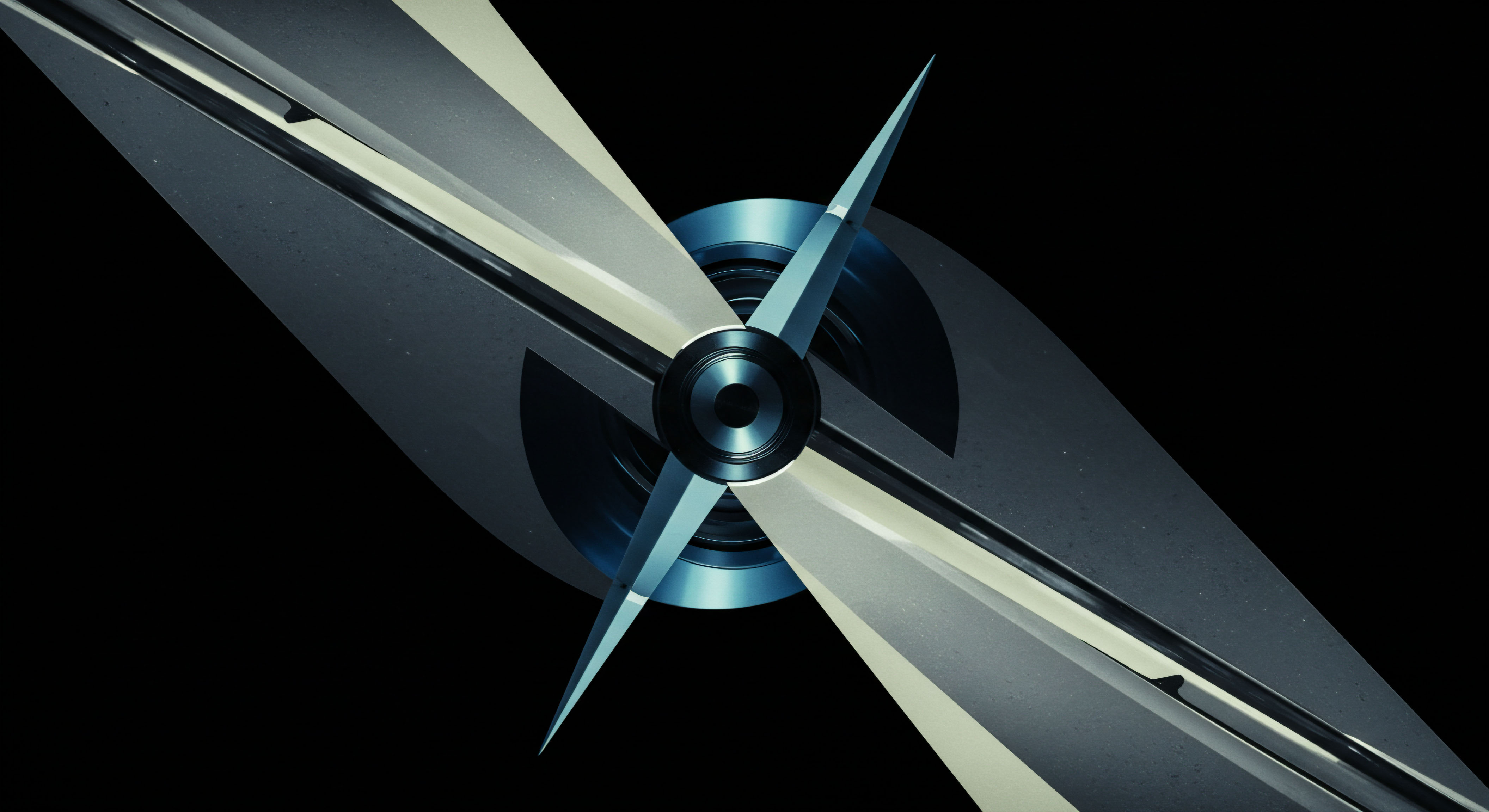

At its core, the FPGA component is deployed to pursue a strategy of latency arbitrage. This strategy is predicated on the ability to react to market events faster than any competitor relying on a software-based system. The execution of this strategy involves offloading a specific set of functions to the FPGA, where they can be processed in parallel at the hardware level. This creates a deterministic and predictable execution path, free from the jitter and delays associated with general-purpose operating systems.

- Market Data Ingestion and Processing The FPGA is positioned to receive the raw FIX/FAST protocol feed directly from the exchange. Its parallel architecture allows it to parse, decode, and filter this data stream simultaneously, constructing an internal representation of the order book in real-time. This process can be an order of magnitude faster than a CPU attempting to do the same task.

- Pre-Trade Risk Checks A subset of critical, simple risk checks are embedded directly into the FPGA’s logic. These include “fat-finger” checks on order size, price collar validations, and checks against maximum order quantity limits. By performing these checks in hardware, the system ensures that they are executed in mere nanoseconds, preventing the introduction of latency into the critical path of an order.

- Order Triggering and Execution For the simplest and most time-sensitive strategies (e.g. simple market making or latency arbitrage), the entire trading logic can be implemented on the FPGA. An incoming market data update can trigger an order that is generated and sent to the exchange without ever involving the CPU. This creates the shortest possible “tick-to-trade” latency.

The strategic allocation of tasks within a hybrid system allows a firm to compete on speed for established, latency-sensitive strategies while retaining the agility to develop new, complex alphas.

The Strategic Flexibility Framework

While the FPGA secures the low-latency frontier, the CPU provides the framework for sustained strategic advantage through adaptability and complexity. By offloading the most time-critical tasks to the FPGA, the CPU is liberated to perform a range of higher-level functions that are essential for long-term profitability. This is where the firm’s intellectual property is truly brought to bear.

How Does the CPU Layer Foster Innovation?

The CPU layer is the system’s innovation engine. It operates on a clean, structured data feed provided by the FPGA, allowing strategists and quantitative analysts to work in a high-level programming environment (like C++ or Python) without needing specialized hardware knowledge. This drastically reduces the development cycle for new strategies.

A new trading idea can be coded, backtested against historical data, and deployed in a matter of hours or days, rather than the weeks or months required for an FPGA redesign. This rapid iteration cycle is a powerful competitive advantage, allowing the firm to quickly respond to new market opportunities or changing conditions.

Furthermore, the CPU is where complex, multi-faceted strategies are managed. These might include statistical arbitrage strategies that analyze relationships between hundreds of securities, multi-leg options strategies requiring complex pricing models, or portfolio-level risk management systems that need a global view of the firm’s positions. These tasks are computationally intensive but are not sensitive to nanosecond-level latency in the same way as a simple order execution. The CPU’s powerful sequential processing capabilities and large memory access are perfectly suited for this class of problem.

Comparative System Architectures

To fully appreciate the strategic positioning of the hybrid model, it is useful to compare it against its alternatives. The following table outlines the key operational characteristics of each architectural choice, illustrating the trade-offs involved.

| Parameter | Pure CPU System | Pure FPGA System | Hybrid CPU-FPGA System |

|---|---|---|---|

| Execution Latency | Moderate to High (microseconds) | Ultra-Low (nanoseconds) | Ultra-Low for critical path; higher for complex logic |

| Strategic Flexibility | Very High | Very Low | Very High |

| Development Time | Short | Very Long | Short for CPU (strategies); Long for FPGA (core functions) |

| Cost of Strategy Change | Low | Very High | Low |

| Throughput | Moderate | Very High | Very High |

| Ideal Use Case | Lower-frequency strategies, complex analytics | Static, ultra-high-frequency market making | Comprehensive, multi-strategy electronic trading |

The table clearly demonstrates the strategic compromise inherent in the pure systems. A pure CPU system sacrifices speed for flexibility, while a pure FPGA system makes the opposite trade-off. The hybrid system is designed to break this compromise.

It achieves best-in-class latency for the functions that require it, while simultaneously providing a platform for rapid and complex strategy development. It is an architecture designed not for a single type of market, but for all of them.

Execution

The implementation of a hybrid CPU-FPGA trading system is a complex engineering undertaking that requires a deep understanding of both hardware and software, as well as the specific microstructure of the markets being traded. The execution phase moves beyond theoretical benefits to the granular details of system architecture, data flow, and risk management. A successful deployment hinges on a meticulously planned operational playbook that governs how these two disparate processing paradigms are integrated into a single, cohesive execution platform.

The Operational Playbook an Architectural Blueprint

The physical and logical layout of the system is the foundation of its performance. The goal is to create the shortest and most deterministic path for data moving from the exchange to the execution logic and back again. The following represents a standard operational blueprint for such a system.

- Physical Co-location The server housing the hybrid system is placed in the same data center as the exchange’s matching engine. This minimizes network latency, which is often the largest single component of the round-trip time.

- Direct Market Access (DMA) The system connects directly to the exchange’s raw market data feed via a high-speed network interface card (NIC). A specialized “smart NIC” or the FPGA itself often handles the initial packet capture to bypass the server’s kernel and reduce latency.

- FPGA as the Front Door The raw data packets from the NIC are fed directly into the FPGA. The FPGA is responsible for the initial, time-critical processing stages:

- Protocol Decoding It parses the exchange-specific protocol (e.g. ITCH/OUCH, FAST).

- Data Filtering It filters for the specific securities or instruments relevant to the active trading strategies.

- Book Building It maintains a real-time, in-hardware model of the order book for the instruments it is tracking.

- Low-Latency Execution Path It houses the logic for the most time-sensitive strategies. If an incoming market data update triggers one of these strategies, the FPGA can generate and send an order in nanoseconds, without CPU intervention.

- High-Speed Internal Bus The FPGA communicates with the host CPU over a high-speed bus, typically PCIe. This connection is critical for transferring the processed market data to the CPU and for receiving commands or more complex orders from the CPU.

- CPU as the Strategy Engine The CPU runs the main trading application. It receives a clean, structured stream of market events from the FPGA. Its responsibilities include:

- Complex Strategy Logic Executing algorithms that are too complex or state-dependent for the FPGA.

- Portfolio-Level Risk Management Maintaining a global view of the firm’s positions, P&L, and risk exposures.

- Strategy Control and Command Sending parameters and commands to the FPGA, such as activating or deactivating specific hardware-based strategies or updating risk limits.

- Post-Trade Analysis and Logging Recording all trading activity for regulatory compliance and future analysis.

Quantitative Modeling and Data Analysis

A quantitative understanding of latency is essential for optimizing a hybrid system. The concept of a “latency budget” is used to account for every nanosecond of delay in the system’s round-trip path. The following table provides a granular, hypothetical breakdown of the latency for a simple “tick-to-trade” event, comparing a pure software implementation with a hybrid architecture where the trade is executed entirely within the FPGA.

| Process Stage | Pure CPU System Latency (ns) | Hybrid FPGA Path Latency (ns) | Notes |

|---|---|---|---|

| Network Transit (Exchange to Server) | 500 | 500 | Dependent on physical distance; identical for both systems. |

| Packet Capture (NIC to Memory) | 1,500 | 50 | FPGA bypasses the kernel network stack (kernel bypass). |

| Protocol Decoding | 800 | 70 | FPGA performs parallel hardware decoding. |

| Order Book Update | 450 | 40 | FPGA maintains the book in dedicated hardware logic. |

| Strategy Logic Execution | 2,500 | 60 | CPU involves cache misses and context switching; FPGA logic is deterministic. |

| Pre-Trade Risk Check | 600 | 20 | Simple checks are faster in hardware. |

| Order Generation | 700 | 30 | FPGA generates the packet directly. |

| Network Egress (Server to Exchange) | 1,000 | 50 | FPGA can write directly to the NIC, bypassing the OS. |

| Network Transit (Server to Exchange) | 500 | 500 | Identical for both systems. |

| Total Round-Trip Latency | 8,550 ns (8.55 µs) | 1,320 ns (1.32 µs) | A 6.5x latency reduction. |

The disciplined segregation of duties between the CPU and FPGA is the cornerstone of a successful hybrid trading architecture, maximizing both speed and strategic agility.

Predictive Scenario Analysis a Market-Making Case Study

Consider a market-making firm operating in a highly competitive futures market. Their primary strategy is to maintain a tight bid-ask spread on a specific contract, capturing the spread on thousands of small trades per day. Their competitor, “Firm B,” uses a highly optimized pure CPU system.

Our firm deploys a new hybrid CPU-FPGA system. An economic data release is scheduled, which is expected to cause a surge in volatility and trading volume.

At the moment the data is released, the market becomes highly active. A large institutional sell order hits the market, consuming the best bid. The exchange disseminates this information via its market data feed. Both our firm’s system and Firm B’s system receive the data packet at the same instant.

From here, the latency budget becomes critical. Firm B’s CPU-based system takes approximately 8.5 microseconds to process the event, decide to place a new bid at the next price level, and send the order. During this time, other fast actors are also reacting.

Our firm’s hybrid system, however, has this market-making logic encoded on the FPGA. The FPGA processes the same market event, recognizes the consumed bid, and generates a new order in just 1.3 microseconds. This order is sent to the exchange and is placed at the top of the new order book queue nearly 7 microseconds before Firm B’s order even leaves their server. When the wave of subsequent sell orders arrives, our firm’s bid is the first in line to be executed, allowing it to capture the spread.

Firm B’s order, arriving later, is further down the queue and may not get filled. Over the course of a volatile trading session, this nanosecond-level advantage, repeated thousands of times, translates into a significant difference in profitability. Meanwhile, our firm’s quantitative team, using the CPU component of the same system, is analyzing the market dynamics in real-time and preparing to deploy a new, more complex momentum-following strategy if the market begins to trend, a strategic pivot that would be impossible for a pure-FPGA firm to execute in a timely manner.

System Integration and Technological Architecture

The technological architecture must be robust and designed for high availability. Key integration points include the Application Programming Interfaces (APIs) between the CPU and FPGA. This is often a custom, low-level API designed to minimize the overhead of communication. It allows the CPU software to perform functions like loading new strategy parameters into the FPGA’s memory, subscribing to specific data streams, and receiving notifications of hardware-level trade executions.

The system must also integrate with post-trade systems for clearing and settlement, and with market data recorders for compliance. The entire architecture is built on a foundation of high-precision time-stamping, using protocols like PTP (Precision Time Protocol) to synchronize clocks across all components to within nanoseconds, ensuring that post-trade analysis is accurate and that regulatory reporting requirements (like MiFID II’s clock synchronization standards) are met.

References

- Fu, Haohuan, et al. “Accelerating Financial Market Server through Hybrid List Design.” 2017 IEEE 25th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2017.

- Litz, Heiner, et al. “DSL programmable engine for High Frequency Trading acceleration.” 2011 International Conference on Field-Programmable Technology, 2011.

- Gomersall, Antony. “FPGAs for HFT ▴ A Survey and Look into the Future.” High-Frequency Trading, 2014.

- Gupta, Ankur, et al. “A survey of accelerator-based financial computing.” Journal of Parallel and Distributed Computing, vol. 108, 2017, pp. 121-137.

- De Coster, I. et al. “Hardware/Software Co-design for High-Frequency Trading.” IEEE Micro, vol. 36, no. 5, 2016, pp. 58-66.

- Harris, Larry. “Trading and Exchanges ▴ Market Microstructure for Practitioners.” Oxford University Press, 2003.

- Cong, Jason, et al. “A Survey of High-Level Synthesis for FPGA-based Acceleration.” ACM Transactions on Reconfigurable Technology and Systems (TRETS), vol. 12, no. 2, 2019, pp. 1-26.

Reflection

The examination of a hybrid CPU-FPGA system moves beyond a simple technical comparison. It prompts a deeper consideration of your own firm’s operational philosophy. Viewing your trading infrastructure as a complete, integrated system is the first step.

Where are the boundaries between your reflex-driven execution and your considered strategic decisions? How does your current architecture facilitate or impede the flow of information between these two domains?

Is Your Architecture a Strategic Asset?

The knowledge of how these systems are constructed provides a new lens through which to evaluate your own capabilities. The true potential lies in understanding that the optimal architecture is a direct reflection of your strategic intent. A system designed for speed at the expense of all else is brittle.

A system designed for flexibility without a low-latency core will be outmaneuvered. The challenge is to build an operational framework where these two attributes are not in opposition, but are instead complementary components of a single, powerful engine for navigating modern financial markets.

Glossary

Hybrid System

Risk Management

Systems Architect

Market Data

Order Book

Fpga

Cpu

Hybrid Architecture

System Designed

Hybrid Cpu-Fpga

Latency Arbitrage

Pre-Trade Risk Checks

Tick-To-Trade

Direct Market Access

Hybrid Cpu-Fpga System