Concept

The pursuit of alpha in modern financial markets is a function of managing probabilities. Your entire operational framework is built to tilt those probabilities in your favor. Yet, a fundamental variable often undermines the most sophisticated strategies ▴ time. Specifically, the inconsistency in processing time, known as jitter.

When a trading system’s response to a market event varies unpredictably, even by microseconds, the statistical foundation of a strategy begins to erode. The system becomes a source of endogenous, unquantifiable risk. The solution lies in fundamentally re-architecting the processing layer to eliminate this temporal uncertainty. This is the precise domain of Field-Programmable Gate Arrays (FPGAs).

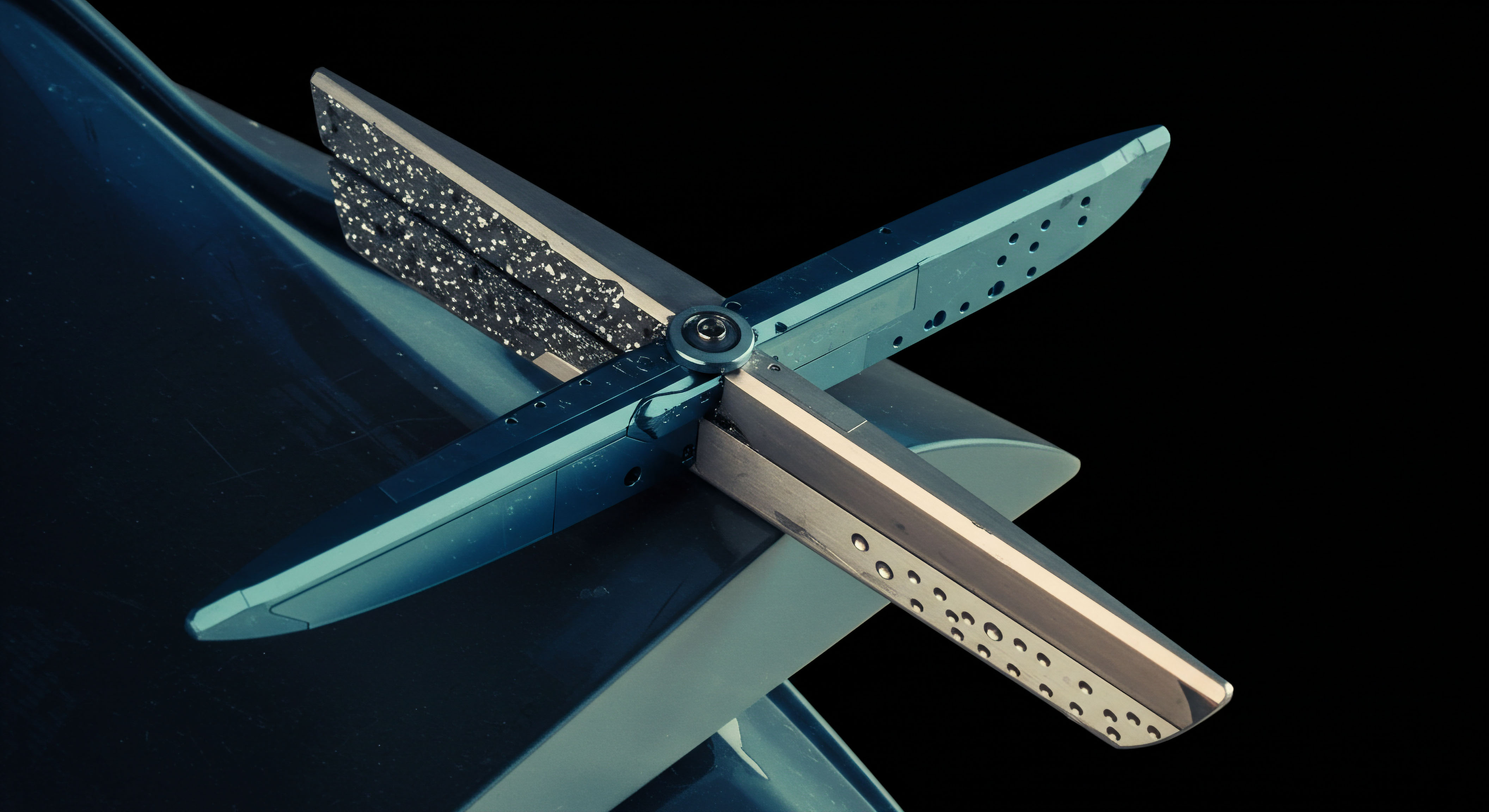

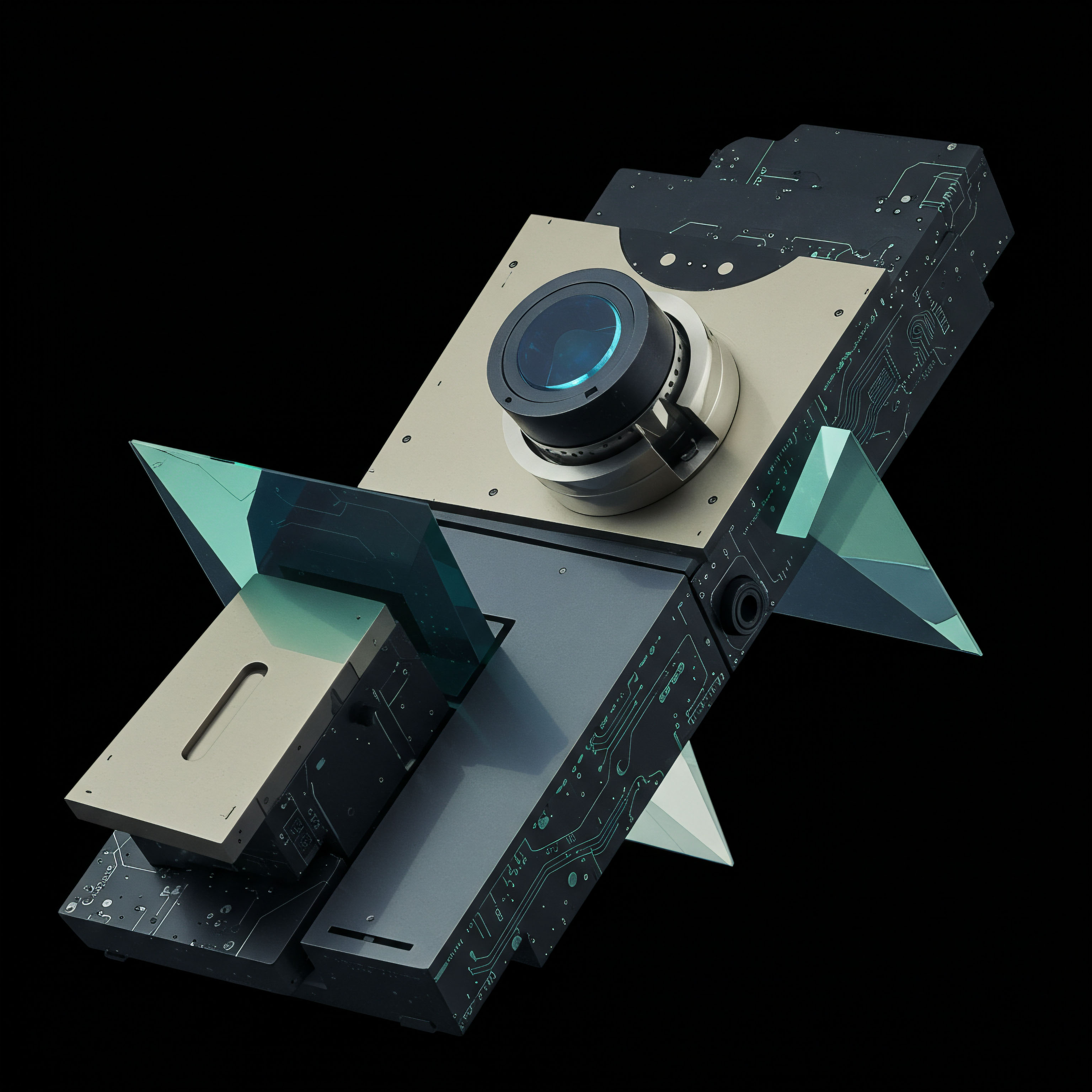

FPGA parallelism provides a direct and physical path to low jitter because it transforms a financial messaging task from a temporal sequence of instructions into a spatial arrangement of dedicated logic circuits. A general-purpose CPU processes tasks sequentially, contending for shared resources under the supervision of an operating system. This creates a cascade of potential delays from process scheduling, cache misses, and interrupts, all of which introduce unpredictable latency variations. An FPGA implements the entire processing pipeline ▴ from packet ingestion to risk analysis and order dispatch ▴ as a purpose-built digital circuit.

Each stage of the pipeline operates independently and simultaneously. Market data does not wait in a queue for a processor to become available; it flows through a dedicated, physical pathway of logic gates designed for one specific purpose. This spatial distribution of tasks is the core mechanism that translates directly to deterministic latency, which is the near-elimination of jitter.

The core value of an FPGA in financial messaging is its ability to convert software algorithms into dedicated hardware circuits, thereby achieving consistent, predictable processing times.

This architectural shift from software-based sequential processing to hardware-based parallel execution is the foundational reason for the technology’s adoption in latency-sensitive applications. The system’s reaction time becomes a physical property of the circuit’s design, not a variable outcome of a CPU’s dynamic workload. Consequently, for an identical input, an FPGA-based system will produce a response in a constant, measurable timeframe, every time.

This deterministic behavior is the antithesis of jitter. It provides the temporal certainty required for high-fidelity strategy execution, allowing quantitative models to operate on the assumption of a stable and predictable technological base.

Strategy

The strategic adoption of FPGAs in financial messaging systems is a direct response to the inherent limitations of CPU-based architectures in high-stakes environments. A CPU is a marvel of versatility, designed to handle a vast array of tasks. This versatility, however, is its primary weakness in applications demanding unwavering consistency.

The strategy of deploying an FPGA is to surgically replace the sources of non-determinism with a system that is, by its very nature, predictable. This involves a deep understanding of how and why a CPU introduces jitter.

The Sources of Non-Determinism in CPU Architectures

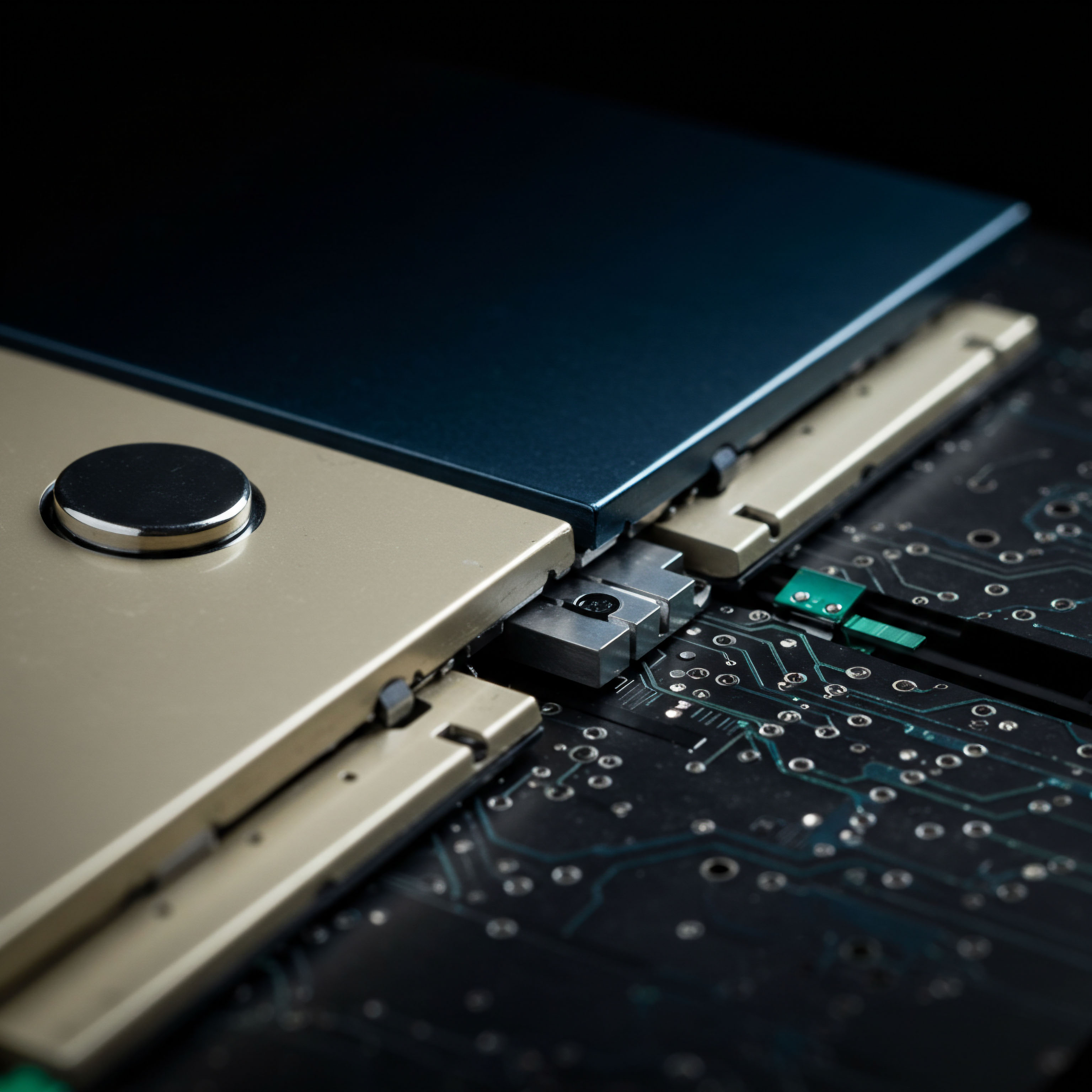

A CPU-based system is a layered environment of abstraction, with each layer contributing to potential latency variations. The operating system (OS) kernel, responsible for managing resources, is a primary source of jitter. It must perform context switching, pausing a trading application to allocate processing time to other system tasks. These interruptions, while lasting only microseconds, are asynchronous and unpredictable.

Further, memory access patterns contribute to inconsistency. A cache miss, where the CPU needs to fetch data from slower main memory instead of its high-speed cache, introduces a significant delay. The performance of a trading algorithm can therefore depend on the state of the cache at the moment of execution, which is a variable factor. Network packet processing through a standard OS kernel stack involves multiple memory copy operations and context switches between kernel space and user space, adding further overhead and variability.

Deploying FPGAs is a strategic decision to trade the versatility of CPUs for the absolute temporal predictability of custom hardware circuits.

The table below provides a strategic comparison of the processing paradigms, highlighting the architectural differences that lead to jitter.

| Processing Characteristic | CPU-Based System (High Jitter) | FPGA-Based System (Low Jitter) |

|---|---|---|

| Execution Model |

Sequential and temporal. Instructions are executed one after another, managed by a scheduler. |

Parallel and spatial. Operations occur simultaneously in dedicated logic blocks. |

| Resource Management |

Shared resources (cores, cache, memory bus) are contended for by multiple processes. |

Dedicated resources. Each function is implemented with its own logic, eliminating contention. |

| Operating System Overhead |

Significant jitter from context switching, interrupts, and kernel-level processing. |

No operating system in the data path. Logic is “bare metal.” |

| Data Path |

Data moves through multiple layers of software abstraction (application, libraries, kernel). |

Data flows through a single, optimized hardware circuit from input to output. |

| Determinism |

Inherently non-deterministic. Latency is a statistical distribution with a long tail. |

Inherently deterministic. Latency is a fixed property of the circuit design. |

How Does FPGA Parallelism Build a Deterministic System?

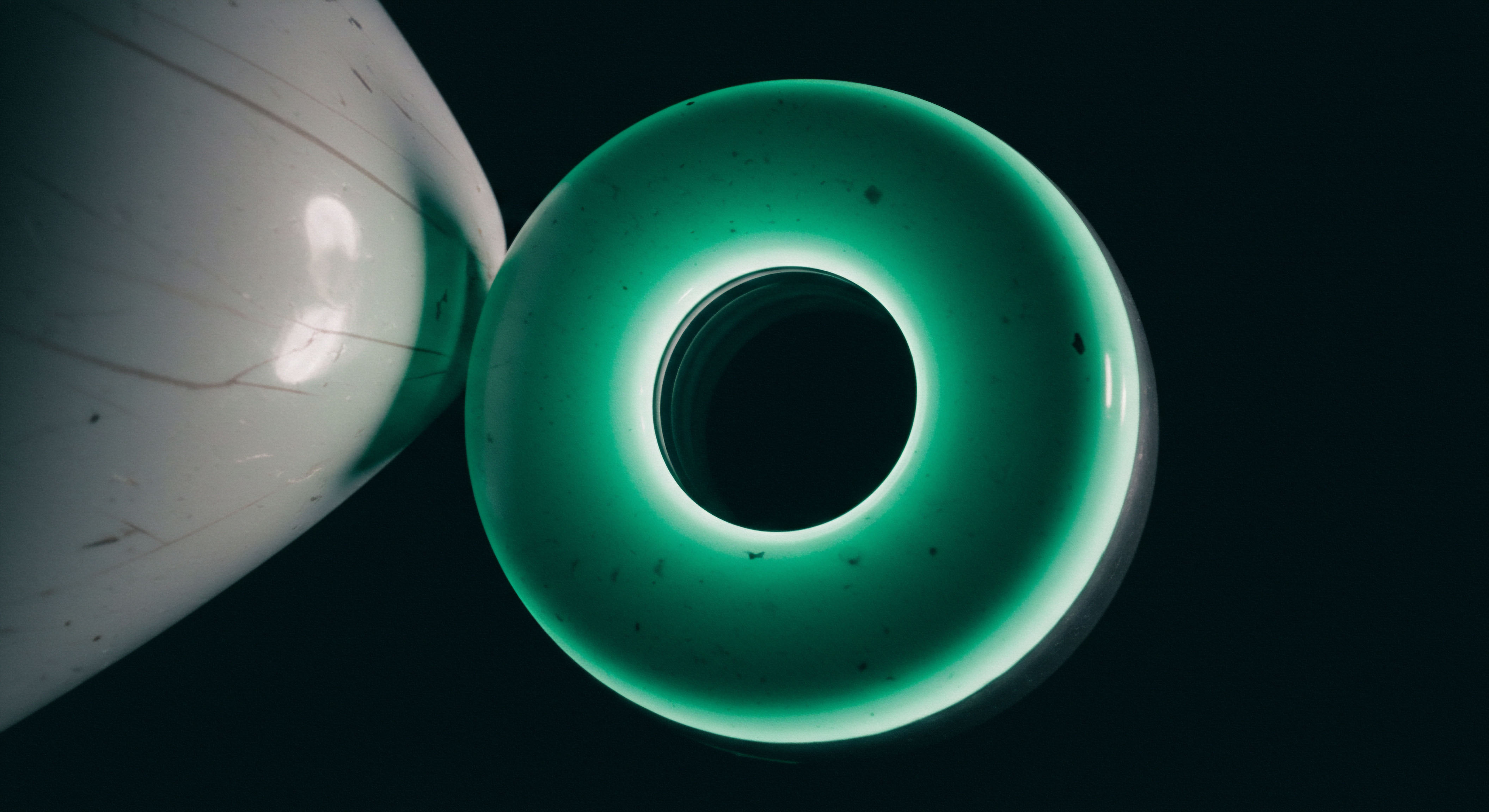

An FPGA strategy addresses each source of CPU jitter at a fundamental level. Instead of relying on an OS, the entire network stack can be implemented in hardware on the FPGA itself. This allows a market data packet to be processed directly from the wire without ever touching the server’s kernel, a technique known as kernel bypass. The different tasks within the financial messaging workflow are not assigned to a core; they are built as separate, parallel logic blocks on the chip.

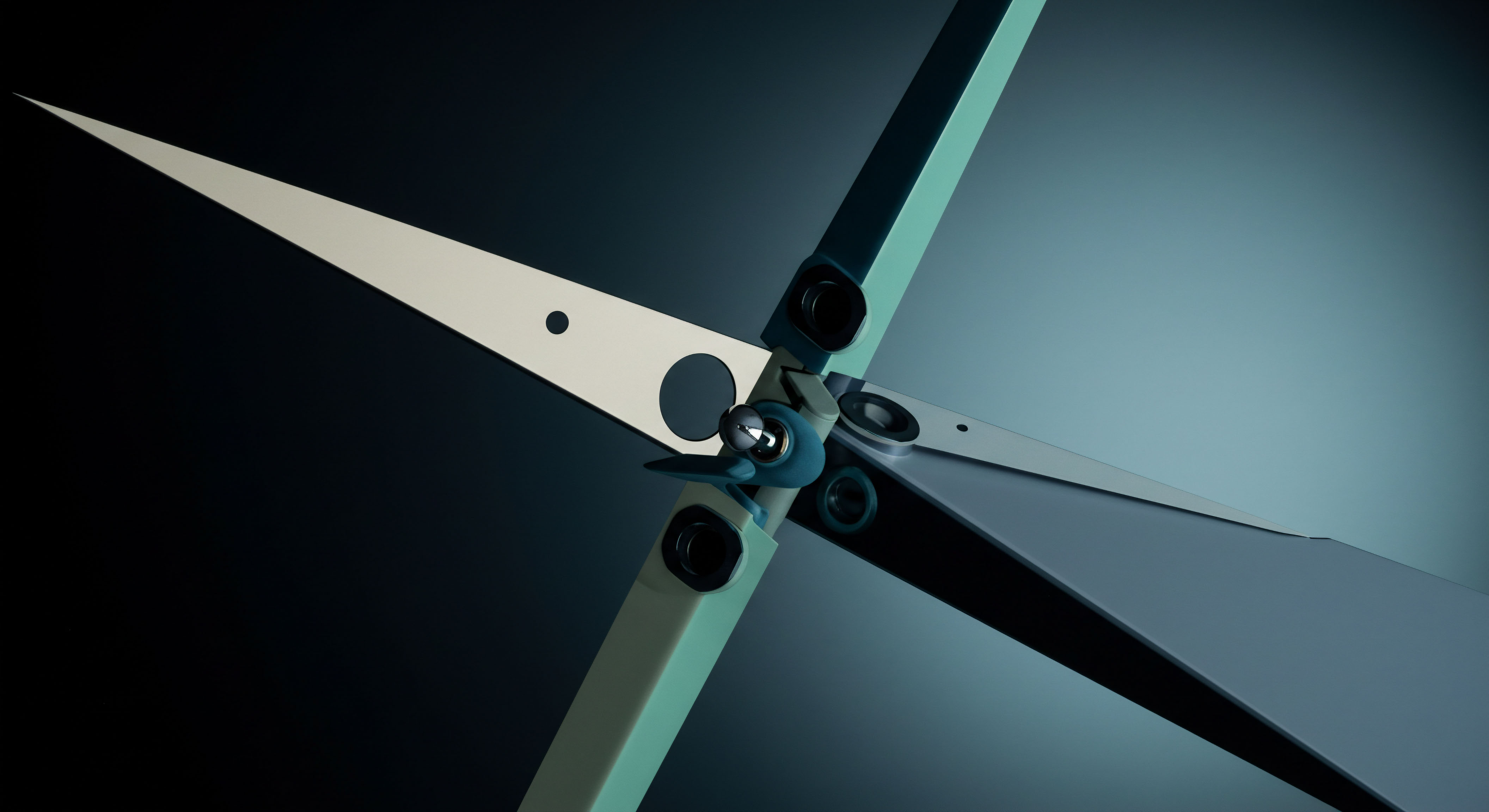

- Market Data Parsing A dedicated block of logic is synthesized to recognize and decode specific financial protocols like ITCH or FAST. It operates independently of any other function.

- Order Book Management Another circuit maintains the state of the order book, updating it as new messages arrive from the parser.

- Risk Analysis A parallel block performs pre-trade risk checks (e.g. fat-finger checks, position limits) on any potential outbound order.

- Order Generation A final block constructs the FIX message for an order and dispatches it to the network interface.

These blocks are connected in a pipeline. As a piece of data finishes processing in one block, it is immediately passed to the next, while the first block is already processing the subsequent piece of data from the market. This deep pipelining and parallelism mean that the system does not slow down under heavy load; it maintains a consistent throughput and latency, directly mitigating the primary cause of jitter.

Execution

Executing a low-jitter financial messaging system with FPGAs requires a shift in thinking from software development to digital circuit design. The objective is to construct a hardware architecture where every nanosecond of the tick-to-trade path is accounted for and optimized. This process involves mapping the logical steps of a trading application onto the physical resources of the FPGA fabric, creating a bespoke processor tailored specifically for the task.

Architecting the Tick-to-Trade Pipeline in Hardware

The execution begins with a granular decomposition of the messaging lifecycle. Each step is implemented as a distinct module within the FPGA design, operating in parallel. A typical high-performance pipeline would include the following stages, all implemented in hardware:

- Physical Layer Interface and MAC The process starts at the physical connection to the exchange. The FPGA’s high-speed transceivers connect directly to the network fiber. An integrated Ethernet Media Access Control (MAC) block handles the raw Layer 2 packet framing, providing wire-speed performance.

- Kernel-Bypass Network Stack A custom, lightweight TCP/IP or UDP stack is implemented directly in logic. This stack processes network packets in nanoseconds, identifying and filtering relevant market data or order acknowledgment streams without involving the host CPU’s slow, general-purpose network stack.

- Financial Protocol Parsing A dedicated parsing engine is designed for the specific exchange feed protocol (e.g. ITCH, SBE, FAST). This engine is a state machine that reads the incoming stream of bytes and extracts meaningful financial messages in a fixed number of clock cycles.

- Strategy and Risk Logic The core trading logic and pre-trade risk checks are synthesized into hardware. This could involve simple price comparisons for arbitrage or more complex calculations. Because it is a dedicated circuit, its execution time is constant and predictable.

- Order Execution and FIX Engine When the strategy logic decides to trade, it triggers an order generation module. This module constructs a Financial Information eXchange (FIX) message or a proprietary exchange order format and passes it back to the hardware network stack for immediate transmission.

This hardware-based execution model provides a stark contrast to a software-based approach, as detailed in the table below.

| Messaging Lifecycle Stage | Software Implementation (High Jitter) | FPGA Implementation (Low Jitter) |

|---|---|---|

| Packet Arrival |

Packet received by NIC, interrupt sent to CPU. Kernel copies packet to memory. |

Packet received by FPGA transceiver and processed directly in the hardware pipeline. |

| Protocol Decoding |

CPU runs a software function to parse the message, competing for core resources. |

Dedicated hardware parser decodes the message in a fixed number of clock cycles. |

| Decision Logic |

Trading algorithm runs as a process, subject to OS scheduling and cache state. |

Strategy logic executes as a combinatorial circuit with a fixed propagation delay. |

| Order Dispatch |

Software constructs an order, passes it to the kernel’s network stack for sending. |

Hardware FIX engine creates the packet and hands it directly to the hardware MAC for transmission. |

What Is the Quantifiable Impact of Jitter Reduction?

The primary benefit of deterministic execution is the reduction of execution uncertainty, which translates into improved fill rates and reduced slippage. In strategies that rely on capturing a small pricing discrepancy, jitter can be the difference between a profitable trade and a loss. A system with high jitter may see a price, but by the time the order reaches the exchange, the price has moved. An FPGA-based system, with its predictable latency, allows a firm to model its execution timeline with high precision.

This enables the trading strategy to account for its own latency, leading to more effective and reliable execution. The operational stability gained from low-jitter systems also simplifies risk management, as it removes a significant source of technological uncertainty from the overall trading equation.

In execution, FPGA parallelism transforms the probabilistic nature of software latency into the physical certainty of a hardware circuit’s timing.

This level of control is the ultimate goal of execution-focused engineering in finance. It allows the performance of the trading strategy to be a reflection of the model’s intelligence, isolated from the unpredictable behavior of the underlying technology.

References

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- Lockwood, John W. and Charles D. Jacobson. “FPGA-based TCP/IP and UDP/IP networking engines.” Proceedings of the 11th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, 2003.

- O’Hara, Maureen. Market Microstructure Theory. Blackwell Publishers, 1995.

- Gommans, L. et al. “A 2.5 Gb/s TCP/IP off-load engine in a reconfigurable platform.” Field-Programmable Logic and Applications ▴ 14th International Conference, FPL 2004, 2004.

- Weatherspoon, H. et al. “NetFPGA ▴ A tool for network research and education.” Proceedings of the 16th international conference on Computer communications and networks, 2007.

- Hutchings, Brad L. and R. J. Omondi. “A survey of FPGA-based network processing.” ACM Transactions on Reconfigurable Technology and Systems (TRETS), vol. 1, no. 1, 2008.

- Xilinx. “Accelerating Financial Applications with FPGAs.” Xilinx White Paper, WP483, 2017.

- Intel Corporation. “FPGAs for Low-Latency Trading.” Intel White Paper, 2019.

Reflection

The integration of FPGA technology into a financial architecture is a profound operational statement. It reflects a commitment to mastering the physical realities of time and data. The knowledge of this mechanism invites a deeper inquiry into your own systems. Where does uncertainty reside within your execution path?

Can you map every microsecond of your data’s journey from the market to your decision engine and back again? Is the latency of your system a stable, known constant, or is it a statistical distribution with a costly tail?

Viewing your technological framework through the lens of determinism reveals its true strength. A system that eliminates jitter is a system that provides a stable foundation upon which strategy can be built with confidence. The ultimate advantage is not just speed; it is the certainty that your system will perform exactly as designed, at the precise moment it matters most. This allows intellectual capital to be focused on market dynamics, liberated from the need to compensate for the unpredictable behavior of the underlying infrastructure.

Glossary

Jitter

Financial Messaging

Operating System

Deterministic Latency

Market Data

Fpga

Network Stack

Kernel Bypass