Concept

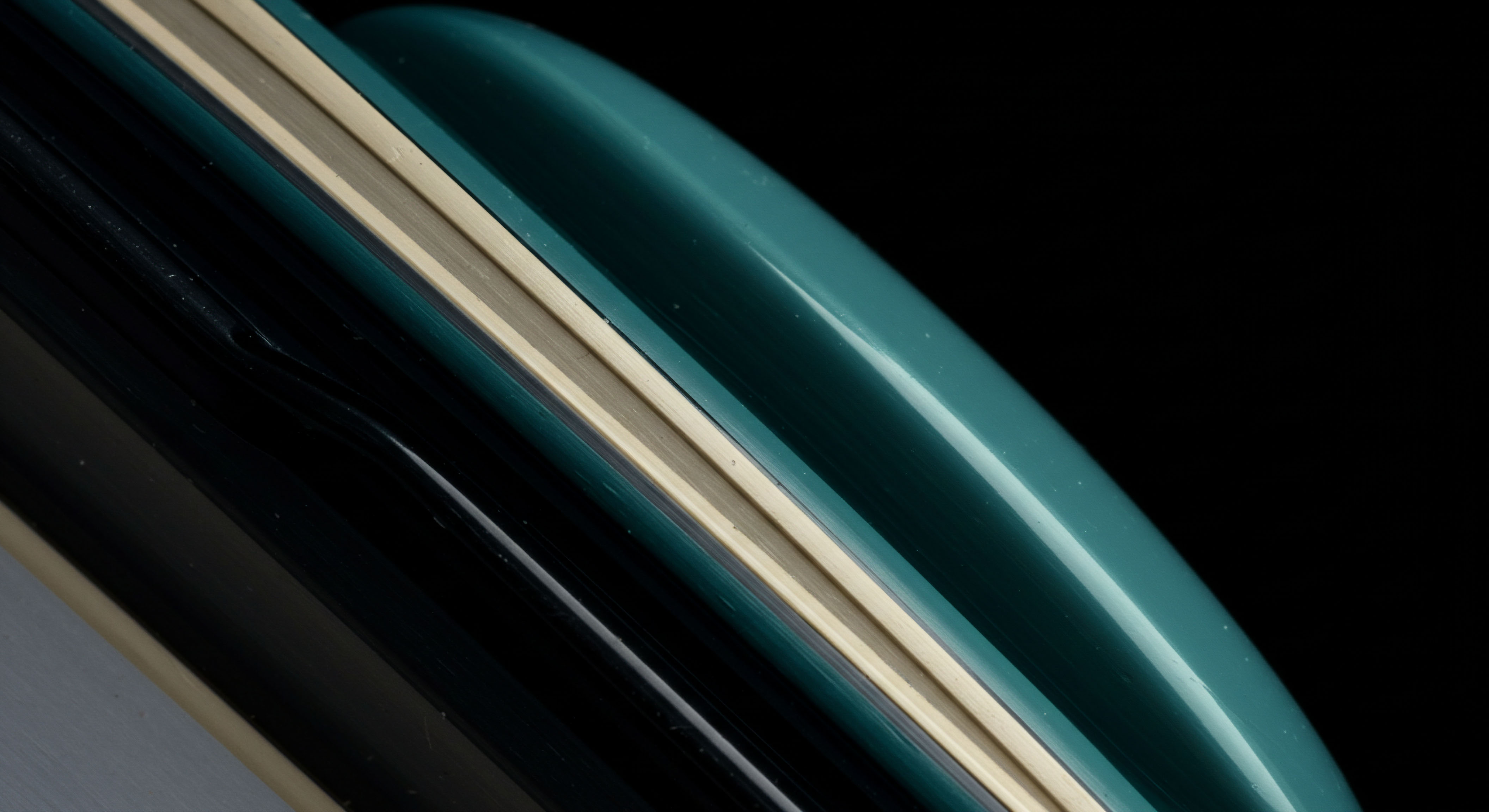

The implementation of hardware acceleration within a trading system directly confronts the foundational challenge of last look ▴ managing risk in the interval between seeing a price and accepting a trade. This mechanism is not about simply making decisions faster. It is a fundamental re-architecting of the decision-making process itself, shifting it from the probabilistic realm of software execution on general-purpose processors to the deterministic domain of silicon. When a liquidity provider’s system receives a request to trade at a quoted price, a clock starts.

This period, the ‘hold time’, represents a moment of maximum vulnerability. During these few microseconds, the market can move against the provider, a phenomenon known as adverse selection. A software-based system must contend with the inherent timing variability, or jitter, of a standard operating system, where other processes can introduce unpredictable delays. Hardware acceleration, typically through the use of Field-Programmable Gate Arrays (FPGAs), collapses this variability.

It allows the core logic of the last look decision ▴ validating the price against real-time market data and internal risk parameters ▴ to be etched directly into a circuit. The result is a system where the hold time becomes a predictable, repeatable, and drastically shorter constant. This transforms last look from a reactive risk-mitigation tool into a precision instrument for shaping liquidity.

Hardware acceleration provides a deterministic framework that minimizes the economic friction of adverse selection inherent in last look mechanisms.

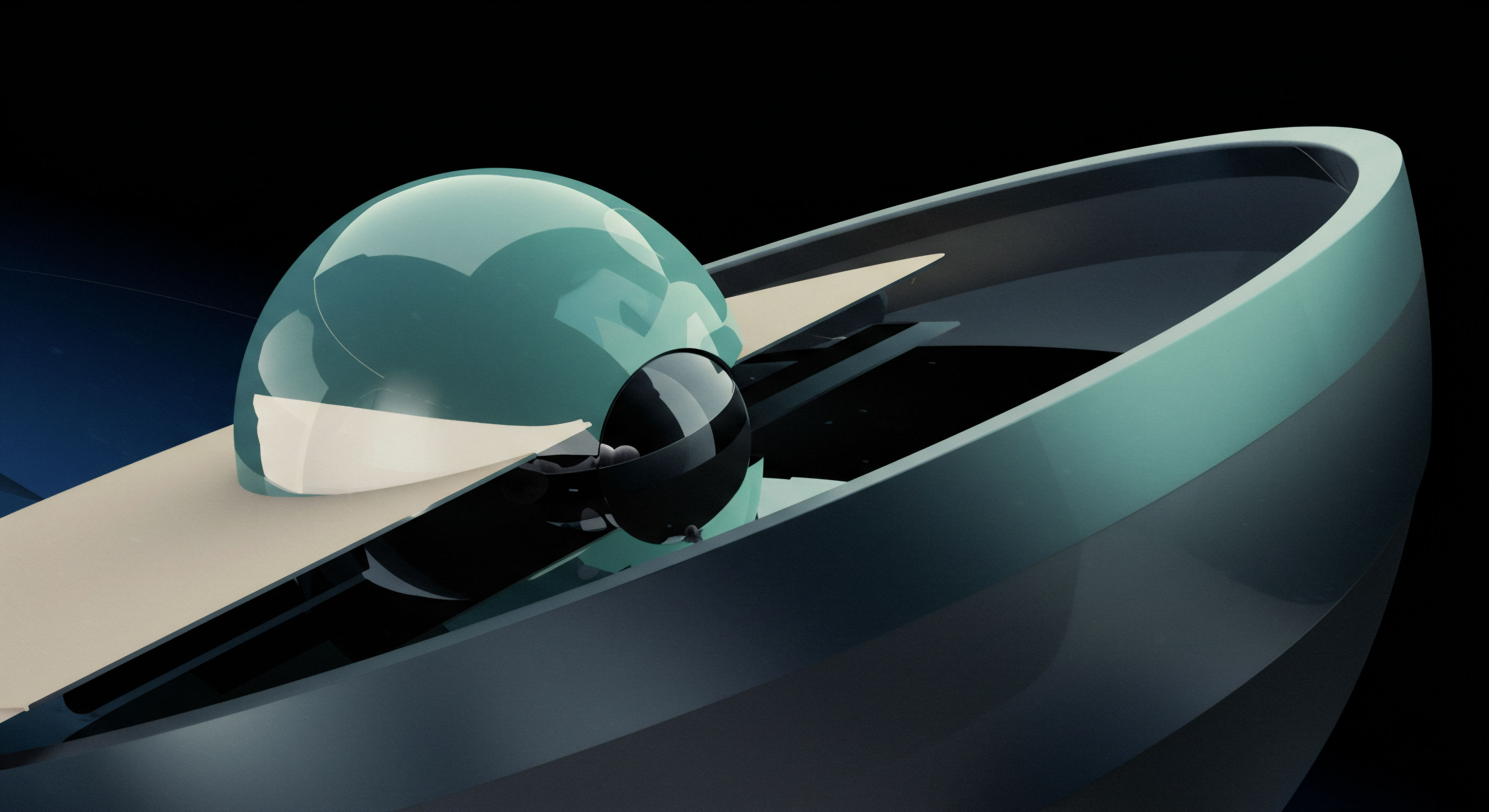

Understanding this transition requires a shift in perspective. The goal ceases to be merely reducing the average hold time. The primary objective becomes the elimination of outliers ▴ the unpredictable delays where the most significant losses from adverse selection occur. An FPGA-based system achieves this by performing critical tasks in parallel at the hardware level.

As network packets containing trade requests arrive, the hardware can begin parsing the message, checking it against risk limits, and comparing the requested price to a high-resolution feed of market data simultaneously. A software equivalent running on a CPU must perform these actions sequentially, subject to the scheduling whims of the operating system. This architectural difference is the source of the strategic advantage. It provides the liquidity provider with a higher degree of certainty about the state of the market at the moment of execution, allowing for more aggressive pricing and tighter spreads.

The system’s capacity to offer liquidity is enhanced because the risk associated with each quote is more precisely controlled. This control is a direct consequence of shrinking the window of uncertainty, a feat made possible by moving the decision logic from mutable software to immutable hardware.

Strategy

The strategic integration of hardware acceleration into a last look framework is a deliberate choice to weaponize time itself. It is an architectural commitment to reducing systemic friction and managing market risk at a granular level. For a liquidity provider, the duration of the last look hold time is a direct proxy for risk.

A longer hold time creates a larger surface area for adverse selection, where fast-acting counterparties can trade on information that has not yet been fully processed by the provider’s system. The core strategy is to compress this risk surface to its absolute minimum, thereby altering the economics of market making.

Redefining Risk and Opportunity

A conventional, software-based last look system operates with a degree of latency and, more importantly, variability (jitter). This uncertainty must be priced into the quotes offered to the market, resulting in wider spreads. Hardware acceleration, by providing ultra-low latency and deterministic processing, allows for a fundamental repricing of this risk. The strategic implication is twofold.

First, the provider can offer tighter spreads to liquidity takers, increasing its competitiveness and market share. Second, the provider can increase its fill rates, accepting a higher percentage of incoming orders with confidence because the risk of being adversely selected has been systematically reduced. The decision to invest in this technology is a calculated move to shift the firm’s operating model from one based on probabilistic risk management to one grounded in deterministic execution.

By minimizing the temporal gap between information and action, hardware acceleration allows a firm to externalize confidence and internalize risk control.

This strategic shift is best understood by comparing the two operational paradigms. A software-based system is akin to a highly skilled artisan; its performance is high but subject to variation based on workload and external factors. A hardware-accelerated system is an industrial automaton; its performance is precisely defined, repeatable, and operates at a speed and consistency unattainable by the former.

This allows the institution to build strategies that rely on this newfound predictability, such as offering more aggressive prices on larger order sizes or quoting more frequently in volatile market conditions. The technology becomes an enabler of business strategy, allowing the firm to capture opportunities that would be too risky to pursue with a slower, less predictable system.

How Does Determinism Alter Quoting Strategy?

A deterministic system provides a reliable upper bound on decision time. A market maker knows, with nanosecond precision, the maximum time it will take to process a trade request. This knowledge allows for a more aggressive quoting strategy. The “risk buffer” that was previously embedded in the spread to account for potential system delays can be significantly reduced.

This has a cascading effect on the entire trading operation. Tighter spreads attract more order flow, which in turn provides the market maker with more information about market sentiment. This information can then be used to refine pricing models further, creating a virtuous cycle of improved execution and increased profitability. The strategic deployment of hardware acceleration becomes a core component of the firm’s competitive moat.

Comparative Analysis of System Architectures

The choice between a software-based and a hardware-accelerated last look system is a choice between flexibility and raw performance. The following table illustrates the key differences from a strategic perspective:

| Metric | Software-Based System (CPU) | Hardware-Accelerated System (FPGA) |

|---|---|---|

| Decision Latency | Variable (tens of microseconds to milliseconds) | Deterministic (sub-microsecond to a few microseconds) |

| Execution Jitter | High (influenced by OS, other processes) | Minimal (nanosecond-level consistency) |

| Risk Management | Reactive (wider spreads to buffer for latency) | Proactive (tighter spreads due to predictable latency) |

| Adverse Selection Impact | Higher potential cost per trade | Systematically minimized cost per trade |

| Scalability Under Load | Performance degrades non-linearly | Consistent performance up to hardware limits |

| Development Cycle | Faster, more iterative (standard languages) | Longer, more specialized (requires hardware description languages) |

This comparison reveals the strategic trade-offs. While a software-based approach offers greater ease of development and modification, the hardware-accelerated path provides a durable performance advantage that directly translates into superior risk management and quoting capabilities. The investment in FPGA development is a capital expenditure that builds a long-term structural advantage in the market.

Execution

The execution of a hardware-accelerated last look system is an exercise in precision engineering. It involves the meticulous integration of specialized hardware, network infrastructure, and software logic to create a cohesive, high-performance trading apparatus. The ultimate goal is to shrink the hold time to a deterministic minimum, thereby providing the firm with a measurable edge in risk management and liquidity provision. This section details the operational protocols, quantitative models, and technological architecture required to achieve this.

The Operational Playbook for Integration

Deploying an FPGA-based last look system is a multi-stage process that requires careful planning and coordination across technology, trading, and risk management teams. The following steps outline a typical implementation path:

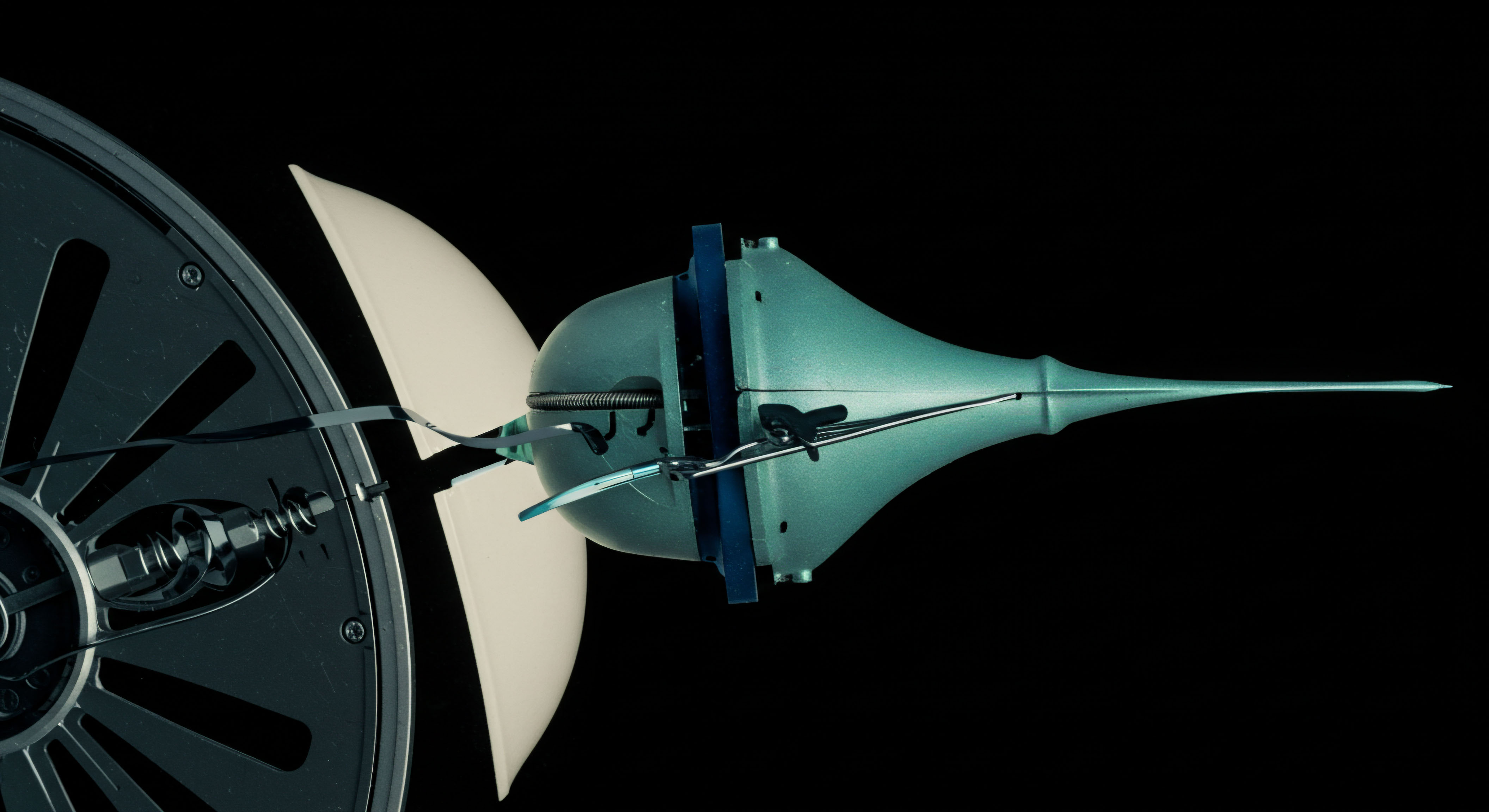

- System Architecture Design ▴ The initial phase involves defining the precise requirements of the system. This includes identifying the specific market data feeds to be processed, the complexity of the risk checks to be performed, and the communication protocols (such as FIX) to be used. The design must specify the exact logic to be offloaded to the FPGA versus what will remain in software.

- Hardware Selection and Procurement ▴ This step involves selecting the appropriate FPGA platform and specialized network interface cards (NICs). The choice of FPGA will depend on the complexity of the trading logic and the required processing power. The NICs must be capable of kernel bypass, allowing network packets to be delivered directly to the application (or FPGA) without involving the operating system’s network stack.

- FPGA Development and Verification ▴ This is the most resource-intensive phase. Engineers write the last look logic using a hardware description language (HDL) like Verilog or VHDL. This code is then synthesized into a circuit design that can be loaded onto the FPGA. Rigorous simulation and testing are performed to verify that the hardware logic is free of bugs and meets the specified latency targets.

- Co-location and Network Connectivity ▴ The physical placement of the hardware is paramount. The system must be housed in a co-location facility with the lowest possible latency to the trading venue’s matching engine. This involves securing rack space and establishing cross-connects to ensure the fastest possible transmission of data.

- Software Integration and Control ▴ A software layer is still required to manage the FPGA, load new trading logic, and provide a user interface for traders and risk managers. This software communicates with the FPGA over a high-speed bus (like PCIe) and is responsible for tasks that are less latency-sensitive, such as historical data logging and system monitoring.

- Live Testing and Phased Rollout ▴ Before being used for live trading, the system undergoes extensive testing in a simulated environment. Once validated, it is typically rolled out in phases, initially handling a small portion of the order flow and gradually scaling up as confidence in its performance and stability grows.

Quantitative Modeling of Latency Impact

The financial justification for investing in hardware acceleration rests on a quantitative understanding of how latency impacts profitability. The primary benefit is the reduction of adverse selection, also known as “P&L decay.” The following table models this relationship, showing how the cost of adverse selection increases as the last look hold time extends. The model assumes a simplified linear decay for illustrative purposes, though in reality, the relationship can be more complex.

| Hold Time (μs) | Probability of Adverse Market Move | Expected P&L Decay per Trade ($) | Cumulative Impact over 1M Trades ($) |

|---|---|---|---|

| 0.5 (FPGA) | 0.01% | $0.05 | $50,000 |

| 1.0 (FPGA) | 0.02% | $0.10 | $100,000 |

| 5.0 (Optimized Software) | 0.10% | $0.50 | $500,000 |

| 20.0 (Standard Software) | 0.40% | $2.00 | $2,000,000 |

| 100.0 (Software with Jitter) | 2.00% | $10.00 | $10,000,000 |

The model uses the formula ▴ Expected P&L Decay = (Base Tick Size) (Probability of Adverse Market Move). This quantification makes the abstract concept of “speed” tangible. A reduction in hold time from 20 microseconds to 1 microsecond represents a 95% reduction in the expected cost of adverse selection on each trade. For a high-volume market maker, this translates into millions of dollars in preserved revenue over time.

What Is the True Cost of Jitter?

While average latency is a useful metric, the true silent killer of profitability is jitter ▴ the variability in latency. A system with a low average latency but high jitter is unpredictable. It might process 99% of trades within an acceptable window but take significantly longer on the 1% of trades that are most likely to be informed and adversely selected.

Hardware acceleration’s primary benefit is the near-elimination of jitter, providing a deterministic upper bound on processing time. This ensures that even the most information-rich trades are handled within the firm’s risk tolerance, preventing the outsized losses that can occur during moments of high system load or market volatility.

System Integration and Technological Architecture

The hardware-accelerated last look system is a highly specialized piece of infrastructure. Its architecture is designed for one purpose ▴ to make a rapid, deterministic decision. The key components of this architecture are detailed below.

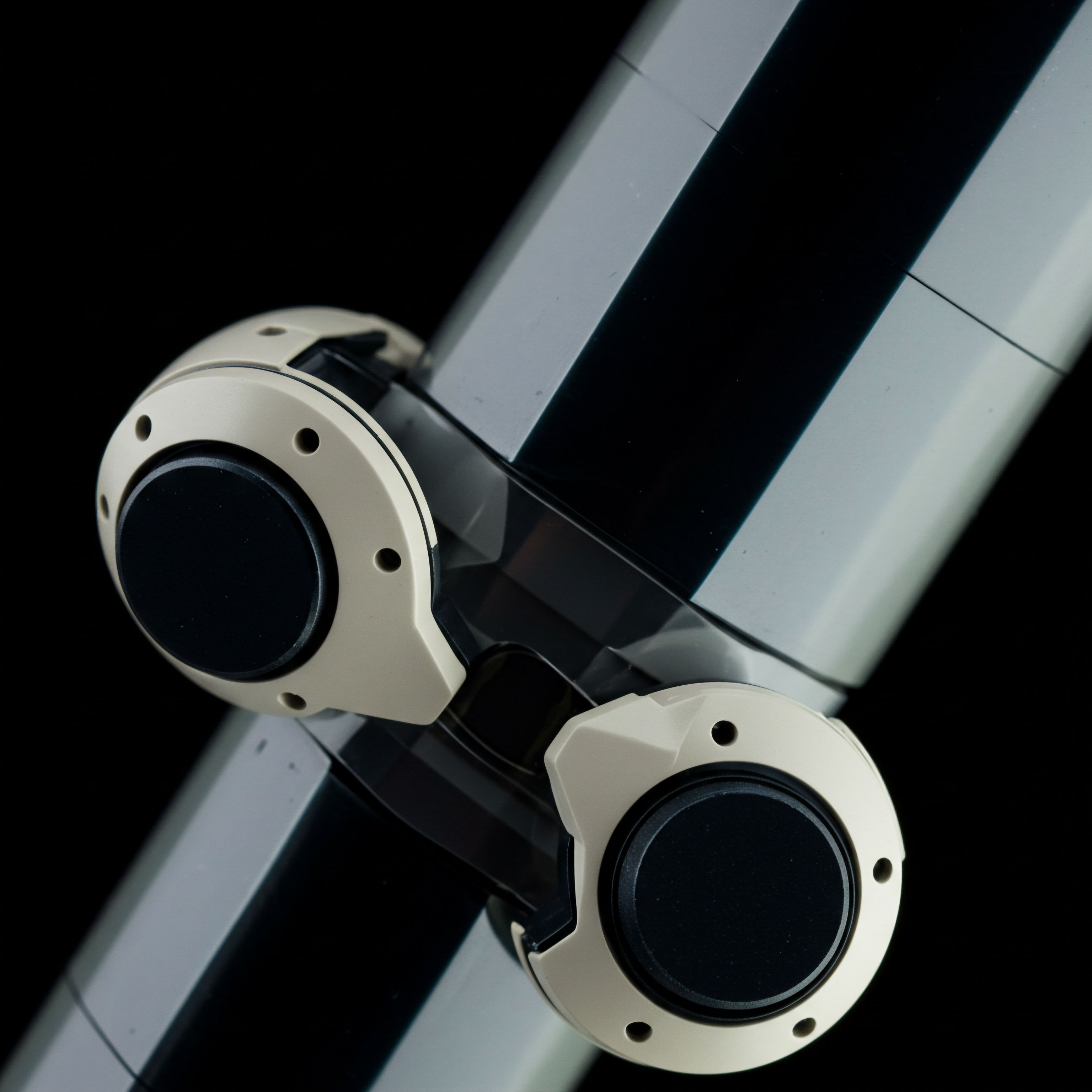

- Field-Programmable Gate Array (FPGA) ▴ The core of the system. The FPGA is programmed with the specific logic for parsing incoming trade requests (e.g. FIX messages), checking against market data, and applying risk rules. Its parallel processing capabilities allow these tasks to occur simultaneously.

- Low-Latency Network Interface Card (NIC) ▴ A specialized NIC that supports kernel bypass technologies. This allows network packets to be moved directly from the network wire to the FPGA, avoiding the latency overhead of the operating system’s networking stack.

- High-Precision Clock Synchronization ▴ The entire system must be synchronized to a high-precision time source, typically using the Precision Time Protocol (PTP). This ensures that timestamps are accurate to the nanosecond level, which is critical for accurate latency measurement and regulatory reporting (e.g. MiFID II).

- Onboard Memory (SRAM) ▴ The FPGA utilizes high-speed static RAM to store critical data, such as risk limits and real-time market price information. The speed of this memory is a key factor in achieving low-latency decision-making.

- PCIe Interface ▴ A high-speed Peripheral Component Interconnect Express bus connects the FPGA card to a host server. This interface is used by the software layer to configure the FPGA, receive status updates, and handle any exceptions or complex trades that are passed up from the hardware.

The integration of these components creates a system where the critical path for a last look decision never touches a general-purpose CPU. The journey of a trade request flows from the network, directly into the FPGA for a decision, and back out to the network. This streamlined path is what delivers the determinism and ultra-low latency that provide a sustainable competitive advantage in modern electronic markets.

References

- Harris, Larry. “Trading and Exchanges ▴ Market Microstructure for Practitioners.” Oxford University Press, 2003.

- O’Hara, Maureen. “Market Microstructure Theory.” Blackwell Publishers, 1995.

- Lehalle, Charles-Albert, and Sophie Laruelle, editors. “Market Microstructure in Practice.” World Scientific Publishing, 2018.

- Narayan, R. & Zervoudakis, K. (2019). “FPGA-based High-Frequency Trading Systems ▴ A Survey.” ACM Computing Surveys (CSUR), 52(4), 1-37.

- Budish, E. Cramton, P. & Shim, J. (2015). “The High-Frequency Trading Arms Race ▴ Frequent Batch Auctions as a Market Design Response.” The Quarterly Journal of Economics, 130(4), 1547-1621.

- Hasbrouck, Joel. “Empirical Market Microstructure ▴ The Institutions, Economics, and Econometrics of Securities Trading.” Oxford University Press, 2007.

- Lockwood, J. & Gupte, A. (2016). “Accelerating Financial Applications with FPGAs.” IEEE Micro, 36(3), 12-21.

- Moallemi, C. C. (2017). “Optimal Execution with a Last Look.” Working Paper, Columbia University.

- Guo, M. & Zou, J. (2018). “Latency, Liquidity, and Market Making.” Journal of Financial Markets, 41, 46-64.

Reflection

The integration of hardware acceleration into the architecture of market making represents a fundamental evolution in the control of financial risk. The principles discussed here extend beyond the specific mechanism of last look. They prompt a deeper consideration of a firm’s entire operational framework. The capacity to engineer determinism into a system that interfaces with a probabilistic world is a powerful strategic asset.

It compels a re-evaluation of where, within the technological stack, critical decisions should be made. As you assess your own systems, consider the points of friction, the sources of unpredictability, and the windows of uncertainty. The pursuit of a superior operational edge is a continuous process of identifying these vulnerabilities and architecting solutions that provide not just speed, but certainty. The true value of this technology lies in the confidence it provides to act decisively in moments of opportunity.

Where Else Can Determinism Create an Edge?

The application of hardware-level determinism is not confined to last look. Its principles can be applied to other latency-sensitive operations, such as pre-trade risk checks, smart order routing, and the real-time calculation of derivatives pricing. Each of these areas contains its own “hold time,” a period of risk between data receipt and action.

By systematically identifying and compressing these periods, a firm can build a more robust and resilient trading enterprise. The ultimate goal is to construct a system where technology serves as a stable foundation upon which complex and profitable trading strategies can be confidently built and executed.

Glossary

Hardware Acceleration

Last Look

Adverse Selection

Hold Time

Market Data

Fpga

Tighter Spreads

Last Look Hold Time

Latency

Jitter

Deterministic Execution

Risk Management

Liquidity Provision

Kernel Bypass