The Imperative of Speed in Market Dynamics

For any principal operating within the volatile expanse of digital asset derivatives, the swiftness of action dictates the very contours of opportunity and exposure. Quote cancellation latency, a metric often overlooked by less sophisticated market participants, represents a critical determinant of operational efficacy. Its impact reverberates across a firm’s entire trading lifecycle, influencing everything from the integrity of a market-making book to the precise execution of a complex arbitrage strategy. Understanding this latency begins with recognizing its constituent elements, which collectively form a sequence of events, each susceptible to technological optimization.

The journey of a quote cancellation instruction commences at the trader’s system, traversing internal networks, undergoing processing by decision-making logic, and ultimately reaching the exchange’s matching engine. Each segment of this journey introduces a delay, a fraction of time where market conditions may diverge from the initial assumptions underpinning the quote. Hardware acceleration fundamentally reshapes this temporal landscape. It transforms sequential software operations into parallel, purpose-built electronic pathways, thereby collapsing the time required for a cancellation order to be generated, transmitted, and acknowledged by the venue.

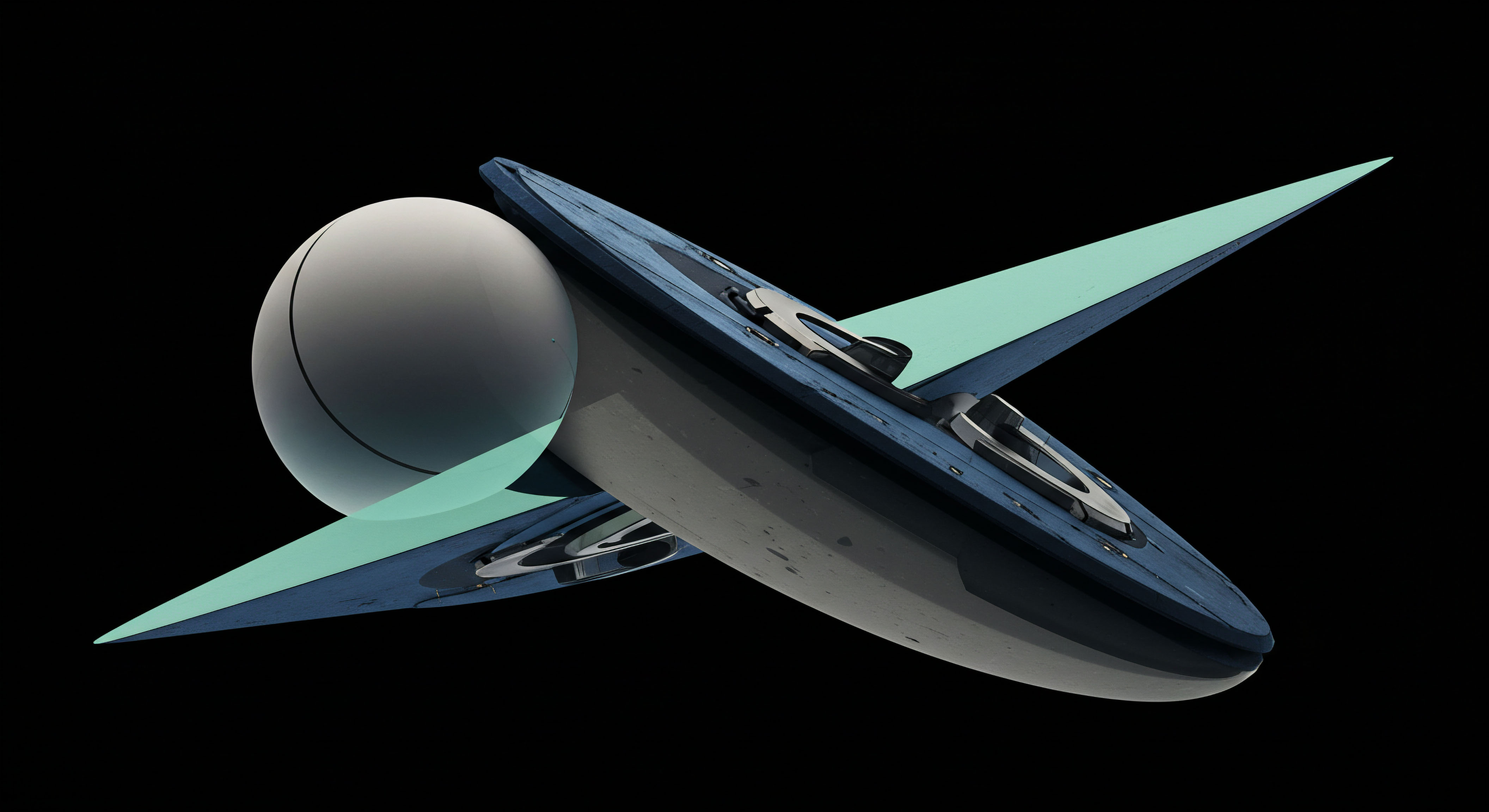

Hardware acceleration fundamentally reshapes the temporal landscape of quote cancellation, converting sequential software operations into parallel electronic pathways.

The profound effect of this acceleration extends beyond mere speed; it introduces a new dimension of control. Market participants gain the ability to react with unparalleled agility to incoming market data, to swiftly withdraw stale quotes, and to recalibrate their exposure in microseconds. This enhanced responsiveness translates directly into superior execution quality, reduced adverse selection, and a more robust management of inventory risk. The pursuit of minimal cancellation latency thus constitutes a foundational objective for any institution seeking a decisive edge in today’s electronically driven markets, particularly where price discovery unfolds at an unrelenting pace.

Strategic Advantage through Temporal Compression

The strategic imperative for embracing hardware acceleration in the context of quote cancellation latency stems from its capacity to fundamentally alter the competitive equilibrium within institutional trading. Firms that command superior temporal compression capabilities gain a distinct, often asymmetric, advantage. This capability allows for a more dynamic engagement with market microstructure, enabling the deployment of strategies that are simply untenable with conventional software-centric processing.

One primary strategic benefit lies in the realm of market making. An institutional market maker thrives on providing liquidity while carefully managing inventory risk. When market conditions shift rapidly, the ability to cancel outstanding quotes with minimal latency becomes paramount.

This swift withdrawal capability protects against adverse selection, a scenario where a market maker’s stale quotes are filled at prices that no longer reflect the prevailing market consensus, resulting in immediate losses. Hardware acceleration mitigates this risk, permitting the continuous recalibration of bid and offer prices with a precision that outpaces competitors reliant on slower processing paradigms.

Superior temporal compression capabilities offer a distinct, often asymmetric, advantage in institutional trading.

Furthermore, hardware acceleration profoundly influences arbitrage strategies. Inter-exchange arbitrage, for instance, demands the simultaneous execution of trades across multiple venues to capitalize on fleeting price discrepancies. The ability to cancel an order on one exchange with near-instantaneous speed, should the arbitrage opportunity vanish or reverse, safeguards capital and prevents unintended directional exposure. This temporal precision enhances the robustness of these strategies, allowing for higher frequency deployment and tighter profit margins.

From a broader capital efficiency perspective, reducing quote cancellation latency optimizes the utilization of trading capital. Capital deployed in outstanding quotes remains exposed to market fluctuations. By minimizing the duration of this exposure through accelerated cancellation, firms can free up capital more quickly, redeploying it into new opportunities or reducing overall margin requirements. This translates into a more efficient capital allocation model, enhancing overall return on capital.

Regulatory compliance also enters this strategic calculus. As market surveillance intensifies, demonstrating the capacity for orderly market participation, including the prompt cancellation of erroneous or unwanted orders, gains increasing importance. Hardware-accelerated systems inherently support this objective through their deterministic and high-speed operational profiles.

The strategic deployment of hardware acceleration, therefore, transcends a simple pursuit of speed; it represents a foundational investment in operational resilience, risk management, and the persistent generation of alpha in an increasingly competitive landscape. Firms evaluate these technological advancements through a lens of total cost of ownership, weighing the initial investment against the long-term gains in execution quality, reduced slippage, and enhanced strategic optionality. The strategic choice becomes clear ▴ to lead in market dynamics, one must first master the dimension of time.

Precision Execution in the Microsecond Domain

The operational protocols governing quote cancellation in ultra-low latency environments demand an intricate interplay of specialized hardware and meticulously engineered software. Execution excellence in this domain hinges on the deployment of technologies that can process, decide, and transmit information at speeds approaching the theoretical limits of physics. This requires a departure from general-purpose computing architectures towards purpose-built solutions designed for deterministic, high-throughput processing.

Hardware Acceleration Technologies and Their Impact

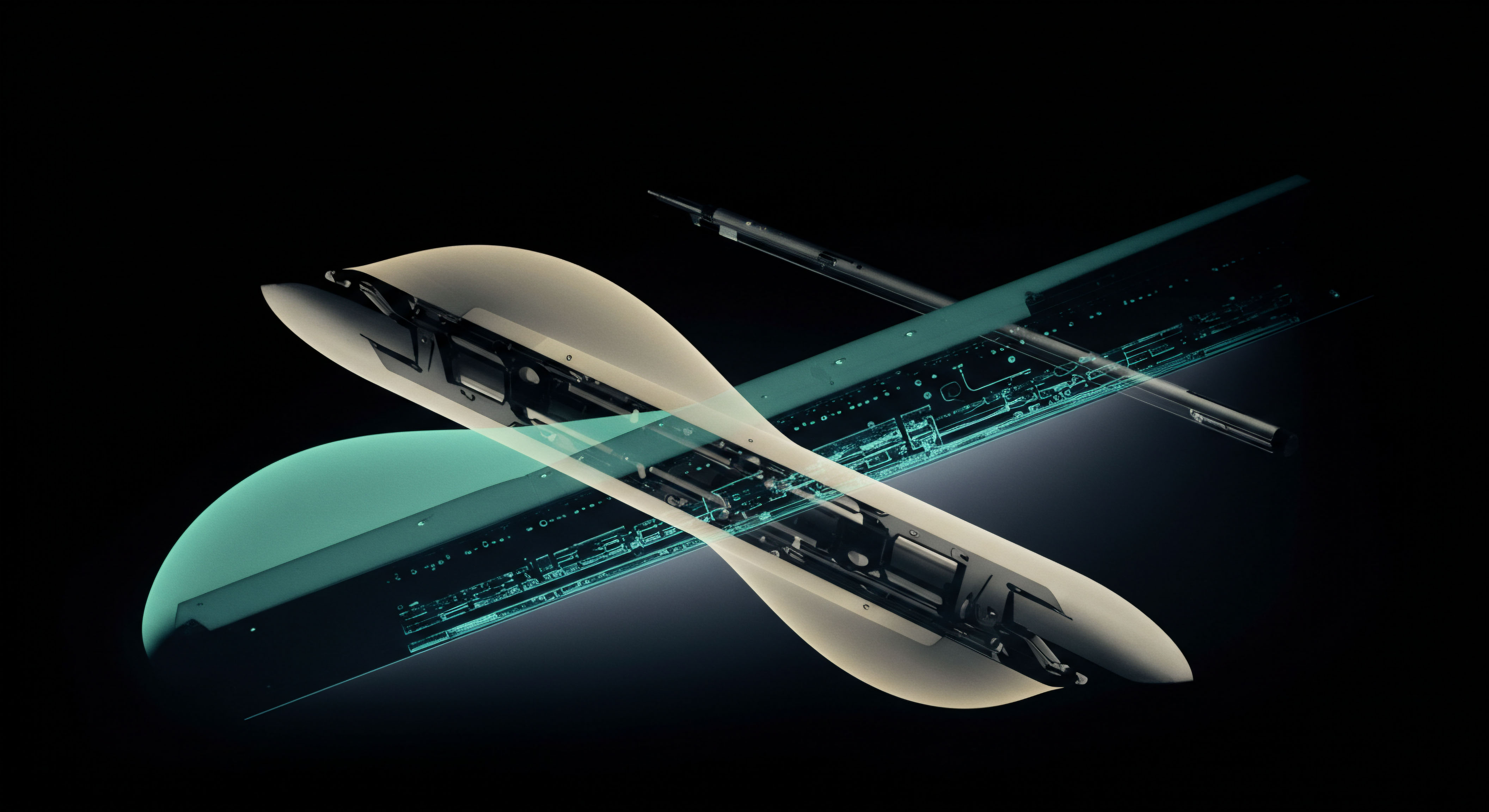

The primary technologies driving this temporal compression include Field-Programmable Gate Arrays (FPGAs), Application-Specific Integrated Circuits (ASICs), and highly optimized network interface cards (NICs). Each plays a distinct role in reducing the end-to-end latency of a cancellation instruction.

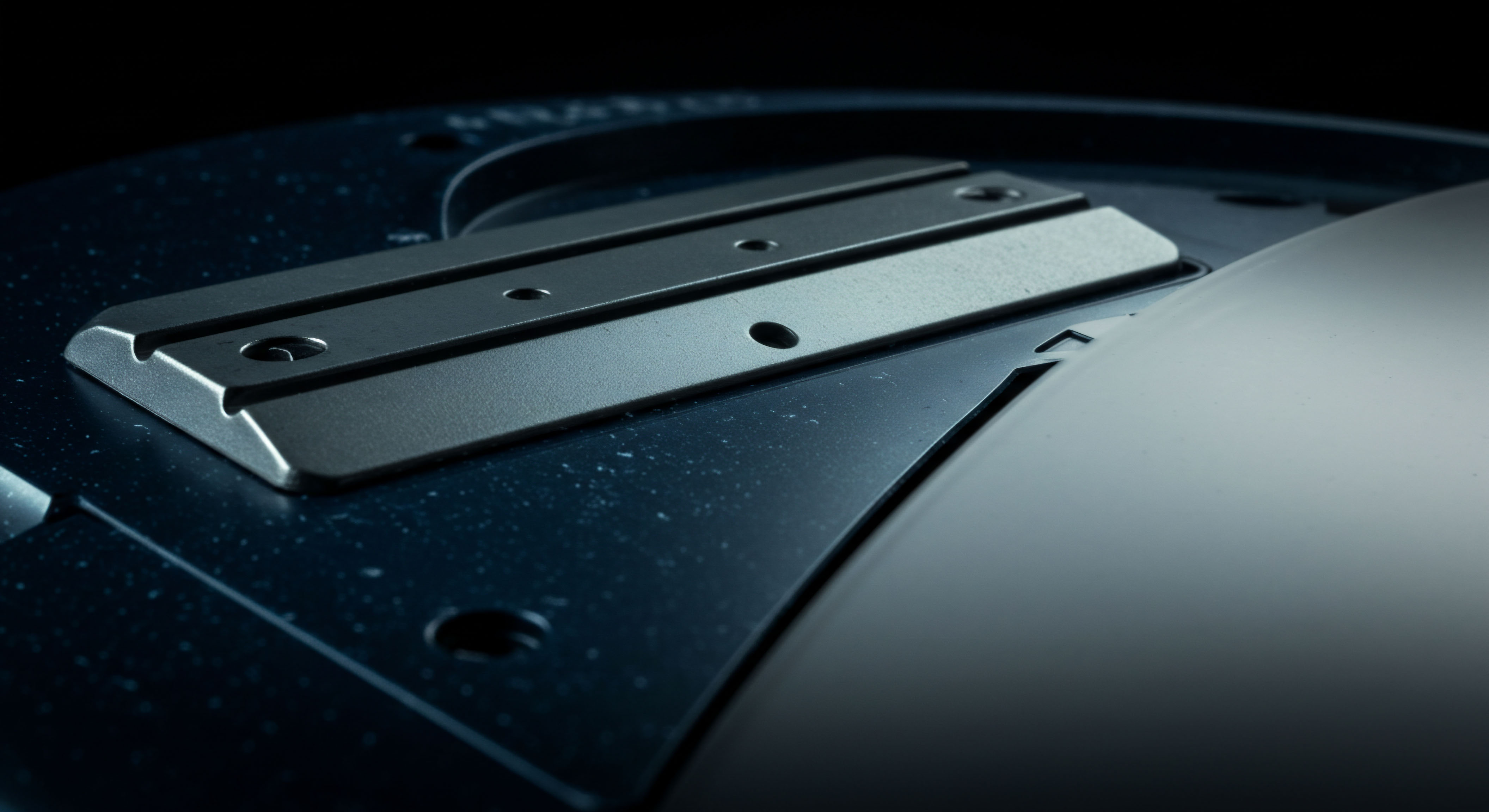

- FPGAs ▴ These reconfigurable silicon chips allow for custom logic circuits to be programmed directly onto the hardware. This bypasses the overhead inherent in software execution on a CPU, such as operating system calls, memory access arbitration, and instruction pipeline stalls. For quote cancellation, FPGAs excel at tasks like market data parsing, order book management, and the rapid generation of cancellation messages based on pre-defined rules. Their parallel processing capabilities ensure that multiple operations can occur concurrently, drastically reducing decision latency.

- ASICs ▴ Representing the pinnacle of hardware acceleration, ASICs are custom-designed chips built for a specific function. While their development cost is higher, their performance in terms of latency and power efficiency is unmatched for highly stable, critical functions. An ASIC designed for quote cancellation might encapsulate the entire logic for identifying stale quotes and initiating their withdrawal, delivering cancellation instructions with picosecond precision.

- Optimized NICs ▴ Specialized network interface cards integrate logic for direct memory access (DMA) and kernel bypass, allowing cancellation messages to enter the network stack with minimal software intervention. These NICs often incorporate hardware time-stamping and flow steering capabilities, ensuring that cancellation packets are prioritized and delivered with the utmost expediency to the exchange’s matching engine.

The cumulative effect of these technologies is a profound reduction in the overall quote cancellation latency, measured in single-digit microseconds or even nanoseconds, a stark contrast to the tens or hundreds of microseconds typical of purely software-driven systems.

Quantitative Modeling and Data Analysis

Quantifying the impact of hardware acceleration on cancellation latency necessitates rigorous measurement and modeling. Firms employ sophisticated telemetry systems to capture timestamp data at various points within the trading pipeline, from the moment a cancellation decision is made to its acknowledgment by the exchange. This data then undergoes detailed statistical analysis to identify bottlenecks and validate performance improvements.

Consider the following hypothetical data illustrating the latency reduction across different stages of a cancellation workflow:

| Cancellation Stage | Software-Only Latency (µs) | FPGA-Accelerated Latency (µs) | ASIC-Accelerated Latency (µs) | Reduction (FPGA vs. Software) | Reduction (ASIC vs. Software) |

|---|---|---|---|---|---|

| Market Data Ingress & Parsing | 5.2 | 0.8 | 0.3 | 84.6% | 94.2% |

| Decision Logic Execution | 8.7 | 1.5 | 0.5 | 82.8% | 94.3% |

| Order Message Construction | 3.1 | 0.6 | 0.2 | 80.6% | 93.5% |

| Network Egress & Transmission | 2.8 | 0.5 | 0.2 | 82.1% | 92.9% |

| Total End-to-End Latency | 19.8 | 3.4 | 1.2 | 82.8% | 93.9% |

The data clearly illustrates the exponential gains achievable through hardware-centric designs. The percentage reduction is calculated as (Software Latency – Accelerated Latency) / Software Latency 100. These reductions compound across the entire processing chain, leading to a substantial decrease in overall latency. Advanced statistical models, such as extreme value theory, are applied to analyze the tail latencies, as even infrequent spikes in cancellation time can lead to significant adverse selection events.

Predictive Scenario Analysis

Imagine a scenario unfolding in the Bitcoin options market during a period of heightened volatility. A proprietary trading firm, “Aether Capital,” operates a sophisticated market-making strategy on a major derivatives exchange. Aether’s system maintains a tight bid-offer spread on a range of BTC call and put options, continuously updating quotes in response to order flow and underlying spot price movements. Their legacy software-only infrastructure typically exhibits an average quote cancellation latency of 18 microseconds, with occasional spikes reaching 50 microseconds during peak market activity.

This latency, while seemingly minuscule, leaves them vulnerable to adverse selection. For instance, if the underlying Bitcoin price suddenly drops by 0.5% in a 20-microsecond window, Aether’s system might still have stale buy orders (puts) or sell orders (calls) at prices that no longer reflect the new market reality. A fast-moving arbitrageur could then “pick off” these stale quotes, executing against Aether’s unfavorable prices before their cancellation messages propagate through the network and are processed by the exchange. Over a high-volume trading day, these “picking off” events could erode a significant portion of their potential profits, manifesting as unexpected inventory imbalances or direct losses on executed trades.

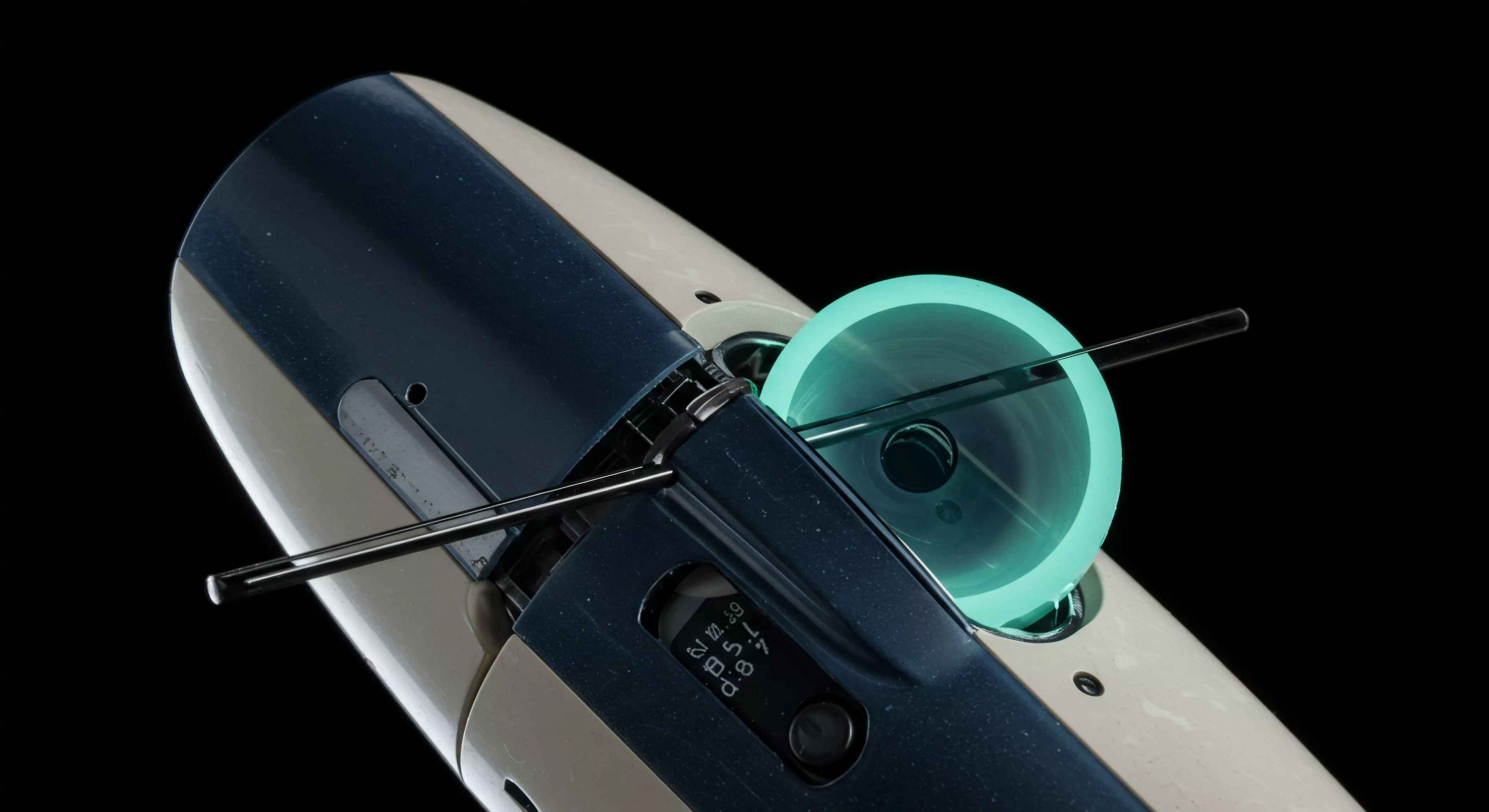

Recognizing this systemic vulnerability, Aether Capital invests in a hardware-accelerated platform, deploying FPGAs for market data parsing and decision logic, coupled with optimized NICs for network ingress and egress. Following implementation, their average quote cancellation latency drops to a consistent 3 microseconds, with tail latencies rarely exceeding 7 microseconds, even during periods of extreme market stress. This dramatic reduction transforms their operational capabilities. In a similar sudden 0.5% Bitcoin price drop, Aether’s hardware-accelerated system can now detect the price movement, re-evaluate its quotes, and issue cancellation instructions within a 3-microsecond window.

This means that by the time an arbitrageur attempts to capitalize on the price dislocation, Aether’s stale quotes are already withdrawn or updated, effectively closing the window for adverse selection. The firm experiences a noticeable reduction in unexpected losses from “picked off” trades and a significant improvement in its realized spread capture. Their inventory management becomes tighter, requiring less capital to be held as a buffer against potential market moves. The system’s ability to react almost instantaneously to changes in implied volatility, for example, allows Aether to adjust its options pricing models with unprecedented speed, ensuring their quotes remain competitive yet protected.

The hardware acceleration thus empowers Aether Capital to operate with a level of precision and risk control that was previously unattainable, solidifying their position as a dominant liquidity provider in the highly competitive digital asset options landscape. The competitive landscape itself shifts, as firms without such acceleration find themselves increasingly marginalized, unable to compete on speed and efficiency. Aether’s ability to cancel orders rapidly provides a crucial defensive mechanism, safeguarding their capital and ensuring the integrity of their trading strategies against the relentless pace of electronic markets.

System Integration and Technological Architecture

The integration of hardware acceleration into a comprehensive trading system requires a holistic approach to technological architecture. This involves meticulous design across several layers, ensuring seamless communication and minimal latency at every juncture.

- Physical Layer Optimization ▴ This begins with colocation in proximity to exchange matching engines, minimizing fiber optic cable lengths. The choice of networking equipment, including ultra-low latency switches, is paramount.

- Data Path Design ▴ The architectural blueprint prioritizes a direct, low-overhead data path for critical market data and order messages. This often involves kernel bypass techniques, where network packets are routed directly to user-space applications or FPGA logic, circumventing the operating system’s kernel entirely.

- Time Synchronization ▴ Precision Time Protocol (PTP) is essential for synchronizing all components of the trading system, ensuring accurate timestamping of events and consistent decision-making across distributed hardware. A microsecond discrepancy in timing can invalidate the benefits of hardware acceleration.

- API and Protocol Integration ▴ Cancellation instructions are typically conveyed via established financial protocols, such as FIX (Financial Information eXchange). Hardware-accelerated systems incorporate dedicated FIX engines implemented in FPGA logic, parsing incoming messages and constructing outgoing ones with extreme efficiency. This offloads the CPU, allowing it to focus on higher-level strategy.

- Risk Management Gateways ▴ Critical risk checks, such as maximum position limits or order size validation, are often implemented directly in hardware. This ensures that even with accelerated execution, fundamental risk parameters are enforced with near-zero latency, preventing unintended market exposure.

- Monitoring and Telemetry ▴ Comprehensive monitoring infrastructure, including hardware-based taps and high-resolution logging, is crucial for validating the performance of accelerated systems. This allows for continuous analysis of latency metrics and rapid identification of any degradation in performance.

A comprehensive trading system integrating hardware acceleration requires meticulous design across multiple layers, ensuring seamless communication and minimal latency at every juncture.

The architectural design must consider the trade-offs between flexibility and raw speed. While FPGAs offer reconfigurability, ASICs deliver ultimate performance for fixed functions. A hybrid approach, leveraging FPGAs for dynamic strategy logic and ASICs for core, stable functions, often provides an optimal balance. The entire system functions as a highly specialized computational instrument, where every nanosecond saved contributes directly to enhanced operational control and a distinct competitive advantage.

References

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- O’Hara, Maureen. Market Microstructure Theory. Blackwell Publishers, 1995.

- Lehalle, Charles-Albert. “Market Microstructure in Practice.” World Scientific Publishing Co. Pte. Ltd. 2017.

- Goldstein, Michael A. and Kenneth C. Kavajecz. “Speed and the Rise of the High-Frequency Trader ▴ The Effects of Liquidity, Information, and Competition.” Journal of Financial Economics, vol. 86, no. 3, 2007, pp. 605-633.

- Aquilina, Matthew, and Christian-Oliver Ewald. “Algorithmic Trading ▴ A Primer on Strategy, Technologies, and Regulation.” Journal of Derivatives & Securities Analysis, vol. 18, no. 1, 2015, pp. 1-26.

- Foucault, Thierry, Marco Pagano, and Ailsa Röell. Market Liquidity ▴ Theory, Evidence, and Policy. Oxford University Press, 2013.

- Chakravarty, Sugato, and Huseyin Gulen. “The Speed of Execution and Liquidity in Electronic Markets.” Journal of Financial Markets, vol. 12, no. 2, 2009, pp. 161-180.

- Hasbrouck, Joel. Empirical Market Microstructure ▴ The Institutions, Economics, and Econometrics of Securities Trading. Oxford University Press, 2007.

- Clark, Kevin, and Kevin M. Dowd. “High-Frequency Trading ▴ A Practical Guide to the Market and its Risks.” John Wiley & Sons, 2013.

The Pursuit of Temporal Mastery

The discourse on hardware acceleration and quote cancellation latency reveals more than a technical pursuit; it unveils a fundamental truth about competitive advantage in modern financial markets. The mastery of time, once a philosophical concept, now translates into tangible operational gains. Each nanosecond shaved from a cancellation path is a fraction of a second gained in market responsiveness, a moment of reduced exposure, and an opportunity for strategic re-evaluation. This understanding compels a critical introspection into one’s own operational framework.

Is the current infrastructure merely adequate, or does it actively contribute to a decisive edge? The question extends beyond mere technological adoption; it interrogates the very philosophy of execution. The true power lies not solely in the hardware itself, but in the intelligent integration of these capabilities into a coherent, high-fidelity operational system, one designed to command temporal mastery.

Glossary

Quote Cancellation Latency

Hardware Acceleration

Quote Cancellation

Cancellation Latency

Adverse Selection

Market Microstructure

Temporal Compression

Stale Quotes

Capital Efficiency

Market Data

Kernel Bypass