Concept

In the domain of automated trading, the conversation around hardware is a conversation about time itself. The physical medium through which an instruction travels dictates the fundamental risk profile of a trading strategy. The choice between a Central Processing Unit (CPU) and a Field-Programmable Gate Array (FPGA) is a decision about how a firm wishes to control its interaction with the market at the most elemental level. It defines the boundary between probabilistic and deterministic execution, a distinction that has profound consequences for risk management and profitability.

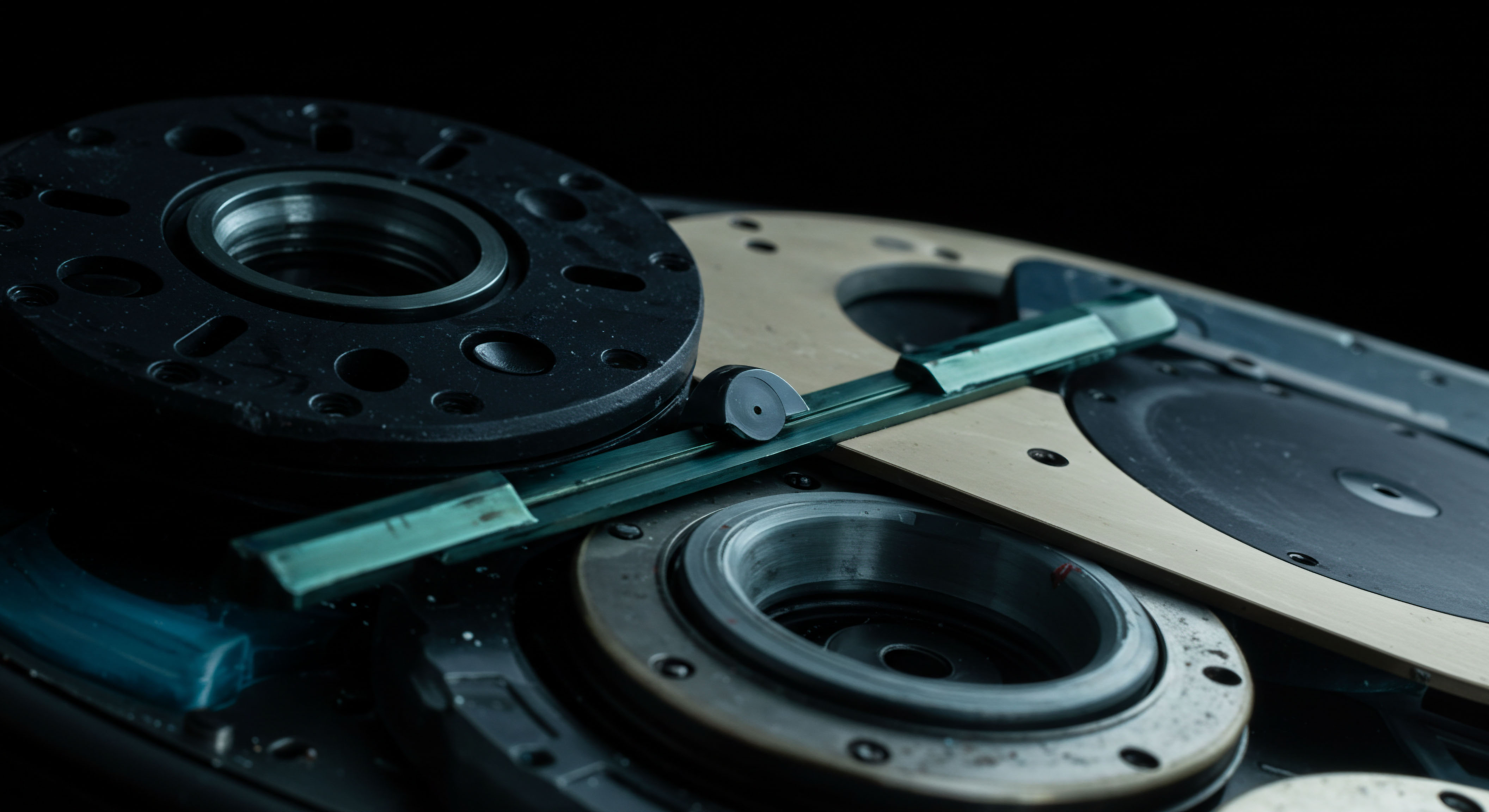

A CPU, the versatile heart of traditional computing, operates on a principle of sequential instruction processing, managed by layers of abstraction like an operating system. This architecture provides immense flexibility but introduces inherent temporal uncertainty, or jitter. An FPGA, in contrast, is a substrate of configurable logic blocks. It is not programmed in the conventional sense; it is configured to become a bespoke digital circuit.

This structural difference moves the operational paradigm from executing software on a general-purpose processor to running tasks on purpose-built, parallel hardware. The risk profiles of these two approaches diverge at this foundational level, long before any trading logic is considered.

The Core Architectural Divergence

Understanding the hardware-level risk differential begins with the core architecture of each device. A CPU is designed for versatility. It fetches, decodes, and executes a stream of instructions, relying on complex features like caches, branch predictors, and multi-threading to accelerate a wide variety of workloads. This complexity, managed by an operating system that juggles countless background processes and interrupts, is the source of its primary hardware-level risk in trading ▴ non-determinism.

The time it takes to execute a specific task can vary based on the processor’s state, cache contents, or an unpredictable operating system interrupt. For a trading system, this jitter is a critical vulnerability. An unexpected delay of even a few microseconds, caused by a cache miss or a context switch, can mean the difference between capturing an arbitrage opportunity and suffering a loss.

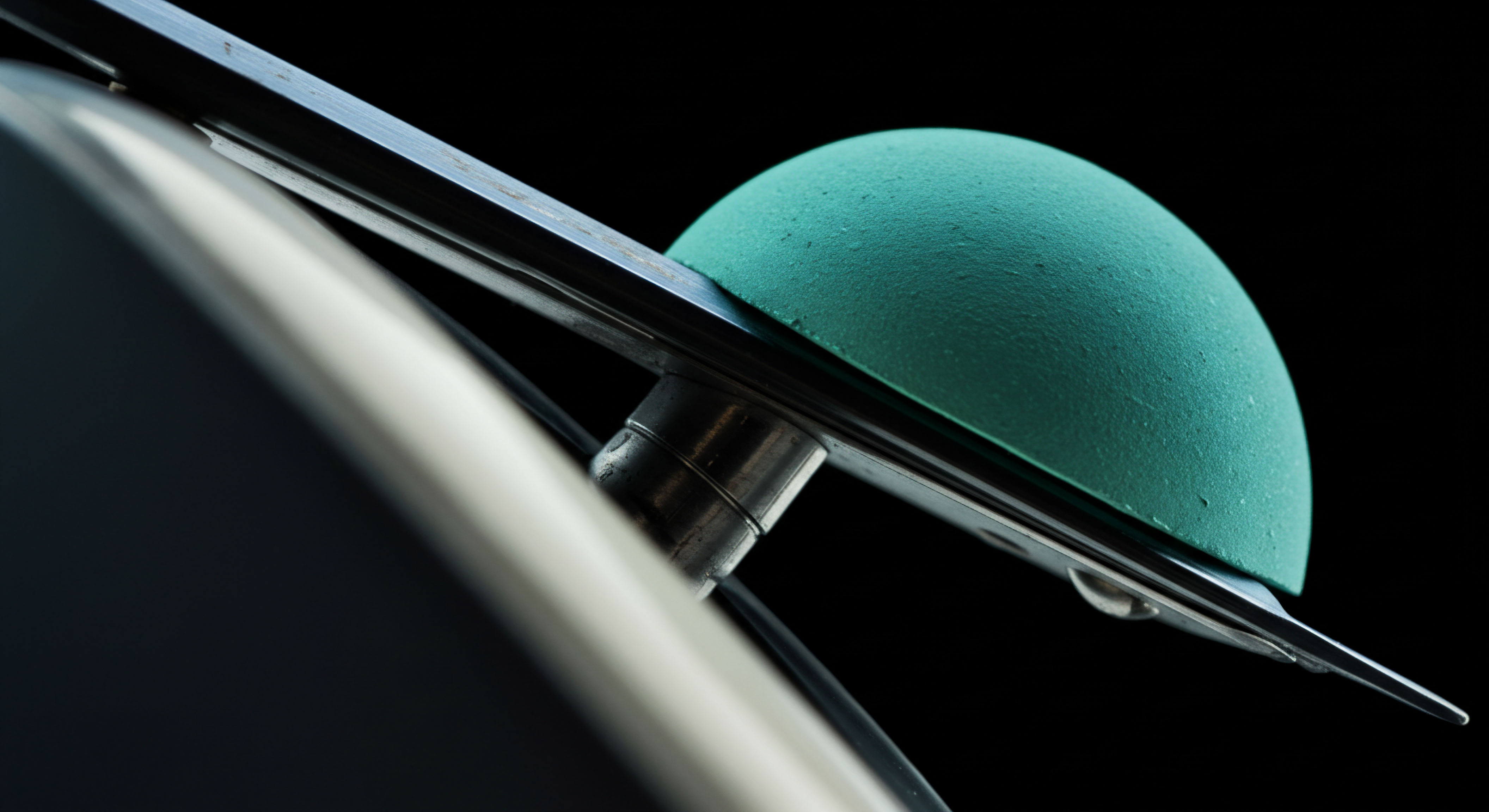

The fundamental distinction lies in how each technology approaches task execution ▴ CPUs process instructions sequentially in a shared, versatile environment, while FPGAs execute tasks in parallel on dedicated, configured circuits.

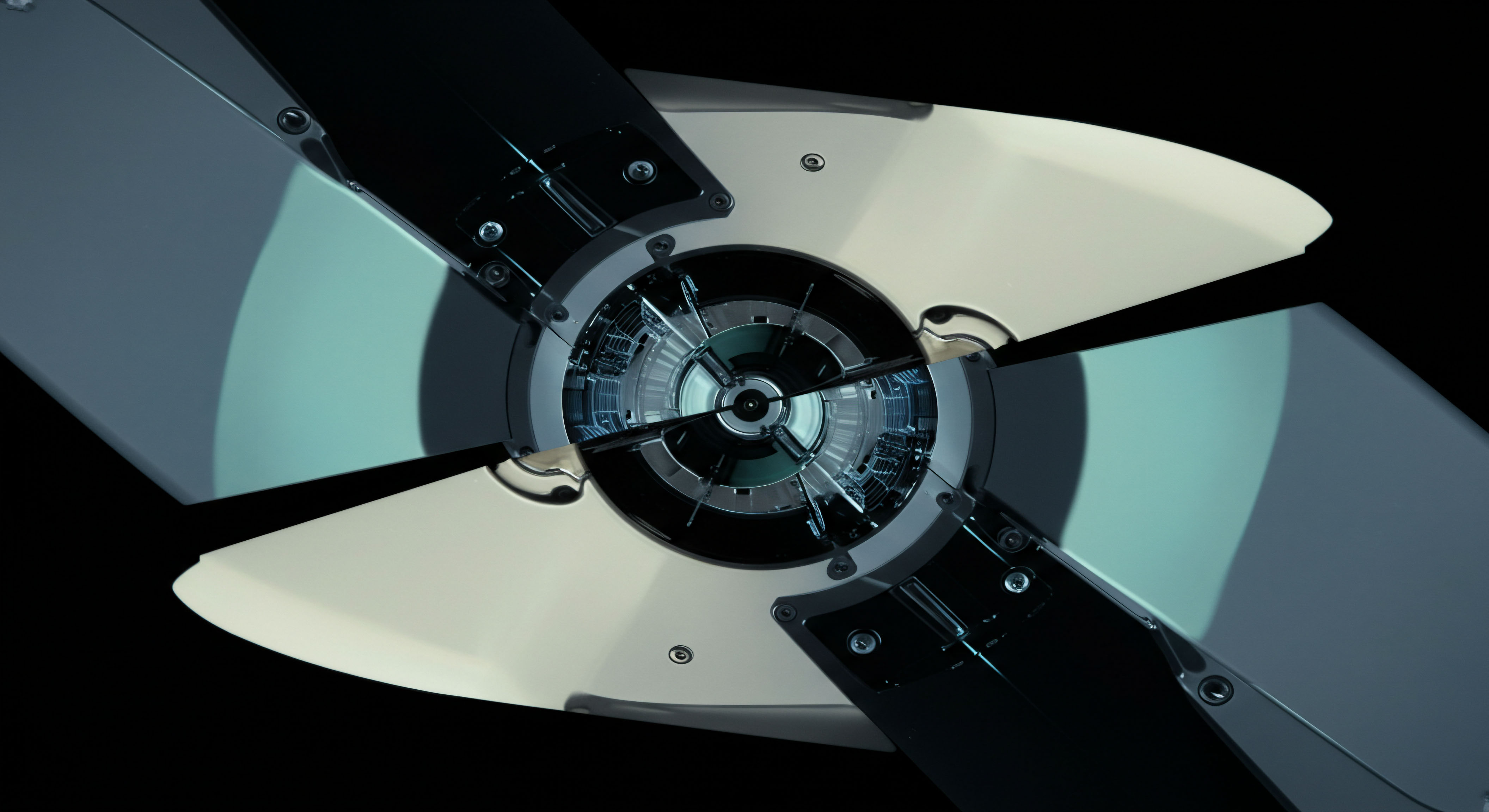

An FPGA’s architecture presents a different set of trade-offs and, consequently, a different risk profile. It is a matrix of logic gates that can be wired together electronically to create a custom circuit designed for a specific task. This process bypasses the overhead of an operating system and the sequential nature of a von Neumann architecture. Trading logic implemented on an FPGA runs in true parallel, with dedicated paths for different functions.

This results in deterministic latency; the time required to process a market data packet and generate an order is constant and predictable, down to the nanosecond. The primary risk shifts from temporal uncertainty to implementation complexity. A flaw in the hardware description language (HDL) code that defines the circuit can lead to catastrophic, systemic failures that are much harder to debug and patch than a software bug. The risk is front-loaded into the design and verification phase, demanding a rigorous engineering discipline distinct from traditional software development.

From Temporal Uncertainty to Design Certainty

The practical implication of this architectural divergence is a shift in the nature of risk itself. With CPU-based systems, risk management is an ongoing, dynamic process of mitigating temporal uncertainty. Engineers focus on isolating trading processes, tuning the operating system kernel, and using techniques like core affinity to minimize jitter.

Despite these efforts, a residual level of unpredictability remains, a “long tail” risk of unexpected latency spikes that can never be fully eliminated. This risk is managed statistically, by analyzing latency distributions and building strategies that can tolerate a certain level of performance variance.

Conversely, with FPGA-based systems, the primary risk is concentrated in the design, verification, and deployment stages. The development cycle is significantly longer and more arduous. Writing Verilog or VHDL to define a circuit requires a specialized skillset, and the verification process is exhaustive, involving complex simulations and formal verification methods to prove the logical correctness of the design. A bug in an FPGA design is not a simple software patch; it requires a complete recompilation and reconfiguration of the hardware, a process that can take hours or even days.

The risk here is one of design flaw and operational rigidity. While the execution is deterministic, the system is inflexible. Adapting to a change in market protocol or a new trading strategy is a major engineering effort, introducing the risk of being outmaneuvered by more agile competitors. The focus of risk management shifts from managing real-time performance variance to ensuring the absolute correctness and integrity of the deployed hardware logic.

Strategy

Strategically evaluating FPGAs and CPUs in a trading context requires moving beyond a simple “speed” comparison. It involves a multi-dimensional analysis of risk, where latency is just one factor. The strategic choice hinges on a firm’s core philosophy ▴ is the primary objective to maximize adaptability and speed of strategy iteration, or is it to achieve the lowest possible, most predictable latency for a specific, well-defined execution path? Each approach carries a unique portfolio of risks that must be aligned with the firm’s trading style, technical capabilities, and operational capacity.

The Spectrum of Latency Risk

The most commonly discussed differentiator is latency, but the strategic risk is more precisely defined by the nature of that latency. CPU-based systems exhibit probabilistic latency, characterized by a distribution with a “long tail.” While the average latency might be low, the system is susceptible to unpredictable outliers caused by operating system interrupts, context switching, cache misses, and other architectural complexities. This unpredictability, or jitter, is a significant strategic risk for latency-sensitive strategies like statistical arbitrage or market making, where consistent performance is paramount.

Choosing between a CPU and an FPGA is a strategic commitment to managing either unpredictable execution timing or complex, rigid design cycles.

FPGAs, on the other hand, offer deterministic latency. Because the trading logic is etched into a physical circuit, the time taken for a signal to travel from input to output is constant and predictable. The risk of jitter is virtually eliminated. This allows for the development of strategies that can operate with extreme confidence at the very edge of the market’s speed envelope.

The strategic trade-off, however, is a complete lack of flexibility. The table below outlines the contrasting latency profiles and their strategic implications.

Table 1 ▴ Comparative Latency Risk Profiles

| Risk Metric | CPU-Based System | FPGA-Based System |

|---|---|---|

| Latency Profile | Probabilistic (Microseconds) | Deterministic (Nanoseconds) |

| Primary Latency Risk | Jitter / Unpredictable Outliers | Fixed latency may be suboptimal if not perfectly designed |

| Source of Risk | OS, kernel interrupts, cache misses, process scheduling | Physical path length of the circuit, logic gate delays |

| Mitigation Strategy | Kernel tuning, core affinity, real-time OS patches | Exhaustive static timing analysis during design phase |

| Strategic Implication | Strategies must be robust to occasional latency spikes | Enables strategies that rely on absolute, predictable speed |

Development Lifecycle and Operational Risk

The development process for each technology represents a major source of strategic and operational risk. CPU development, using high-level languages like C++, is a well-understood discipline. It allows for rapid iteration, extensive library support, and a large talent pool. A new strategy can be coded, tested, and deployed relatively quickly.

The risk is hidden in the layers of abstraction. Compilers, libraries, and the operating system can introduce subtle bugs or performance issues that are difficult to trace back to the source. The speed of deployment comes at the cost of system transparency.

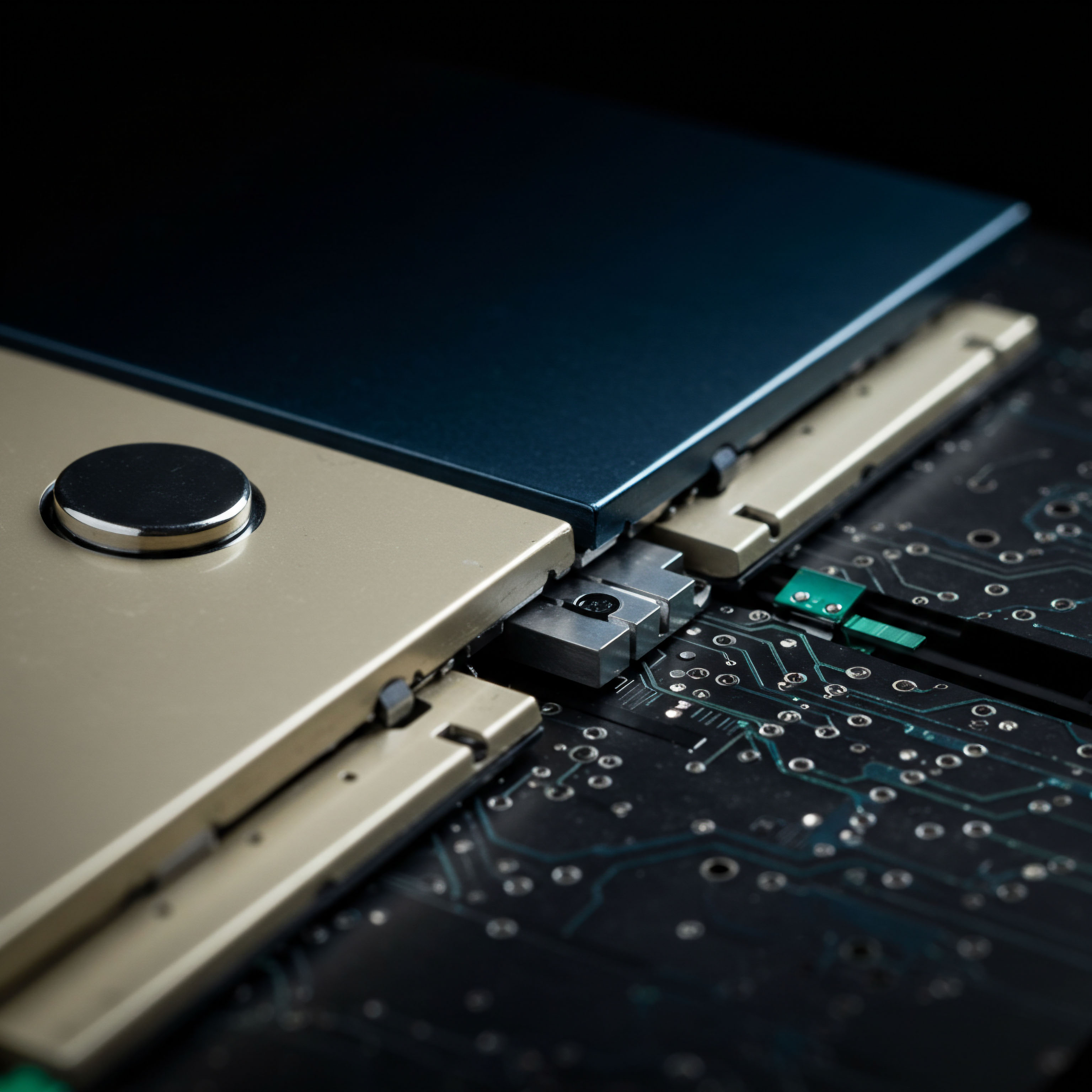

FPGA development is a fundamentally different practice, more akin to hardware engineering than software programming. It involves using Hardware Description Languages (HDLs) to design a circuit, a process that is orders of magnitude more complex and time-consuming. The verification phase is critical and extensive, as a bug in the deployed logic can have catastrophic consequences and cannot be easily patched. This introduces a significant operational risk ▴ the inability to adapt quickly to changing market conditions.

If an exchange modifies its messaging protocol, a CPU-based system might be updated in hours, while an FPGA-based system could be offline for weeks awaiting a complete redesign and verification of its hardware logic. This rigidity is a primary strategic risk that must be weighed against the benefit of deterministic performance.

- CPU Development Risk ▴ Characterized by rapid iteration but opaque layers of abstraction. The primary risk is the introduction of subtle, hard-to-diagnose bugs or performance bottlenecks through software dependencies and OS interactions.

- FPGA Development Risk ▴ Defined by a long, complex, and rigid design cycle. The main risk is the prolonged time-to-market for new strategies or adaptations, creating a vulnerability to more agile competitors. Design flaws are also more critical, requiring a complete hardware reconfiguration.

Environmental and Physical Hardware Risks

Beyond logic and latency, the physical operating environment presents another layer of risk. Both CPUs and FPGAs are susceptible to environmental factors, but their failure modes and mitigation strategies differ.

CPUs, particularly high-core-count server processors, generate significant heat and are subject to thermal throttling. A spike in activity can cause the CPU to automatically reduce its clock speed to prevent overheating, introducing a sudden and unpredictable increase in latency. This risk is managed through sophisticated cooling systems and server room environmental controls, but it remains a potential point of failure.

FPGAs, while generally more power-efficient for a given task, also have strict thermal operating envelopes. A more subtle and insidious risk in FPGAs is the danger of bitstream corruption. The configuration file, or “bitstream,” that defines the circuit is loaded onto the FPGA.

A radiation-induced single-event upset (SEU) or a power fluctuation could theoretically corrupt this bitstream, altering the circuit’s logic in a silent and potentially disastrous way. While rare, this risk requires mitigation through techniques like cyclical redundancy checks (CRCs) on the bitstream and the implementation of fault-tolerant logic within the FPGA design itself, adding another layer of complexity to the development process.

Execution

In the execution phase, the theoretical differences between CPU and FPGA risks become tangible operational realities. The focus shifts from strategic choice to the granular mechanics of risk mitigation and performance validation. For trading firms, execution is where the architectural decisions translate directly into profit or loss. Mastering the execution environment for either a CPU or an FPGA requires a distinct set of tools, procedures, and expertise aimed at controlling the specific hardware-level risks inherent to each platform.

A Playbook for Hardware Risk Mitigation

Effective risk management at the hardware level is not a passive process. It involves a proactive and highly specialized set of procedures designed to harden the trading system against its innate vulnerabilities. The execution playbook for a CPU-based system is centered on taming the general-purpose environment, while the FPGA playbook focuses on ensuring the integrity of a custom-built one.

For a CPU system, the goal is to create a “quiet” environment where the trading application can run with minimal interference. This involves a deep interaction with the operating system and the physical hardware configuration.

- CPU Core Affinity and Shielding ▴ This is a foundational technique where specific CPU cores are exclusively reserved for the trading application. The operating system and all other non-essential processes are “shielded” from these cores, preventing them from causing context switches or cache pollution that would introduce jitter.

- Kernel Tuning ▴ A standard Linux kernel is not optimized for low-latency operations. Execution requires a custom-tuned kernel where timers, schedulers, and interrupt handling routines are modified to prioritize predictable performance over general-purpose throughput. This can involve using real-time patches like PREEMPT_RT.

- Interrupt Management ▴ Network card interrupts are a primary source of latency. The playbook involves assigning these interrupts to specific, non-trading cores to ensure that the data processing cores are not disturbed.

For an FPGA system, the execution playbook is dominated by pre-deployment validation. The goal is to prove, with mathematical certainty, that the hardware design is free of logical errors.

- Formal Verification ▴ Beyond simple simulation, formal verification uses mathematical methods to prove or disprove the correctness of a hardware design’s properties. This technique can identify corner-case bugs that might be missed by trillions of simulation cycles.

- Comprehensive Timing Closure ▴ This is a critical step in the FPGA compilation process. The tools analyze every possible signal path within the design to ensure that it can meet the target clock frequency. Failure to achieve “timing closure” means the circuit will not function reliably at speed.

- In-Circuit Logic Analyzers ▴ Modern FPGAs allow for the inclusion of debugging logic, like a miniature logic analyzer, directly within the design. This allows engineers to monitor internal signals in real-time on the deployed hardware, providing a crucial tool for diagnosing issues that only appear during live operation.

Quantitative Analysis of Latency Jitter

The financial impact of hardware-level risk can be quantified by analyzing latency distributions. A CPU’s probabilistic nature results in a wider, less predictable distribution, while an FPGA’s deterministic nature yields a tight, narrow one. The table below presents a hypothetical analysis of one million transaction timestamps for a simple market data-in to order-out process, illustrating the quantitative difference in risk.

The ultimate measure of hardware risk is found in the statistical distribution of latency, where the “tail” of the distribution represents the potential for catastrophic financial loss.

Table 2 ▴ Latency Distribution Analysis (Hypothetical Data)

| Latency Metric | CPU-Based System (nanoseconds) | FPGA-Based System (nanoseconds) |

|---|---|---|

| Mean Latency | 2,500 ns | 350 ns |

| Median Latency | 2,450 ns | 350 ns |

| Standard Deviation | 800 ns | 5 ns |

| 99th Percentile (P99) | 4,500 ns | 355 ns |

| 99.99th Percentile (P9999) | 15,000 ns | 360 ns |

| Maximum Observed Latency | 85,000 ns | 365 ns |

The data reveals the core of the risk differential. While the CPU system’s average performance is in the low microseconds, its P9999 latency is an order of magnitude higher. This “tail risk” represents the 1 in 10,000 trades that experience a significant delay. For a high-frequency market-making strategy, such a delay could lead to being adversely selected, resulting in a substantial loss.

The FPGA system, by contrast, shows almost no deviation. Its maximum observed latency is only marginally higher than its mean. This predictability allows the firm to quantify its execution risk with a much higher degree of confidence, enabling more aggressive and finely tuned trading strategies. The financial risk of the CPU system lies in the cost of these unpredictable tail events, while the FPGA system’s primary financial risk lies in the massive upfront development cost and the potential for design flaws.

References

- Klaisoongnoen, W, et al. “I feel the need for speed ▴ Exploiting latest generation FPGAs in providing new capabilities for high frequency trading.” 2021 IEEE 33rd International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD), 2021.

- Underwood, Keith, and K. Scott Hemmert. “Closing the gap ▴ The performance of GPGPU versus FPGA for HPC.” 2012 IEEE 20th Annual International Symposium on Field-Programmable Custom Computing Machines, 2012.

- Lockwood, John W. et al. “FPGA-based packet filtering and dropping for denial of service attack prevention.” ACM SIGARCH Computer Architecture News, vol. 35, no. 5, 2007, pp. 98-103.

- “The Role of FPGAs in High-Frequency Trading.” Magmio, 2023.

- “FPGA vs. CPU ▴ A Look at the Future of High-Frequency Trading.” The TRADE, 2022.

- Guo, K. et al. “A survey of FPGA-based neural network accelerators.” ACM Transactions on Reconfigurable Technology and Systems (TRETS), vol. 12, no. 1, 2019, pp. 1-24.

- Herbordt, Martin C. et al. “A survey of FPGA-based systems for bioinformatics.” ACM Computing Surveys (CSUR), vol. 45, no. 4, 2013, pp. 1-38.

- Long, Burton, and David Seddon. “FPGA High-Frequency Trading ▴ From Nanoseconds to Profit.” Finance and Technology, 2021.

Reflection

The True Nature of the Machine

The decision between these two silicon substrates is ultimately a reflection of a firm’s identity. It forces a critical self-examination of core competencies, risk appetite, and strategic posture. Is the organization’s strength in the rapid, creative iteration of complex software models, thriving on market adaptability? Or is its edge found in the meticulous, patient engineering of a perfect, unchanging execution machine?

There is no universally superior answer. The choice of hardware defines the operational philosophy. It sets the terms of engagement with the market, establishing whether the firm will navigate the chaotic currents of the market with a nimble vessel or attempt to slice through them with an immutable blade. The true risk is not in choosing one technology over the other, but in failing to comprehend how that choice permeates every aspect of the trading operation, from the skillset of the engineering team to the fundamental assumptions underpinning every strategy.

Glossary

Risk Management

Temporal Uncertainty

Operating System

Hardware-Level Risk

Hardware Description Language

Formal Verification

Operational Rigidity

Cpu-Based System