Concept

The pursuit of alpha in electronically traded markets is fundamentally a contest of speed. At the heart of this contest lies a critical architectural decision ▴ how an application receives and processes market data. The choice between kernel bypass techniques and hardware-based acceleration using Field-Programmable Gate Arrays (FPGAs) represents two distinct philosophies for minimizing latency.

This decision is not merely a technical detail; it is a foundational choice that defines a firm’s entire operational posture, risk profile, and capacity for innovation. Understanding the core mechanics of each approach is the first step in architecting a system capable of competing at the nanosecond level.

The Kernel Conundrum

In a standard computing environment, every network packet that arrives at a Network Interface Card (NIC) must traverse the operating system’s kernel. The kernel is the core of the OS, managing system resources, scheduling processes, and providing a layer of abstraction between hardware and software. For network data, this involves a series of steps ▴ the NIC driver raises an interrupt, the kernel copies the packet from the NIC’s buffer into kernel-space memory, processes it through the TCP/IP stack (which involves checksums, sequencing, and state management), and finally copies it again to the user-space memory of the waiting application. Each step ▴ each context switch and memory copy ▴ introduces delay and unpredictability, measured in microseconds.

For most applications, this overhead is negligible. For a high-frequency trading application, these microseconds represent an eternity of missed opportunities.

Kernel bypass is a strategy that allows an application to communicate directly with the network hardware, circumventing the operating system’s slow and non-deterministic data path.

Software Redefined Path Kernel Bypass

Kernel bypass techniques create a direct data path between the NIC and the user-space application. This is achieved by using specialized libraries and drivers that map the NIC’s hardware buffers directly into the application’s memory space. When a packet arrives, the application can read it directly from the NIC’s receive queue without involving the kernel. This eliminates multiple memory copies (a concept known as “zero-copy”) and avoids the overhead of kernel-level processing and context switches.

There are several prominent implementations of this philosophy:

- Data Plane Development Kit (DPDK) ▴ An open-source set of libraries and drivers, primarily managed by the Linux Foundation, that provides a framework for fast packet processing. DPDK allows an application to take direct control of a NIC, dedicating it entirely to that application and using polling instead of interrupts to check for new packets, which further reduces latency.

- Vendor-Specific Libraries ▴ Companies like Solarflare (now part of AMD/Xilinx) and Mellanox (now part of NVIDIA) offer their own kernel bypass solutions. Solarflare’s OpenOnload, for instance, can transparently accelerate existing network applications by intercepting standard socket calls and redirecting them through its own highly optimized, low-latency user-space network stack.

The essence of kernel bypass is achieving hardware-like performance by running a highly optimized, specialized software stack on a general-purpose CPU. It is a software-centric solution to a hardware-level problem.

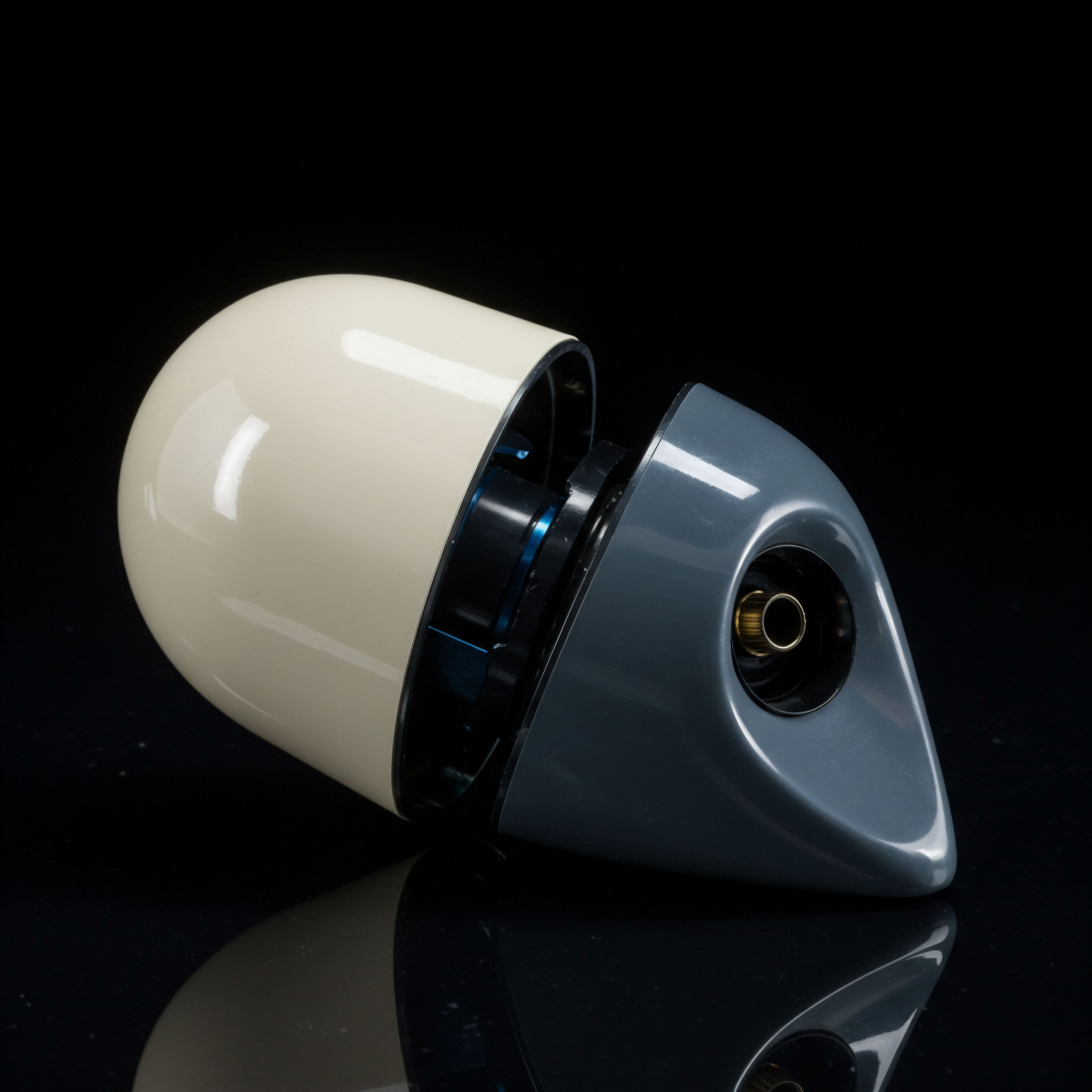

Hardware Embodied Logic FPGAs

Hardware-based acceleration with FPGAs takes a fundamentally different approach. An FPGA is a type of integrated circuit that can be reconfigured by a developer after manufacturing. It consists of a vast array of programmable logic blocks and a hierarchy of reconfigurable interconnects that allow the blocks to be wired together.

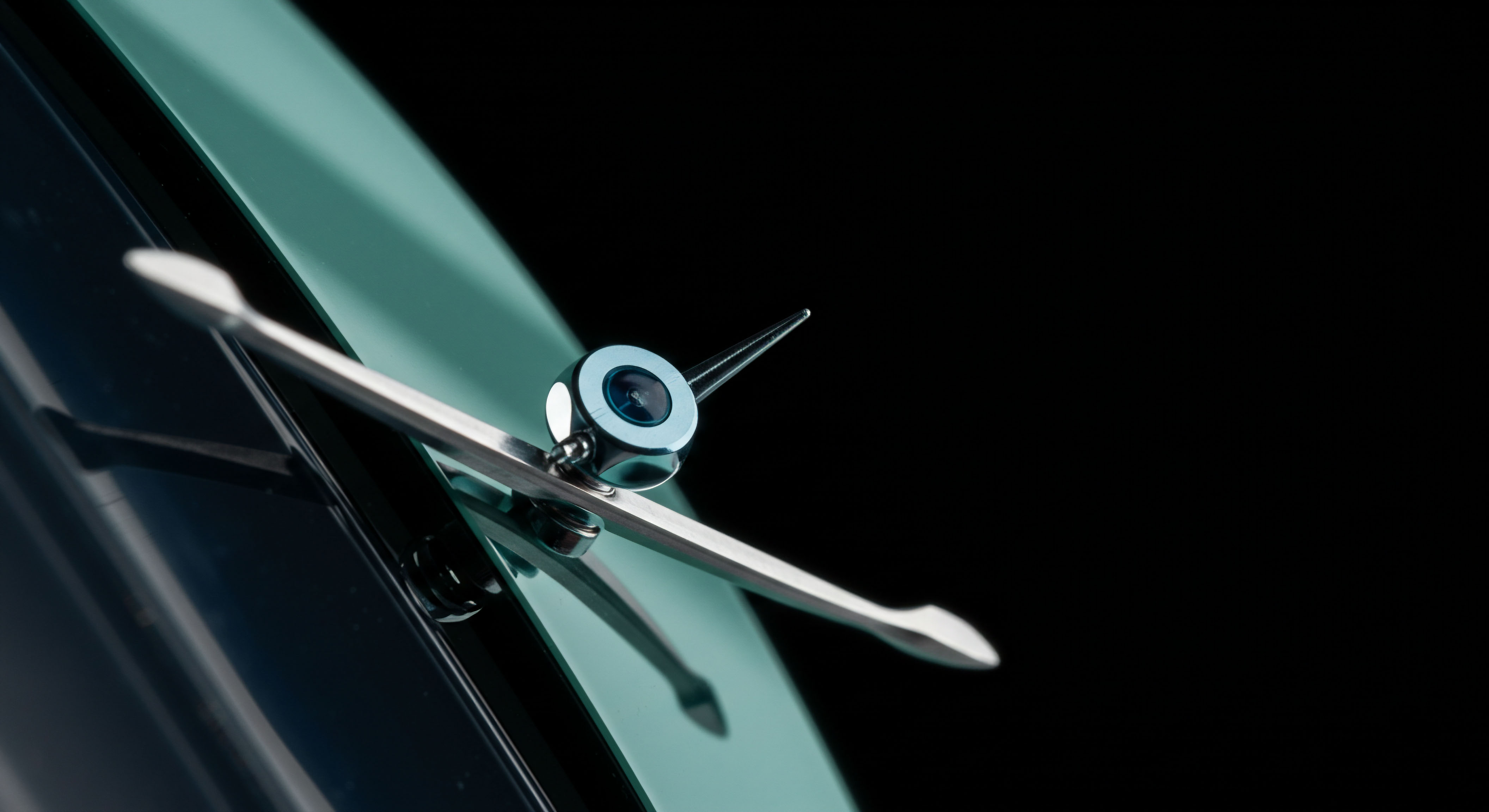

This is akin to being given a set of fundamental digital building blocks (like logic gates) and the ability to connect them in any way to create a custom digital circuit. In the context of trading, an FPGA can be programmed to perform the entire network stack processing ▴ from parsing Ethernet frames and handling TCP/IP sessions to decoding market data feeds (like ITCH or FAST) and even executing the trading logic itself ▴ directly in silicon.

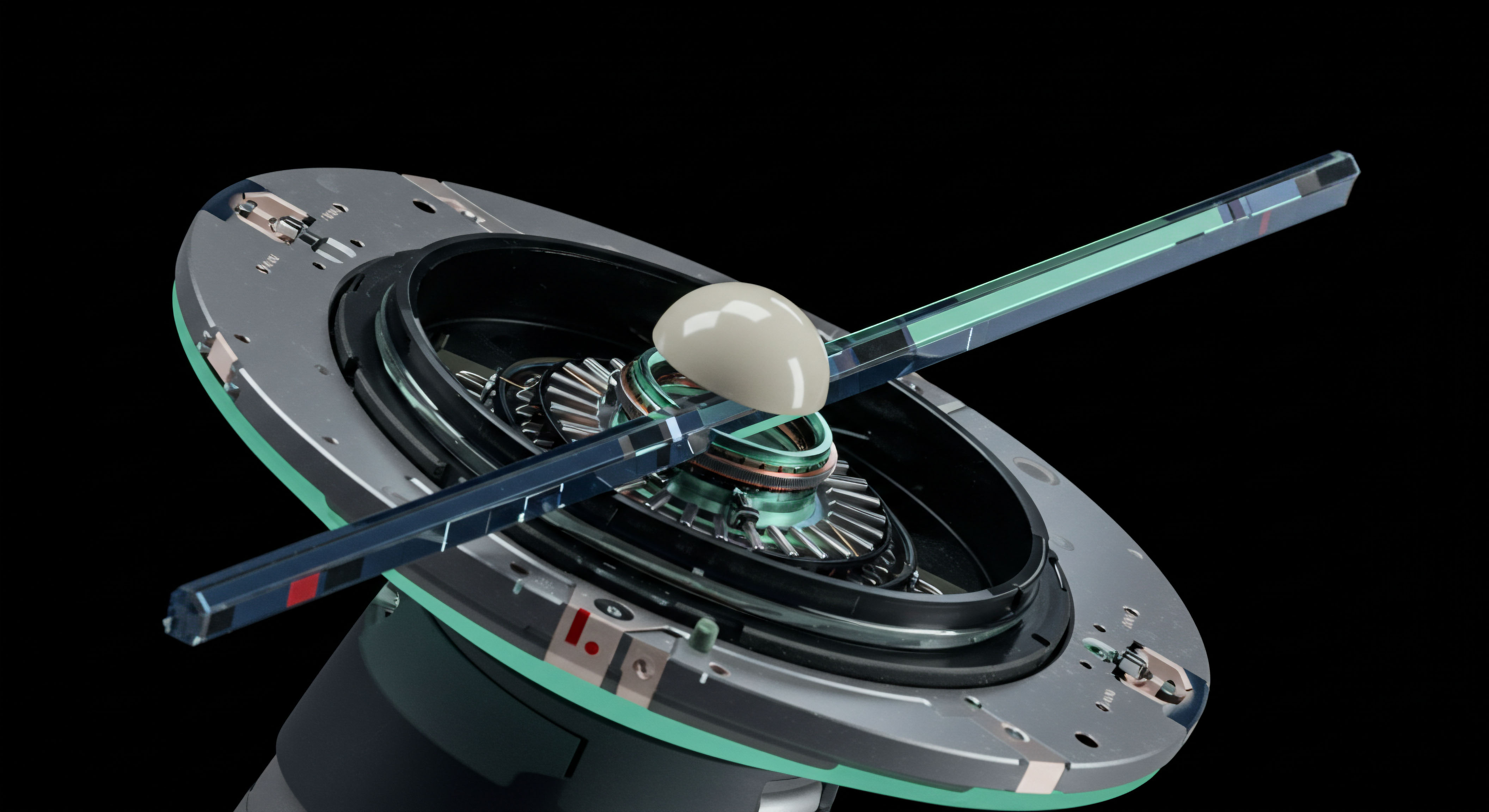

FPGAs move the processing logic from software running on a CPU to a dedicated, reconfigurable hardware circuit, enabling true parallel processing at line rate.

When a packet arrives at an FPGA-based accelerator card, it doesn’t wait to be processed by a CPU. Instead, it flows directly into the custom-designed logic circuit. Operations that would be executed sequentially in software can be implemented as a deep pipeline in hardware, where each stage of the pipeline processes a different packet simultaneously.

This results in deterministic, nanosecond-level latency. The processing happens as the data streams through the chip, a concept known as “cut-through” processing, which is the pinnacle of low-latency design.

Strategy

The strategic decision between deploying a kernel bypass solution or a hardware-based FPGA architecture is a multi-dimensional problem. It extends beyond a simple latency comparison to encompass development velocity, operational flexibility, total cost of ownership, and the intrinsic nature of the trading strategies being deployed. Each path offers a distinct set of advantages and imposes its own unique constraints. A firm’s choice reflects its core competencies, its risk appetite, and its long-term vision for its technological infrastructure.

A Framework for Architectural Selection

The selection process is an exercise in trade-offs. While FPGAs typically offer the lowest possible latency and jitter, this performance comes at the cost of increased complexity and development time. Kernel bypass solutions provide a significant leap in performance over standard kernel networking while retaining the familiar software development environment. The optimal choice depends on where a firm positions itself on the spectrum between raw performance and operational agility.

Comparative Performance Metrics

The most immediate point of comparison is, of course, latency. However, a nuanced view must also consider throughput and jitter, as these factors are equally critical for a robust trading system.

| Metric | Standard Kernel Networking | Kernel Bypass (e.g. DPDK, OpenOnload) | FPGA-Based Acceleration |

|---|---|---|---|

| Median Latency (Application-to-Application) | 50 – 200+ microseconds | 1 – 5 microseconds | 50 – 500 nanoseconds |

| Jitter (99th Percentile Latency) | High (subject to OS scheduling, interrupts) | Low (dedicated cores, polling) | Extremely Low (deterministic hardware path) |

| Microburst Handling | Poor (prone to packet loss) | Excellent (can process at line rate) | Superior (processes at line rate with fixed latency) |

As the table illustrates, FPGAs operate in a different performance universe, measuring latency in nanoseconds rather than microseconds. This advantage is most pronounced in reducing jitter ▴ the variation in latency. For strategies that rely on predictable response times, the deterministic nature of an FPGA’s hardware path is a decisive advantage.

Development Lifecycle and Total Cost of Ownership

Performance is only one part of the equation. The human and financial costs associated with developing, deploying, and maintaining these systems are critical strategic considerations.

- Talent and Skillset ▴ Kernel bypass development primarily uses C and C++, languages with a vast talent pool. Developers can leverage standard software engineering tools and practices. FPGA development, conversely, requires expertise in Hardware Description Languages (HDLs) like Verilog or VHDL, and a deep understanding of digital circuit design. This is a far more specialized and scarce skillset. While High-Level Synthesis (HLS) tools that compile C/C++ to HDL are maturing, they still require a hardware-aware mindset to achieve optimal results.

- Development and Debugging Cycle ▴ A software-based kernel bypass application can be compiled in minutes, and debugging can be done with familiar tools like GDB. Compiling an FPGA design (a process called synthesis and place-and-route) can take hours or even days for complex designs. Debugging is also more challenging, often relying on simulation and in-circuit logic analyzers. This longer iteration cycle significantly impacts development velocity.

- Flexibility and Adaptability ▴ A key strategic advantage of kernel bypass is flexibility. Modifying a trading algorithm is a software change that can be deployed relatively quickly. While FPGAs are “re-programmable,” making changes to the hardware logic is a more involved process. If a firm’s strategy requires frequent algorithmic adjustments, the agility of a software-based approach may be more valuable than the raw speed of an FPGA.

Mapping Technology to Trading Strategy

The suitability of each technology is intrinsically linked to the requirements of the trading strategy it will execute. There is no single “best” solution; there is only the most appropriate tool for a given task.

| Trading Strategy | Primary Requirement | Optimal Technology Choice | Rationale |

|---|---|---|---|

| Cross-Exchange Latency Arbitrage | Lowest possible latency | FPGA | The strategy’s profitability is almost entirely dependent on being the absolute fastest to react to price discrepancies. Nanosecond advantages are critical. |

| Market Making | Low latency with high message throughput and reliability | FPGA or Kernel Bypass | FPGAs are ideal for simple, quote-and-cancel heavy strategies. More complex market making models that require sophisticated calculations might benefit from the flexibility of a CPU-based kernel bypass system. |

| Smart Order Routing (SOR) | Complex decision logic, flexibility | Kernel Bypass | SOR algorithms often involve evaluating liquidity across multiple venues and considering many factors beyond simple price. The computational power and programmability of a CPU are well-suited to this complexity. |

| Pre-Trade Risk Checks | Deterministic, low-latency filtering | FPGA | Implementing compliance and risk checks directly in hardware ensures they are applied at line rate with no impact on the trading application’s performance, providing a “bump-in-the-wire” safeguard. |

Execution

Transitioning from strategic evaluation to operational execution requires a granular understanding of the implementation pathway for both kernel bypass and FPGA-based systems. This involves not only the technical architecture but also a disciplined process of profiling, modeling, and integration. The goal is to construct a high-performance trading apparatus where every component is optimized and works in concert to achieve the desired latency and throughput objectives.

The Operational Playbook

A successful implementation, regardless of the chosen technology, follows a structured, data-driven process. A firm cannot simply acquire a technology; it must integrate it into a coherent operational framework.

- Baseline Performance Profiling ▴ The initial step is to meticulously measure the existing system’s performance. This involves capturing packet timestamps at various points in the stack to identify the precise sources of latency, from network transit to kernel processing and application logic. This data provides the empirical foundation for setting realistic improvement targets.

- Define the Latency Budget ▴ Based on the strategy’s requirements, a “latency budget” must be established. This budget allocates a maximum permissible delay for each segment of the trade lifecycle ▴ market data in, processing and decision-making, and order out. This analytical rigor focuses optimization efforts where they will have the most impact.

- Technology Prototyping and Bake-Off ▴ Before full-scale commitment, a “bake-off” between competing solutions is essential. For kernel bypass, this could mean comparing the performance and API usability of DPDK versus a vendor solution like OpenOnload on identical hardware. For FPGAs, it could involve evaluating different accelerator cards and their associated development toolchains.

- System Hardening and Tuning ▴ Once a technology is selected, the host server must be aggressively tuned. This includes BIOS adjustments (disabling power-saving states), OS tuning (isolating CPUs for dedicated tasks, known as CPU pinning), and optimizing memory access patterns to ensure the application runs with maximum efficiency and determinism.

- Continuous Monitoring and Optimization ▴ A low-latency system is not a “set and forget” asset. It requires continuous monitoring using high-precision timestamping and performance counters to detect regressions and identify new optimization opportunities as market conditions and application logic evolve.

Quantitative Modeling and Data Analysis

To make an informed decision, it is crucial to model the expected performance and cost implications of each path. The following table presents a hypothetical quantitative comparison for a latency-sensitive trading application, providing a framework for such an analysis. The data represents realistic estimates for a round-trip “tick-to-trade” operation.

| Parameter | Kernel Bypass (DPDK-based) | FPGA (Full Hardware Offload) |

|---|---|---|

| Mean Round-Trip Latency (ns) | 2,500 | 350 |

| 99.9th Percentile Latency (ns) | 8,000 | 450 |

| Host CPU Utilization (per core) | 85-95% (on dedicated core) | <5% (for control/monitoring) |

| Maximum Message Rate (million msg/sec) | ~10 | >20 (line rate limited) |

| Estimated Development Time (man-months) | 6 – 9 | 18 – 24 |

| Required Skillset | C/C++, Network Programming | Verilog/VHDL, Digital Design, HLS |

| Estimated 3-Year TCO (Hardware + Talent) | $1.5 Million | $3.5 Million |

This model highlights the core trade-off ▴ the FPGA solution offers an order-of-magnitude improvement in latency and jitter, but at more than double the total cost of ownership due to longer development cycles and the higher cost of specialized engineering talent. The kernel bypass approach provides a massive improvement over a standard kernel stack at a lower cost and with greater agility, making it a potent and often more practical choice for a wider range of strategies.

The choice is an economic one ▴ is the nanosecond-level advantage offered by an FPGA worth the substantial increase in cost and reduction in strategic flexibility?

System Integration and Technological Architecture

The practical integration of these technologies into a trading system reveals their architectural differences.

Kernel Bypass Integration

A system using kernel bypass dedicates one or more CPU cores entirely to the trading application. The architecture is software-centric:

- Data Path ▴ The NIC is unbound from the kernel driver and bound to a user-space driver like DPDK. The application runs in a tight loop, continuously polling the NIC’s receive queues for new packets.

- Processing ▴ Once a packet is received into the application’s memory space, the CPU executes the full logic ▴ parsing the network headers, decoding the market data payload, evaluating the trading algorithm, constructing an outbound order, and writing it to the NIC’s transmit queue.

- Integration ▴ The application is a standard Linux executable, albeit one that requires careful tuning. It interfaces with other systems (like a central risk management or position-keeping database) over standard inter-process communication (IPC) mechanisms or a dedicated low-latency message bus. The key is to keep these interactions off the critical path.

FPGA Integration

An FPGA-based system redefines the boundary between hardware and software. The architecture is hardware-centric:

- Data Path ▴ The network cable connects directly to the FPGA card. The FPGA itself contains the Ethernet MAC, effectively making it the network endpoint.

- Processing ▴ The entire critical path logic is implemented in hardware. This includes the TCP/IP stack, the market data parser, and often a simplified version of the trading algorithm. The host CPU is relegated to a supervisory role.

- Integration ▴ The host application communicates with the FPGA over the PCIe bus. This communication is for non-latency-critical tasks ▴ configuring the trading logic on the FPGA, receiving status updates, and handling exceptions. The actual high-speed trading decisions and order placements occur entirely within the FPGA, without any involvement from the host CPU. This creates a “bump-in-the-wire” device where data goes in and orders come out, all handled by the reconfigurable circuit.

References

- Lockwood, J. W. (2021). Algorithms in Logic for Ultra Low Latency Networking ▴ Full Stack Applications in FPGAs. IEEE Hot Interconnects.

- Leber, C. Geib, B. & Litz, H. (2011). A HFT-optimized FAST-decoder in an FPGA-based streaming architecture. 21st International Conference on Field Programmable Logic and Applications.

- Databento. (n.d.). What is kernel bypass and how is it used in trading?. Databento Microstructure Guide.

- Ahmad, M. & Rizvi, A. (2020). DPDK for ultra low latency applications. DPDK Userspace Summit 2020.

- Velvetech. (2024). In Pursuit of Ultra-Low Latency ▴ FPGA in High-Frequency Trading. Velvetech.

- Herrmann, F. & Perin, G. (2009). An UDP/IP Network Stack in FPGA. 16th IEEE International Conference on Electronics, Circuits, and Systems.

- Harris, L. (2003). Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press.

- Gope, P. & Sikdar, B. (2018). Lightweight and Privacy-Preserving RFID Authentication Scheme for E-health applications. 2018 IEEE International Conference on Communications (ICC).

- McGuirk, M. & Courtney, D. (2023). FPGAs and the future of high-frequency trading technology. The TRADE.

- Yasukata, K. et al. (2016). StackMap ▴ Low-Latency Networking with the OS Stack and Dedicated NICs. Usenix ATC 2016.

Reflection

The Systemic Definition of Speed

The deliberation between kernel bypass and FPGA acceleration forces a firm to define what “speed” truly means within its operational context. Is it the raw, unyielding velocity of electrons through silicon, measured in the smallest possible number of nanoseconds? Or is it the agility to adapt, to redeploy capital and logic faster than the competition can rewrite their hardware? The answer defines the organization’s technological soul.

Viewing this choice through a systemic lens reveals that neither technology is an isolated solution. Each is a component within a larger architecture of capital, intellect, and risk. The optimal system is not one that is simply “fast,” but one that achieves a state of resonance, where the latency profile of its technology is perfectly matched to the half-life of its strategic opportunities. The ultimate edge is found not in the hardware or the software, but in the institutional wisdom to know which to deploy, and when.

Glossary

Kernel Bypass

Market Data

High-Frequency Trading

Zero-Copy

Dpdk

Fpga

Latency and Jitter