Concept

In the domain of institutional trading, the pursuit of alpha is inextricably linked to the mastery of time. The physical distance between an exchange’s matching engine and a firm’s trading algorithm is a known constraint, measured in meters of fiber optic cable. The true variable, the frontier of competition, resides within the processing stack of the trading system itself.

It is here, in the nanoseconds that separate a market event from a calculated response, that a decisive advantage is forged. The conversation about minimizing latency, therefore, begins not at the network level, but deep within the server’s operating system, at the point where data packets arrive and are translated into actionable intelligence.

At the heart of this internal journey is the operating system’s kernel. The kernel acts as the central nervous system for all machine operations, managing resources, scheduling processes, and, crucially, handling all network input/output (I/O). For most applications, this centralized management is a feature, providing stability and security. For a high-frequency trading algorithm, it is a bottleneck.

Every incoming market data packet must traverse the kernel’s networking stack ▴ a multi-layered process of checks, buffer copies, and context switches ▴ before it is finally delivered to the user-space application where the trading logic resides. This journey, while reliable, is laden with latency and, perhaps more damagingly, unpredictable delays known as jitter. When success is measured in increments of time smaller than a single thought, this variability is unacceptable.

The Direct Data Pathway

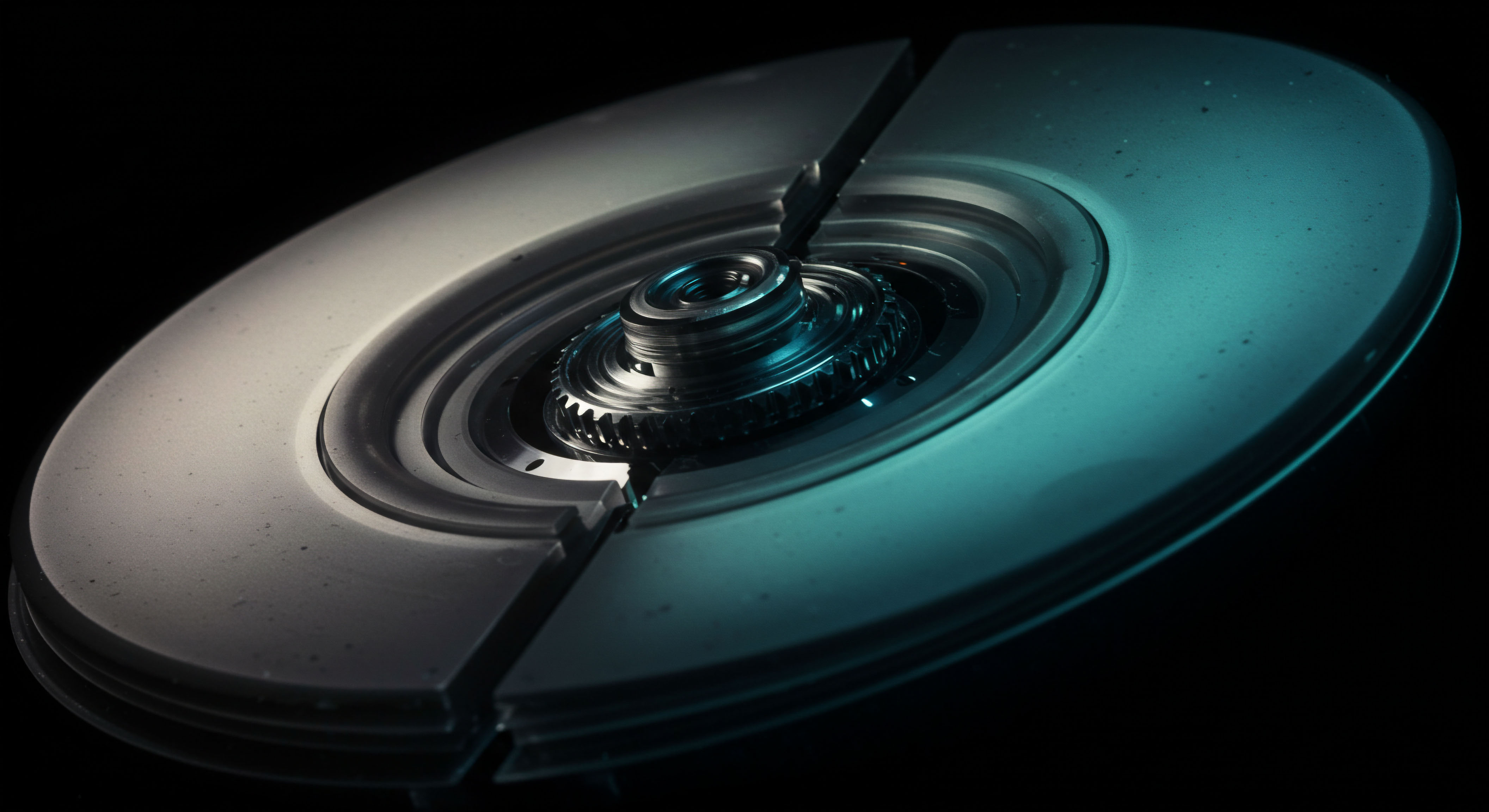

Kernel bypass technology provides a direct conduit from the network interface card (NIC) to the trading application. It constructs a private data path that circumvents the operating system’s kernel entirely. The application is granted direct memory access (DMA) to the NIC’s buffers, allowing it to read incoming data packets the moment they are received by the hardware. This eliminates the multiple data copies and context switches inherent in the traditional kernel path.

A context switch, where the CPU must save the state of the user application and load the state of the kernel to handle a network interrupt, is a profoundly expensive operation in the time-scale of low-latency trading. By avoiding these switches, kernel bypass preserves the temporal integrity of the data’s arrival and allows the trading application to maintain a continuous, uninterrupted focus on its primary task ▴ processing market data.

The Principle of Data Minimization

While kernel bypass clears the highway for data to travel, the volume of that data presents its own challenge. In a volatile market, an exchange can disseminate millions of messages per second for a single instrument. Transmitting the entire state of the order book with every single update is profoundly inefficient. This is the problem that incremental data feeds are designed to solve.

Instead of sending a complete snapshot of the order book, an incremental feed transmits only the changes ▴ the deltas. A new order, a cancellation, or a modification is communicated as a discrete, small message. It is the responsibility of the receiving application to ingest this stream of deltas and use them to maintain an exact, real-time replica of the exchange’s order book. This approach dramatically reduces the volume of data that must be transmitted and processed, freeing up network bandwidth and, more importantly, reducing the computational load on the receiving system.

Kernel bypass and incremental feeds work in concert, one creating a faster pathway and the other reducing the traffic that travels upon it.

The synergy between these two technologies is foundational to modern low-latency trading systems. Kernel bypass provides the raw speed for packet delivery, while incremental feeds ensure that the packets being delivered are dense with new information and free of redundant data. This combination allows a trading system to react to market changes with the lowest possible latency, transforming a flood of raw data into a precise, actionable understanding of the market’s state.

Strategy

Integrating kernel bypass with incremental data feeds is a strategic decision to engineer a system with a high degree of “mechanical sympathy.” This principle, borrowed from high-performance engineering, dictates that a system achieves maximum efficiency when its software architecture is in deep alignment with the properties of the underlying hardware and data protocols. A trading system is a data processing engine, and its performance is a function of how efficiently it can move data from the network wire to its logical core. The strategic framework, therefore, is one of removing friction at every stage of this journey.

A Tale of Two Stacks

To fully appreciate the strategic advantage, consider two distinct system architectures. The first is a traditional networking stack, where the application relies on the operating system’s kernel to receive and process network packets containing full market data snapshots. The second is an optimized stack, employing kernel bypass technologies to receive an incremental data feed directly into the application’s memory space. The performance differential is not merely quantitative; it is a qualitative shift in the system’s character.

The traditional stack is defined by interrupts and copies. When a packet arrives at the NIC, an interrupt is sent to the CPU. The CPU must stop what it’s doing, switch to kernel mode, process the packet through the network stack (IP, TCP/UDP layers), copy the data to a kernel buffer, and then copy it again to the user-space application’s buffer before the trading logic can even begin its work. This process is repeated for every packet.

If the market is volatile and the exchange is sending full snapshots, the system can become overwhelmed, spending more time on data logistics than on trading logic. This introduces significant, non-deterministic latency.

The optimized stack operates on a principle of direct, uninterrupted flow. With kernel bypass, the NIC writes incoming packet data directly into a ring buffer in the application’s memory. The application runs in a tight loop on a dedicated CPU core, constantly polling this buffer for new data. There are no interrupts, no context switches, and no kernel-mediated data copies.

When this is combined with an incremental data feed, the packets being polled are small and information-rich. The application’s task is simplified to applying a series of small changes to its in-memory representation of the order book. The result is a system characterized by extremely low and, critically, predictable latency. This predictability, or low jitter, is often more valuable than raw speed, as it allows for the fine-tuning of algorithms with a high degree of confidence in their execution timing.

Comparative Performance Metrics

The strategic value becomes evident when we quantify the differences. The following table provides a conceptual model of the performance characteristics of a traditional versus an optimized trading stack under load.

| Metric | Traditional Stack (Kernel, Full Snapshot) | Optimized Stack (Kernel Bypass, Incremental Feed) |

|---|---|---|

| Median Latency (Wire-to-App) | 20-50 microseconds | 1-5 microseconds |

| 99th Percentile Latency (Jitter) | > 200 microseconds | < 10 microseconds |

| CPU Load (Per Core) | High (Dominated by Context Switches) | High (Dominated by Polling), but Efficient |

| Data Volume Processed | High (Redundant Snapshot Data) | Low (Information-Dense Deltas) |

| System Determinism | Low | High |

Strategic Implications of Determinism

The reduction in latency is the most cited benefit, but the strategic advantage lies in the dramatic improvement in determinism. A system with low jitter behaves like a precision instrument. This allows for several strategic advantages:

- Tighter Spreads in Market Making ▴ A market maker’s risk is a function of how long they are exposed to the market with a stale price. With a deterministic, low-latency system, the market maker can update their quotes in near-perfect synchronization with the market, allowing them to quote tighter bid-ask spreads, attract more flow, and reduce adverse selection risk.

- Higher Confidence in Arbitrage ▴ Statistical arbitrage strategies rely on identifying and capturing fleeting price discrepancies. High jitter introduces uncertainty into the execution leg of the arbitrage, making it difficult to know if the opportunity will still exist when the order reaches the exchange. A deterministic system allows the arbitrage model to operate with higher confidence and capture opportunities that would be too risky for a slower, less predictable system.

- Improved Capacity for Complex Models ▴ By offloading the work of network processing from the CPU, kernel bypass frees up computational resources. This allows the trading system to run more sophisticated pricing and risk models in real-time, without sacrificing latency. The system can think more deeply about the market without falling behind.

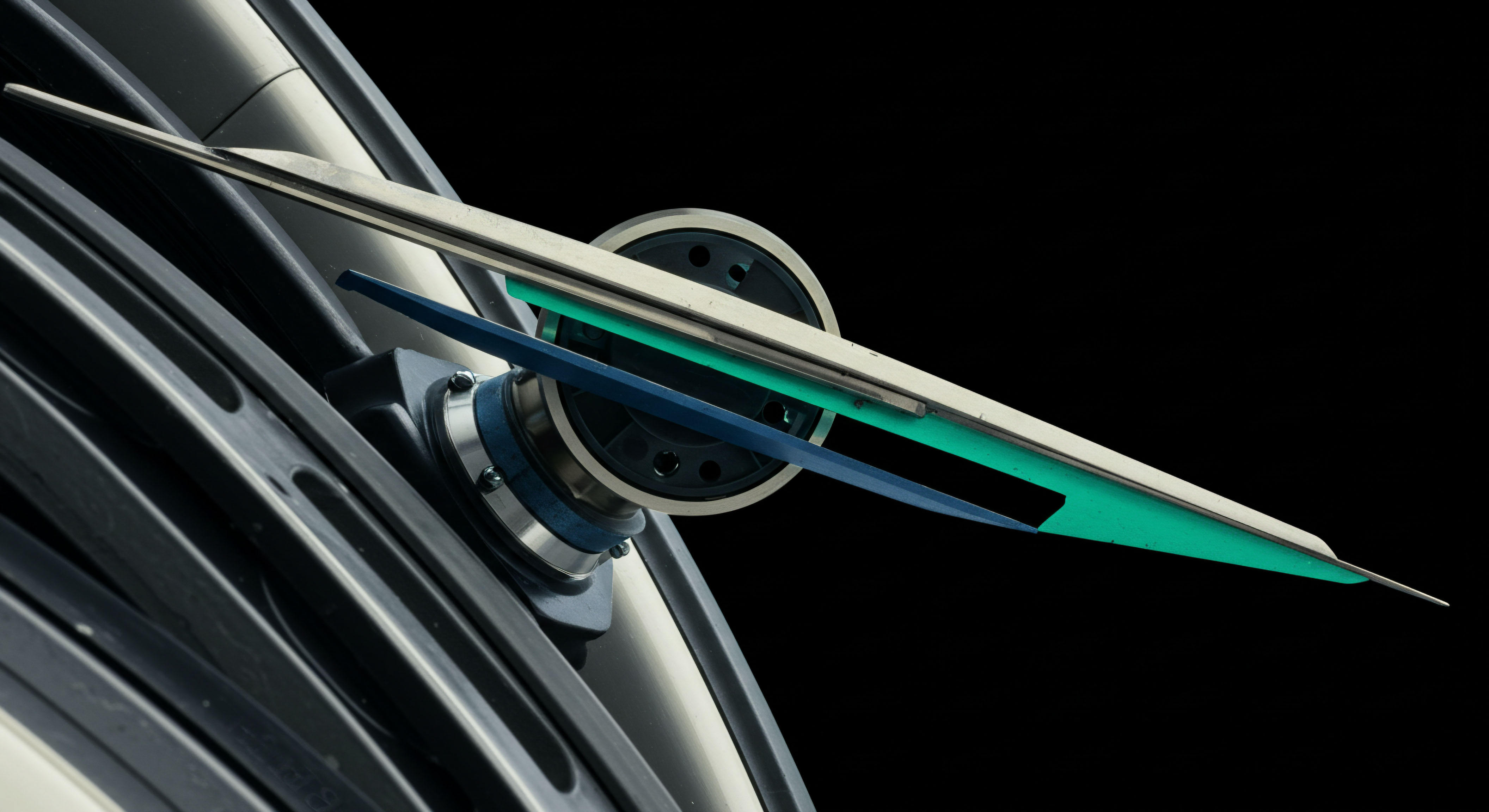

The combination of kernel bypass and incremental feeds transforms the trading server from a general-purpose computer into a specialized, high-performance data processing appliance.

This transformation is a strategic imperative for any firm competing on speed. It shifts the engineering focus from simply writing trading logic to designing a holistic system where every component, from the NIC to the CPU core to the application software, is optimized for a single purpose ▴ the frictionless flow of information.

Execution

The execution of a low-latency trading system built on kernel bypass and incremental feeds is an exercise in precision engineering. It requires a deep, multi-disciplinary understanding of hardware, networking, operating systems, and software design. The goal is to construct a data path that is as close to a straight line as possible, from the photon arriving at the fiber optic port to the electrical signal representing an order leaving the system. This section provides an operational guide to the key components and considerations in building and deploying such a system.

The Operational Playbook

Building a system capable of leveraging these technologies is a multi-stage process that demands meticulous attention to detail. Each choice has a direct impact on the final latency profile of the system.

- Hardware Selection ▴

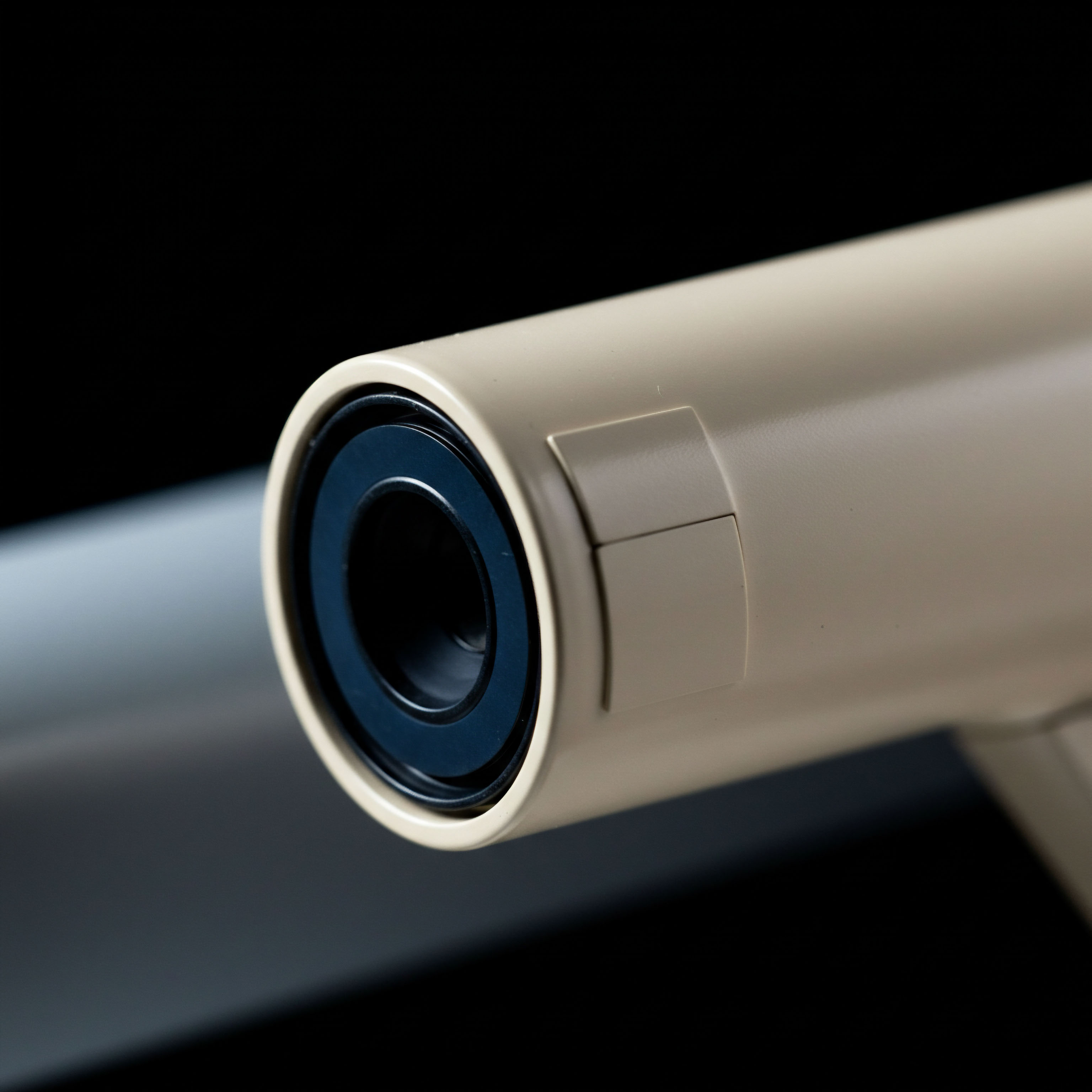

- Network Interface Cards (NICs) ▴ This is the foundation. Specialized NICs from vendors like Solarflare (now part of Xilinx/AMD) or Mellanox (now part of NVIDIA) are standard. These cards have on-board FPGAs (Field-Programmable Gate Arrays) and powerful processors designed for low-latency networking. They provide the hardware-level support for kernel bypass technologies like Solarflare’s Onload or Mellanox’s VMA.

- CPU ▴ The choice of CPU is critical. High clock speeds are important, but factors like cache size (L3 cache, in particular) and memory access architecture are paramount. The system should be designed to respect NUMA (Non-Uniform Memory Access) boundaries, ensuring that the trading application runs on a CPU core that is physically close to the PCIe slot of the NIC and the memory banks it uses.

- System Clock ▴ Precision timekeeping is essential. The system must be synchronized to a high-precision clock source, typically using the Precision Time Protocol (PTP), to accurately timestamp incoming data and outgoing orders for performance analysis and regulatory compliance.

- System Configuration ▴

- Operating System Tuning ▴ A stripped-down Linux distribution is the typical choice. The OS must be tuned to minimize sources of jitter. This includes disabling unnecessary services, isolating specific CPU cores for the trading application, and using kernel boot parameters like isolcpus, nohz_full, and rcu_nocbs to prevent the kernel from scheduling other tasks on the critical cores.

- BIOS/UEFI Settings ▴ Low-level hardware settings must be optimized for performance. This involves disabling power-saving states (C-states), setting the performance profile to maximum, and configuring memory access modes for the lowest latency.

- Software Architecture ▴

- Kernel Bypass Implementation ▴ The application must be written to use a kernel bypass library. This could be a commercial solution like Solarflare’s Onload, which can accelerate standard socket-based applications with minimal code changes, or a more intensive framework like the Data Plane Development Kit (DPDK), which requires the application to be explicitly designed around its polling-mode driver model.

- Market Data Handler ▴ This is the component that consumes the incremental feed. It must be highly efficient, capable of parsing the exchange’s specific protocol (e.g. FIX/FAST, SBE) and applying the updates to an in-memory representation of the order book. This often involves using lock-free data structures to avoid contention between the thread receiving the data and the threads running the trading logic.

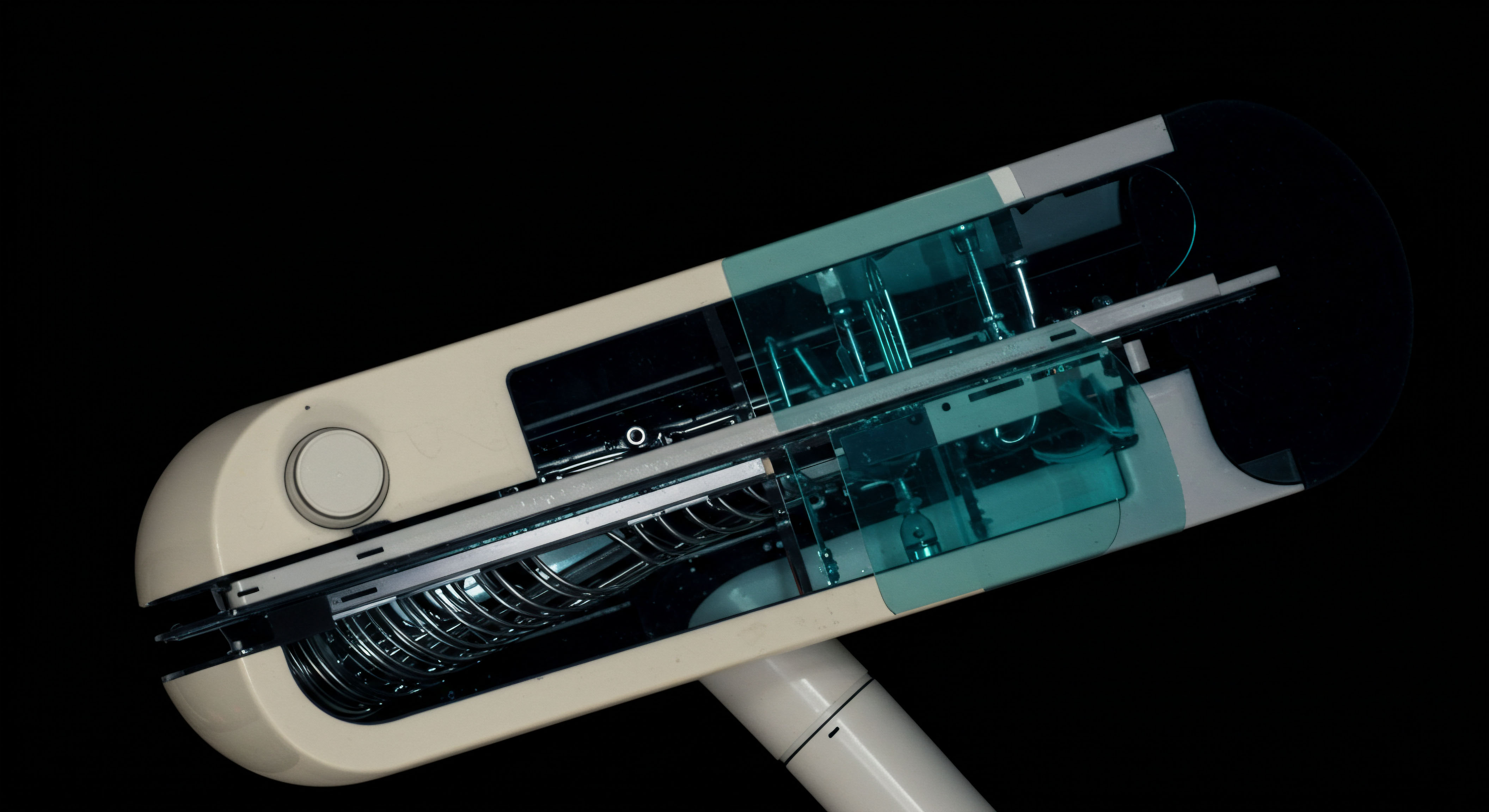

- CPU Core Affinity ▴ The different threads of the application must be pinned to specific, isolated CPU cores. For example, one core might be dedicated solely to polling the NIC for new packets, another to parsing the data and updating the order book, and several others to running the trading strategy and risk checks. This prevents the operating system from moving the threads between cores, which would destroy cache locality and introduce latency.

Quantitative Modeling and Data Analysis

To understand the impact of these execution choices, we can model the latency budget of a single market data packet. The following table provides a hypothetical, yet realistic, breakdown of the time spent in each stage of processing for both a traditional and an optimized system. The values are expressed in nanoseconds (ns).

| Processing Stage | Traditional Stack (ns) | Optimized Stack (ns) | Notes |

|---|---|---|---|

| Wire to NIC Buffer | ~200 | ~200 | Physics-limited (speed of light in fiber, hardware serialization). |

| NIC to Kernel | ~5,000 | N/A | Dominated by interrupt generation and handling. |

| Kernel Network Stack | ~10,000 | N/A | TCP/IP processing, socket buffer management. |

| Kernel to User Space Copy | ~3,000 | N/A | A significant source of latency and CPU load. |

| NIC to User Space (DMA) | N/A | ~800 | Direct Memory Access via kernel bypass. |

| Application Wakeup/Polling | ~2,000 | ~100 | Context switch vs. reading from a polled ring buffer. |

| Total Wire-to-App Latency | ~20,200 ns (20.2 µs) | ~1,100 ns (1.1 µs) | An order of magnitude improvement. |

The execution of a low-latency system is a process of eliminating nanoseconds at every stage of the data path.

Predictive Scenario Analysis

Consider a scenario ▴ a major central bank makes a surprise interest rate announcement. The market for equity index futures becomes extremely volatile. A firm using a traditional stack, “Legacy Trading,” and a firm using an optimized stack, “Helios Capital,” are both competing to capture arbitrage opportunities created by the news.

The moment the announcement hits the wires, the exchange’s market data gateways are flooded with activity. The volume of messages increases by a factor of 100. Legacy Trading’s system, which relies on full snapshots, is now receiving massive data packets every few milliseconds. Their servers’ CPUs are immediately pegged at 100%, consumed by network interrupts and context switching as the kernel struggles to deliver the data to the application.

Their trading application experiences latency spikes of over 500 microseconds, and the data it is acting on is hopelessly stale. By the time it generates an order, the opportunity has vanished.

Helios Capital’s system, in contrast, is built for this exact scenario. Their kernel bypass stack continues to deliver the incremental data feed directly to the application’s memory with sub-microsecond latency. Because the feed is incremental, the data volume, while higher, is manageable. The dedicated CPU core running the data handler is busy, but it keeps up with the flow.

The trading logic, running on its own isolated cores, receives a steady, predictable stream of updates. It is able to see the market evolving in real-time, identify a price discrepancy between the futures contract and its constituent stocks, and fire off an order in under 5 microseconds. The order reaches the exchange and is executed before Legacy Trading’s system has even finished processing the first wave of data. In this environment, Helios Capital is able to execute hundreds of profitable trades, while Legacy Trading is effectively frozen out of the market, paralyzed by its own technology.

System Integration and Technological Architecture

The final piece of the puzzle is the integration of this low-latency data path with the rest of the trading infrastructure. The market data handler, which now holds a real-time image of the order book, becomes the central source of truth for the entire system. It must provide this data to the various strategy and risk modules through highly efficient inter-thread communication mechanisms, such as shared memory or lock-free queues. The signals generated by the trading strategies must then be passed to an execution module, which is responsible for constructing and sending the order.

This outbound path must also be optimized, often using the same kernel bypass techniques to send the order packet to the NIC with minimal delay. The entire system, from ingress to egress, must be conceived as a single, integrated, low-latency pipeline. This requires a level of system-level design and optimization that goes far beyond traditional application development, but it is the price of entry into the competitive world of high-frequency trading.

References

- Bilokon, Paul. “Low-Latency Programming & High Frequency Trading.” WBS Training, 2025.

- NVIDIA Corporation. “Accelerating Electronic Trading – End-to-End Networking Solutions.” NVIDIA Whitepaper, 2023.

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- Intel Corporation. “Data Plane Development Kit (DPDK) ▴ The Path to High-Performance Packet Processing.” Intel Whitepaper, 2021.

- Lehalle, Charles-Albert, and Sophie Laruelle. Market Microstructure in Practice. World Scientific Publishing, 2018.

- Solarflare Communications, Inc. “OpenOnload ▴ Application Acceleration for Everyone.” Solarflare Whitepaper, 2019.

- Jefferis, David. High-Frequency Trading ▴ A Practical Guide to Algorithmic Strategies and Trading Systems. John Wiley & Sons, 2017.

- Podobas, Artur, et al. “A Survey on Kernel Bypass Networks.” ACM Computing Surveys, vol. 53, no. 2, 2020, pp. 1-38.

Reflection

The Unseen Frontier

The mastery of latency is a journey inward. While the external world measures speed in proximity to exchanges, the most significant gains are found within the architecture of the trading system itself. The principles of kernel bypass and incremental data feeds are not merely technical optimizations; they represent a philosophical shift in how a firm approaches the market. They demand a view of the trading system not as a collection of disparate software components, but as a single, cohesive instrument, finely tuned to the rhythms of the market.

The knowledge gained here is a component in a larger operational framework. The ultimate question is not whether these technologies can reduce latency, but how a deep, systemic understanding of them can be integrated into a firm’s culture, strategy, and risk management to create a durable and defensible competitive edge. The true frontier is the space between the arrival of information and the execution of a decision, and it is in this unseen space that the future of trading will be decided.

Glossary

Trading System

High-Frequency Trading

Context Switches

Trading Logic

Network Interface Card

Trading Application

Low-Latency Trading

Kernel Bypass

Data Feeds

Order Book

Incremental Feeds

Optimized Stack

Market Data

Traditional Stack

Jitter

Memory Access

Numa

Data Plane Development Kit

Dpdk