Concept

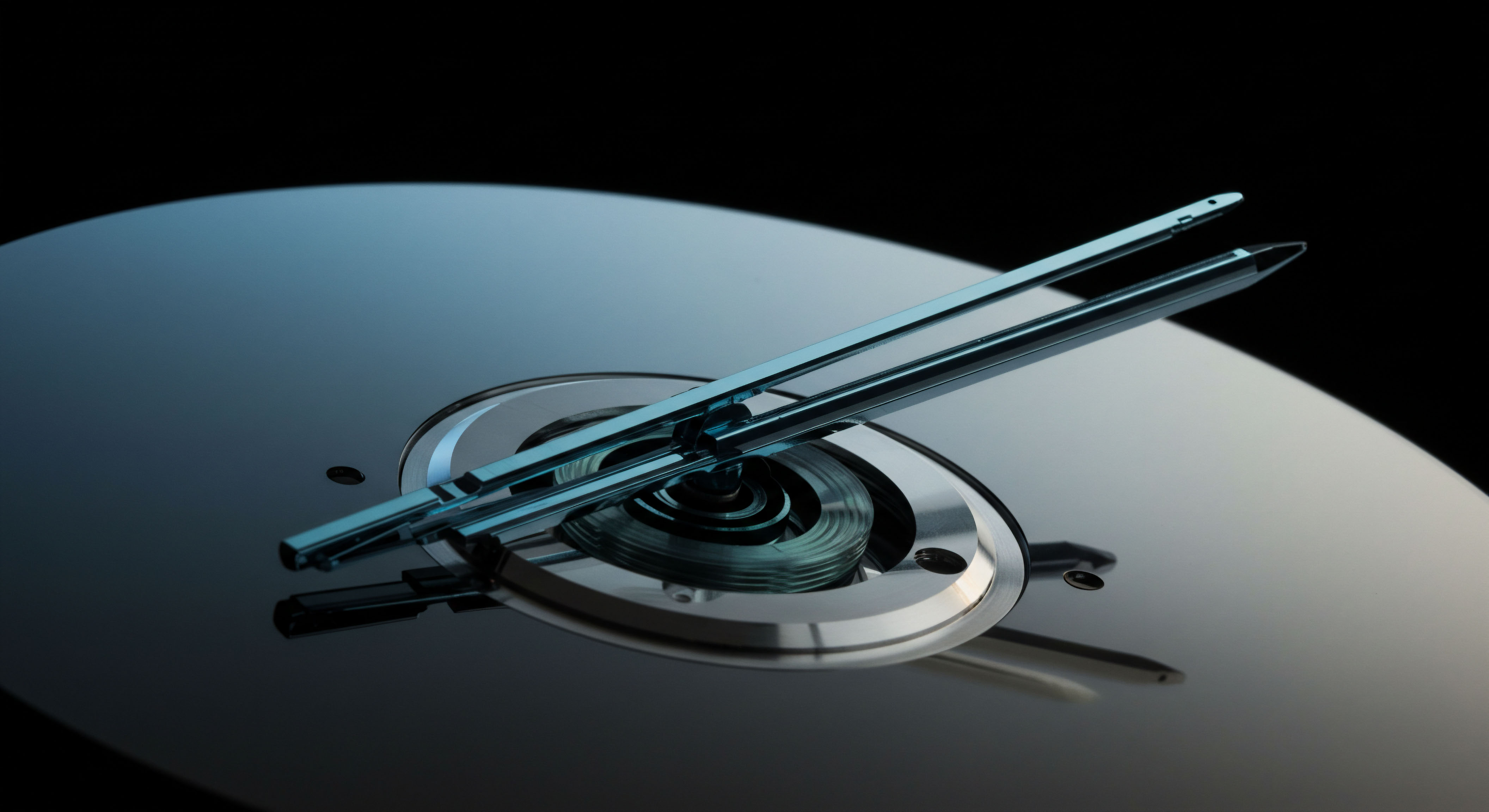

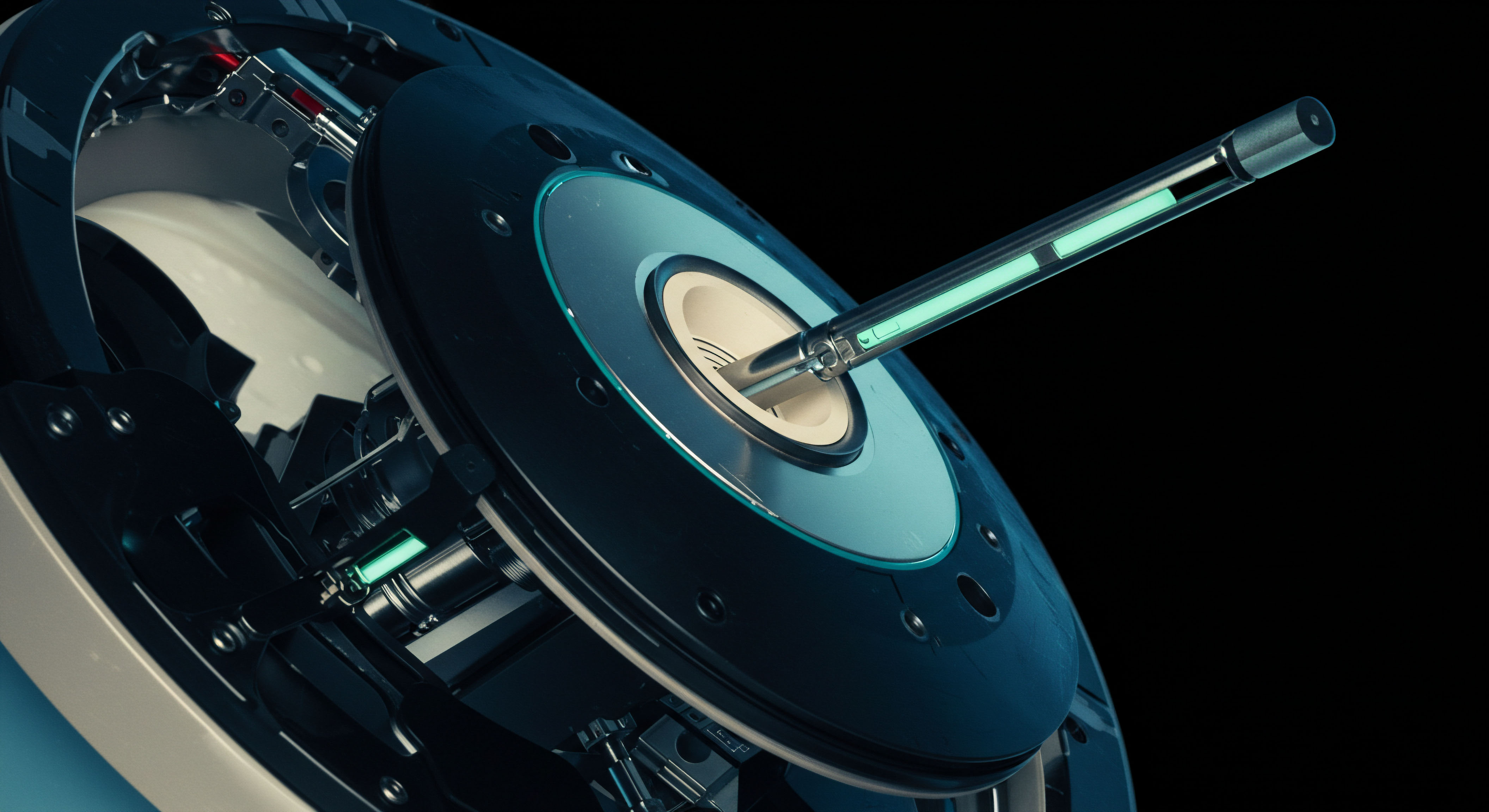

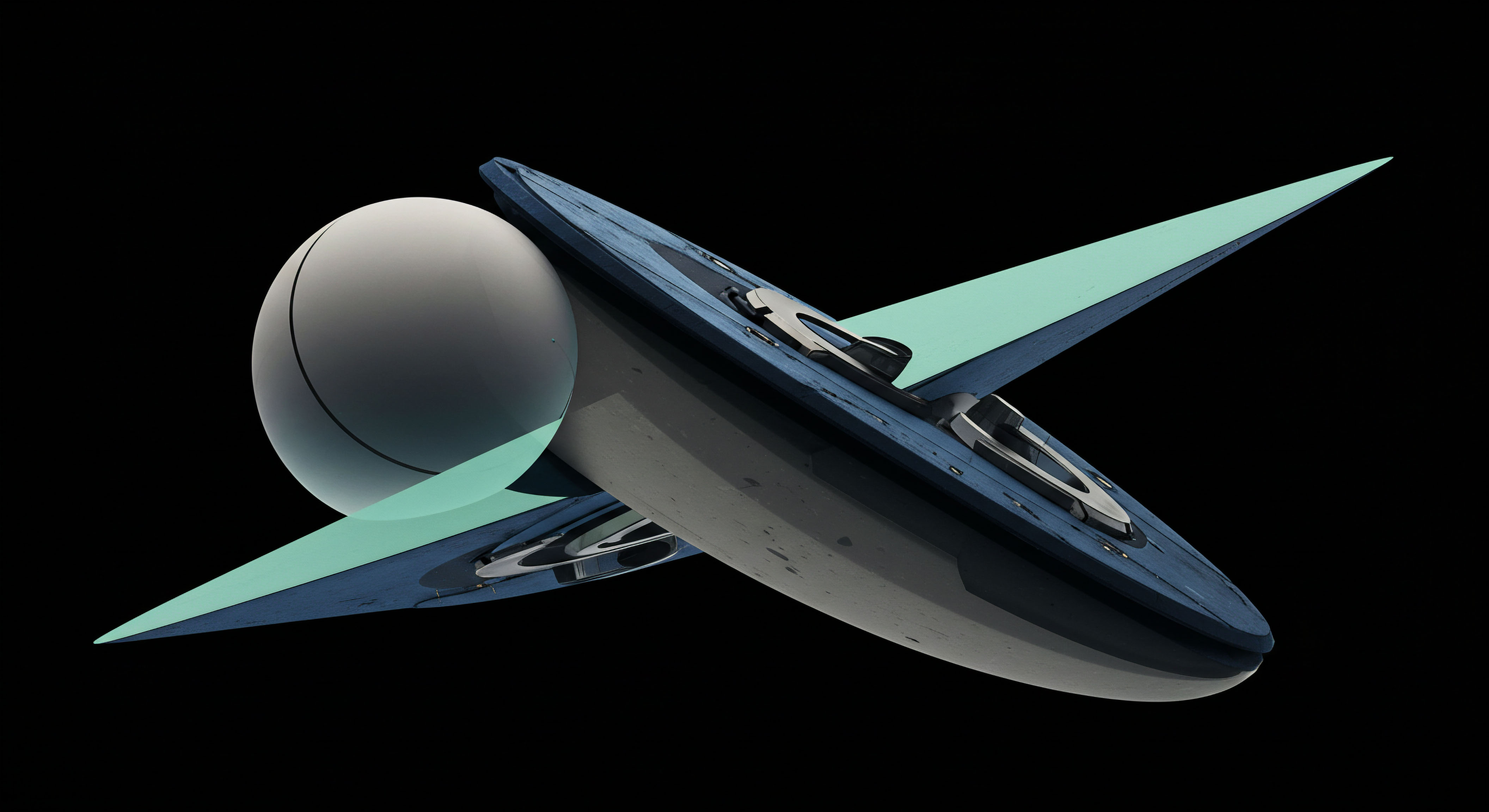

The decision to integrate hardware acceleration into a firm’s operational core is a fundamental re-architecting of its central nervous system. It represents a calculated move from a purely software-defined logic to a physically instantiated one, where algorithms are no longer just executed but are etched into the very silicon that processes market data. This transition acknowledges a physical reality of modern capital markets ▴ the speed of light is a non-negotiable constraint, and the latency introduced by software-based processing, however optimized, constitutes a competitive drag.

The adoption of technologies like Field-Programmable Gate Arrays (FPGAs) and Graphics Processing Units (GPUs) is the firm’s response to this physical boundary. It is an admission that the ultimate performance ceiling is defined by physics, and the only way to approach that ceiling is to translate strategic logic directly into hardware.

At its heart, this is a paradigm shift in how a firm perceives and interacts with time. In a software-centric model, an algorithm is a set of instructions interpreted and executed by a general-purpose processor. Each step, each decision, involves layers of abstraction ▴ from the operating system to the application layer ▴ and each layer introduces microseconds of delay, or “jitter.” This variability, while minuscule in human terms, is a significant source of uncertainty in an environment where execution priority is determined by nanoseconds. Hardware acceleration collapses these layers.

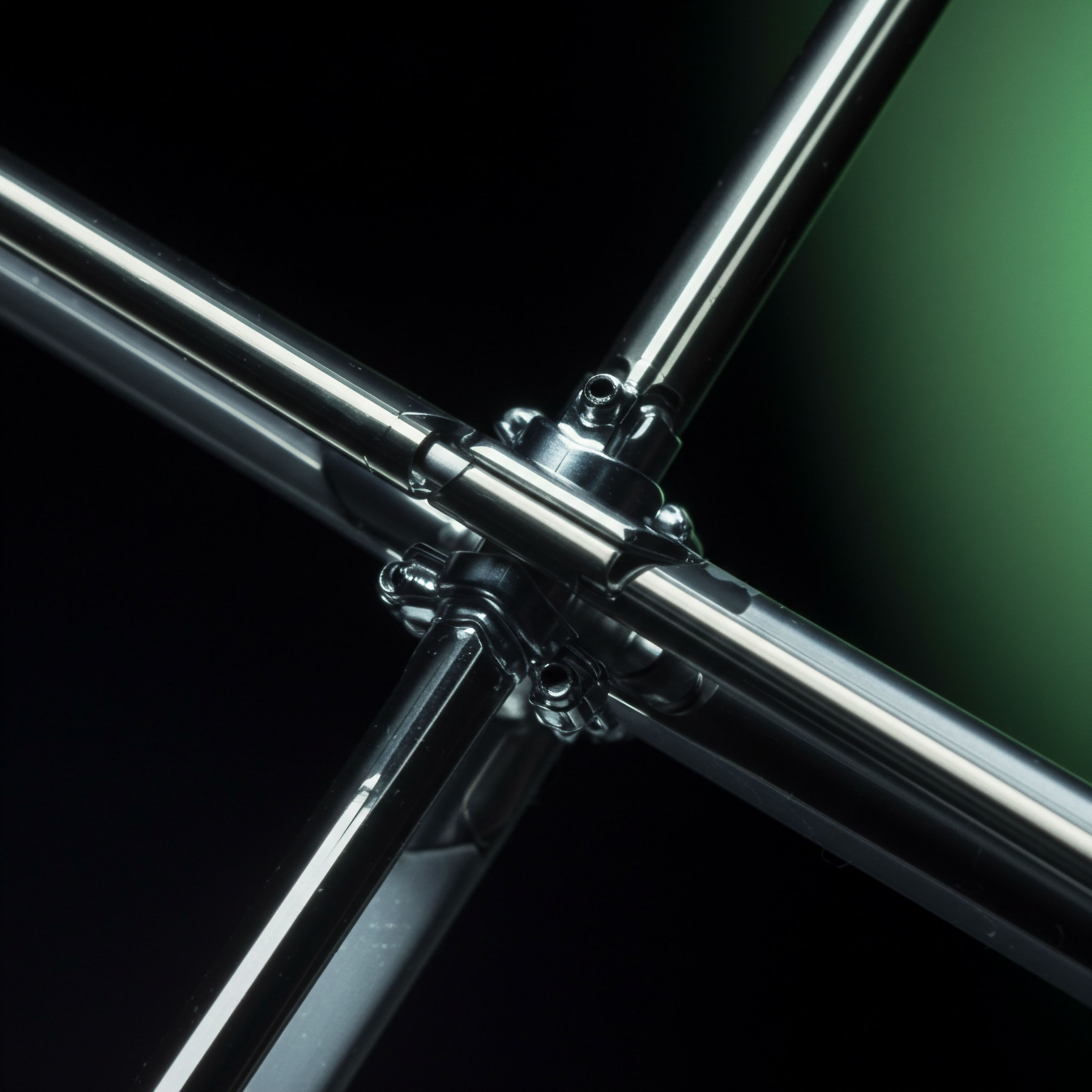

An algorithm compiled onto an FPGA creates a dedicated, deterministic circuit. The logic exists as a physical pathway. When market data enters the system, it flows through this circuit, and the reaction is as close to instantaneous as electronic engineering allows. The firm is, in effect, building a bespoke processor designed to do one thing with supreme efficiency ▴ execute its trading strategy.

The integration of hardware acceleration transforms a firm’s operational model from executing instructions in software to processing data through physically instantiated logic.

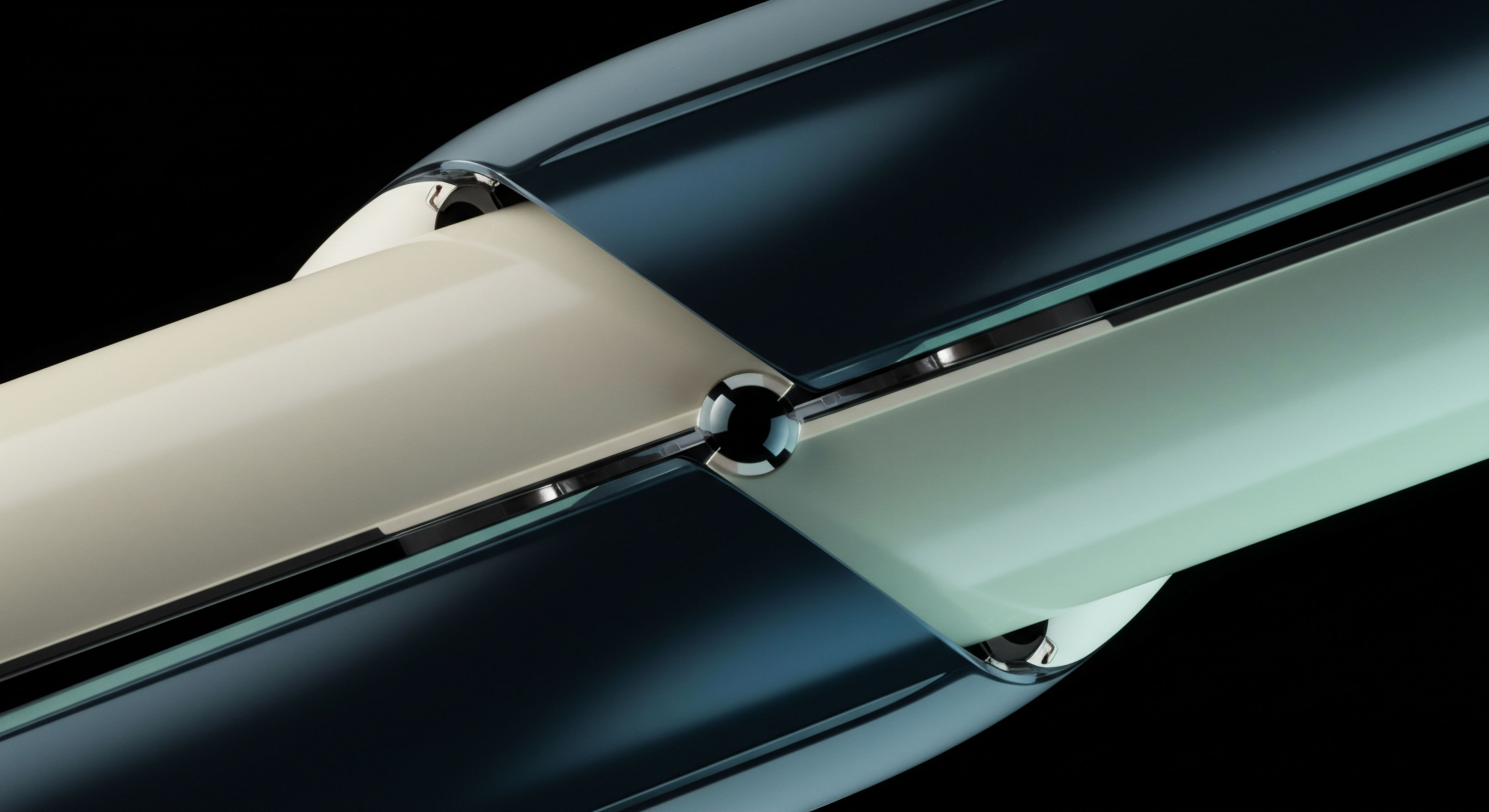

This commitment to physical logic has profound implications. It changes the very nature of technological assets. A software algorithm is malleable, easily changed and redeployed. A hardware-based strategy, while reprogrammable in the case of FPGAs, represents a more significant investment in a specific logical architecture.

The development lifecycle is longer, the required expertise is rarer, and the cost of error is higher. Yet, the payoff is a level of performance and predictability that software alone cannot replicate. This is the central bargain ▴ a firm trades the flexibility of pure software for the deterministic, low-latency performance of specialized hardware. This choice signals a maturation of the firm’s strategy, moving from a focus on the abstract logic of a trading idea to the physical reality of its implementation.

The question ceases to be ‘what is our strategy?’ and becomes ‘how is our strategy physically manifested at the point of execution?’. This reframing is the true conceptual impact of hardware acceleration adoption.

What Is the Core Architectural Shift?

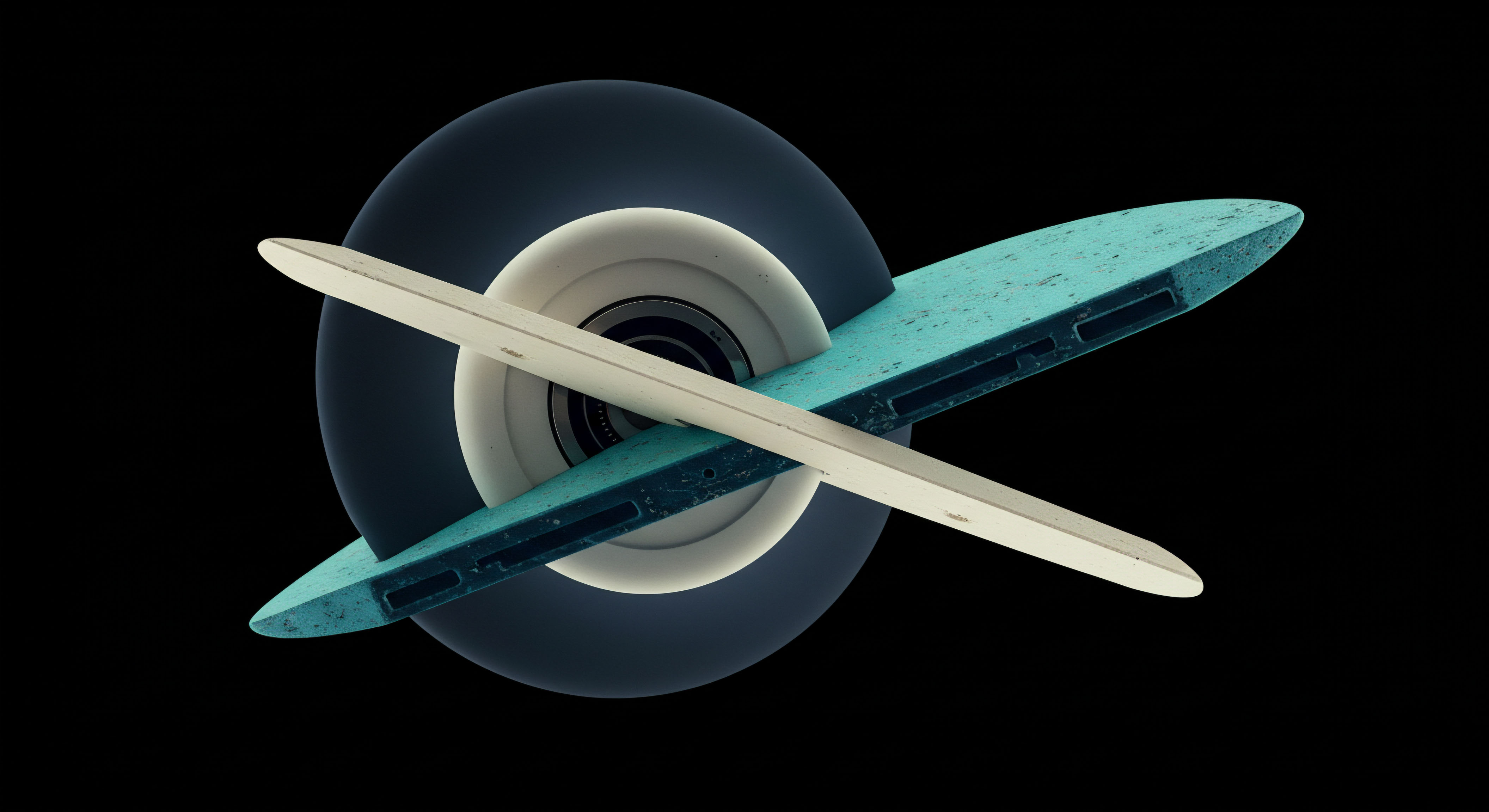

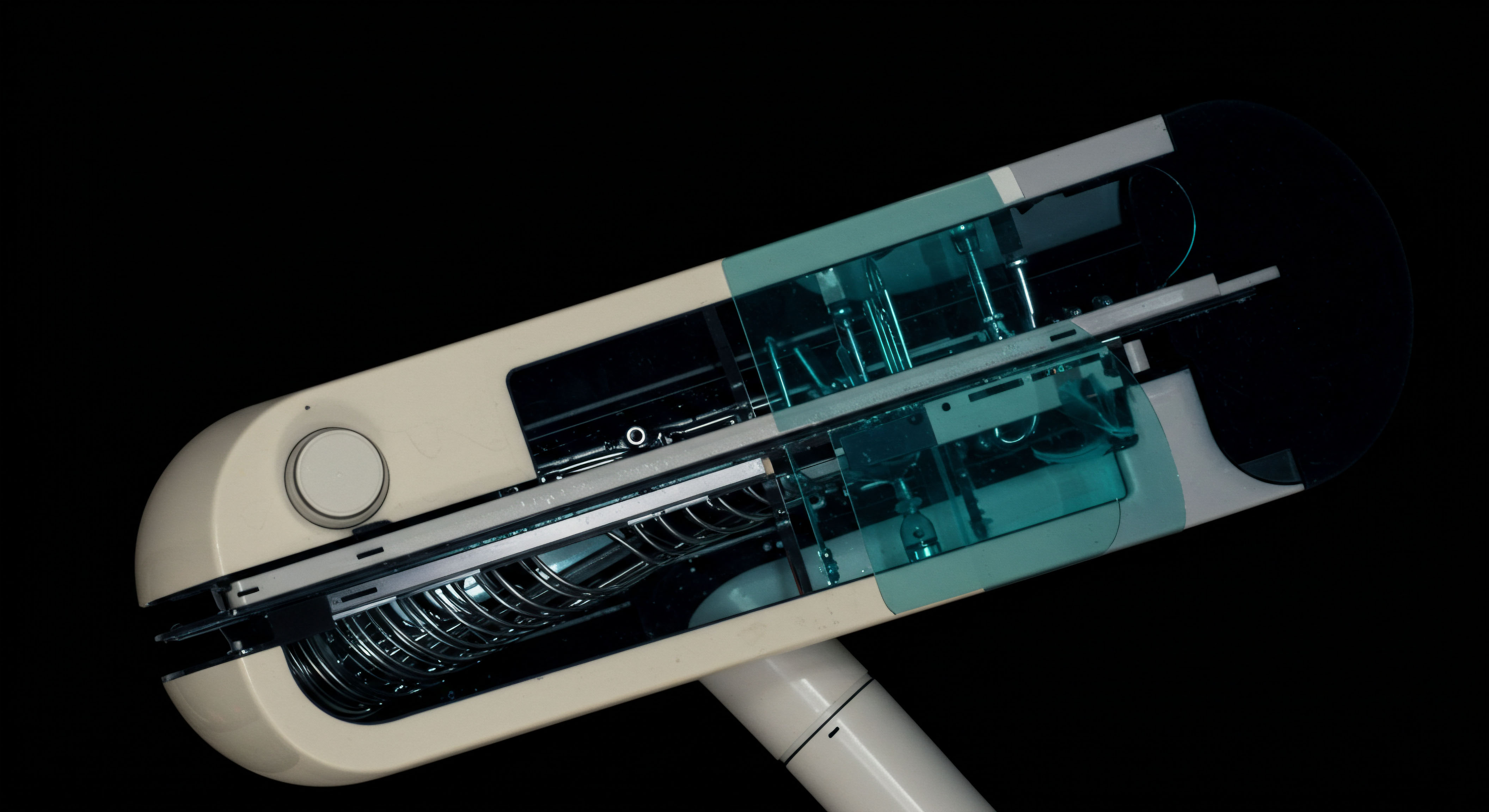

The core architectural shift is from sequential processing on general-purpose CPUs to parallel and pipeline processing on specialized hardware. A CPU is a master of all trades, designed to handle a vast array of tasks by loading and executing instructions one after another at incredible speeds. This versatility is its strength in a corporate IT environment but becomes a bottleneck in high-frequency trading. Market data arrives in parallel torrents, and strategic decisions often involve performing the same calculation on thousands of data points simultaneously.

A CPU must cycle through these tasks, creating a queue. Specialized hardware, like GPUs, contains thousands of smaller, simpler cores designed for parallel computation. They can perform the same mathematical operation on a massive dataset in a single clock cycle. FPGAs take this a step further by allowing the creation of a custom data pipeline.

Data flows through a series of logic gates that perform operations in a continuous stream, without the overhead of instruction fetching and decoding inherent in a CPU. This architectural change directly mirrors the nature of the problem ▴ processing a massive, parallel stream of market data to make a time-critical decision.

This move also represents a shift from a stateless to a stateful processing model. In many software systems, each transaction is treated as a discrete event. Hardware acceleration, particularly with FPGAs, allows the firm to build a system that maintains a persistent, real-time state of the market within the hardware itself. The FPGA can be programmed to hold the order book, track liquidity changes, and update risk calculations continuously.

Incoming data packets do not require a round trip to a software application to be contextualized; they are processed against the current state held in the silicon. This creates a system with an incredibly low-level awareness of the market, capable of reacting to changes with a speed that is simply unachievable when there is a separation between the data-receiving hardware and the decision-making software. The firm’s strategy becomes an embedded, stateful entity that lives directly on the network boundary.

The Physics of Performance

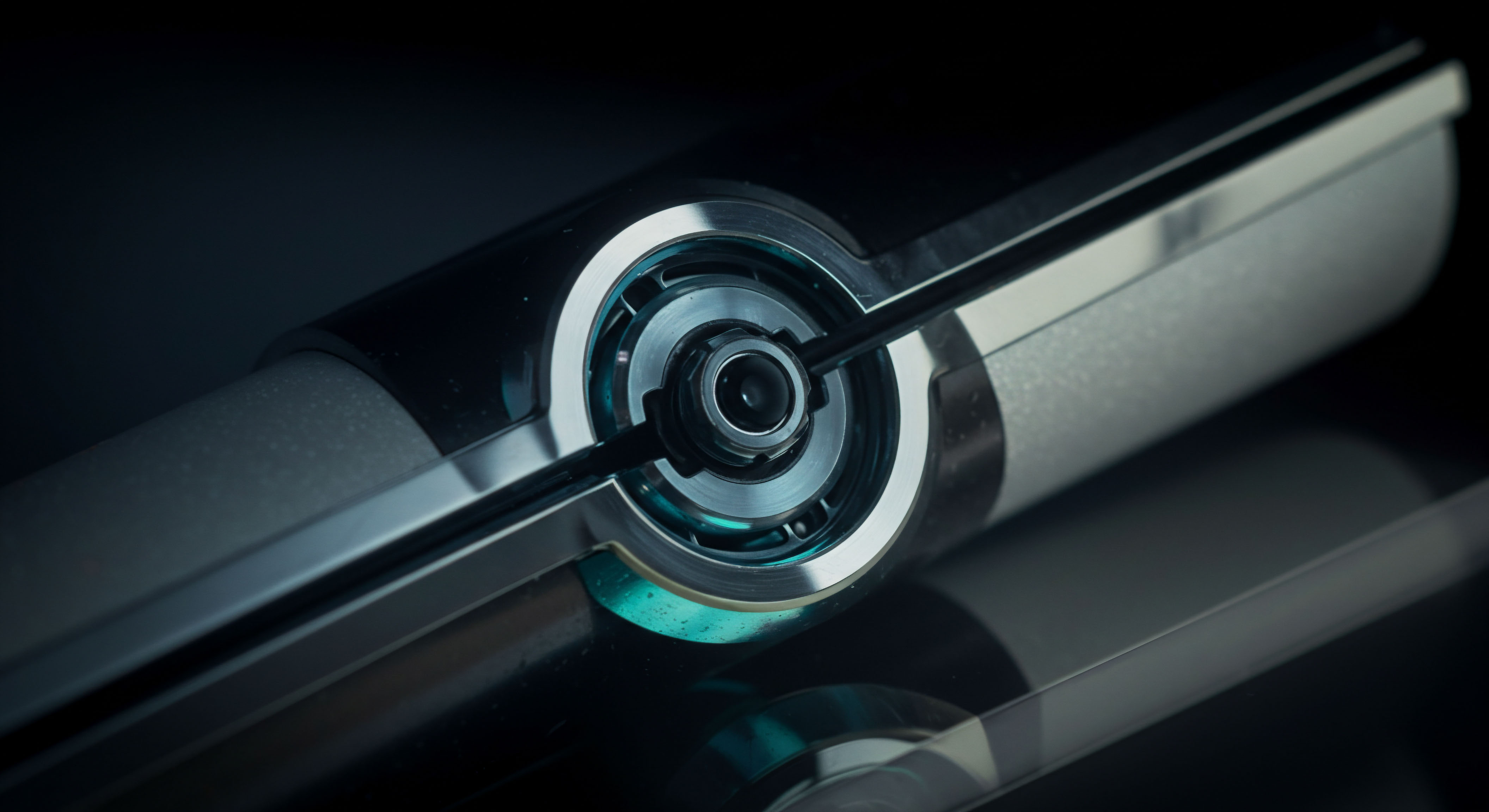

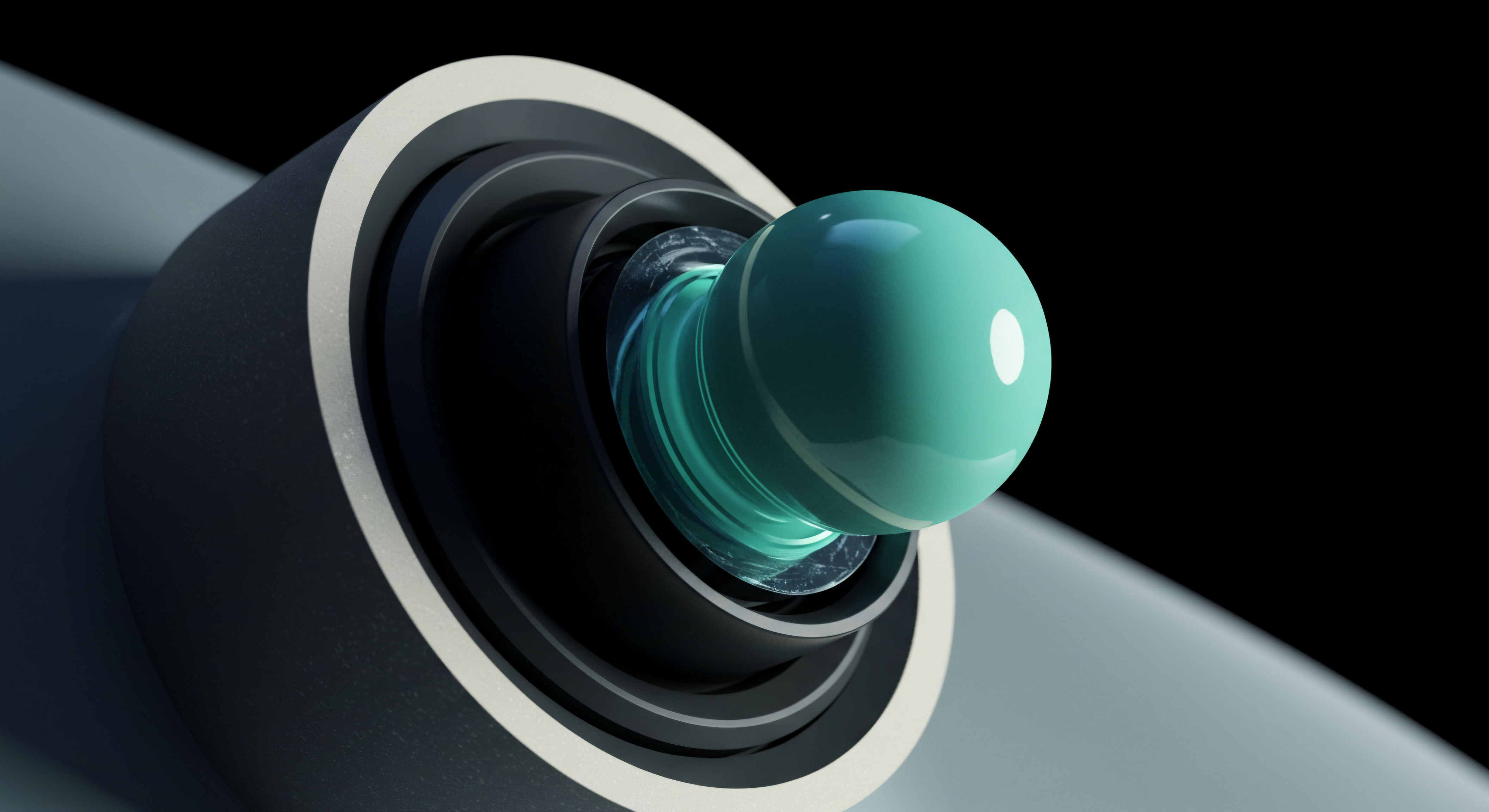

Understanding the adoption of hardware acceleration requires an appreciation for the physics of data movement and computation. In electronic markets, competitive advantage is measured in nanoseconds, the time it takes light to travel approximately one foot. The physical distance between a firm’s servers and the exchange’s matching engine is a critical factor, leading to the co-location race. Hardware acceleration is the logical next step in this optimization process.

Once a firm has minimized the physical distance, the next frontier of latency reduction is within its own server rack. The journey of a market data packet from the network card, through the server’s operating system, to the application software, and back out again is a journey measured in microseconds. Each step ▴ each buffer copy, each context switch, each instruction fetch ▴ adds latency.

Hardware acceleration seeks to shorten this internal journey to the absolute minimum. By placing FPGA cards directly in the data path, firms can process data packets as they arrive from the network, a practice known as “bump-in-the-wire” processing. The FPGA can perform tasks like data filtering, normalization, and even order book building before the data ever touches the server’s main CPU. This is a profound change.

The server’s CPU is no longer the primary brain; it is a higher-level controller, tasked with managing the strategy running on the FPGA. The most time-critical functions are offloaded to the hardware that is physically closest to the market. This approach acknowledges that every millimeter of copper trace, every layer of software abstraction, is a source of latency that must be engineered away. It is a strategy built on the principles of electrical engineering and physics as much as it is on financial theory.

Strategy

The integration of hardware acceleration is a strategic declaration that a firm intends to compete on the axis of time. This decision ripples through every facet of its technology and talent strategy, forcing a fundamental realignment of resources, priorities, and culture. It is a move to re-architect the firm’s competitive posture, building a moat based on deterministic execution speed and predictability. The primary strategic objective is to reduce latency and eliminate jitter, the variability in processing times that can be just as detrimental as high latency itself.

A firm with deterministic, low-latency infrastructure can implement strategies that are unavailable to its software-based competitors. It can react to market events faster, capture fleeting arbitrage opportunities, and provide liquidity with a higher degree of confidence, knowing that its orders will reach the market with predictable timing.

This shift compels a complete re-evaluation of the technology stack. The stack ceases to be a collection of software applications running on commodity hardware and becomes a highly integrated, bespoke system where hardware and software are co-designed. The technology strategy must now encompass the entire data path, from the fiber optic cable entering the data center to the logic gates on the FPGA. This requires a new set of design principles centered on minimizing data movement and processing overhead.

The firm’s architects must think in terms of data pipelines and clock cycles, not just application threads and processes. This holistic view is essential because the performance of the entire system is dictated by its slowest component. A world-class FPGA is of little use if it is fed by a slow software process. Therefore, the technology strategy becomes one of end-to-end optimization.

Adopting hardware acceleration is a strategic commitment to competing on the dimension of time, necessitating a complete co-design of hardware and software systems.

Consequently, the talent strategy undergoes a radical transformation. The demand for pure software developers, while still present, is supplemented by a pressing need for a new class of engineer. These are individuals who exist at the intersection of computer science, electrical engineering, and quantitative finance. They must be able to translate a financial model into a register-transfer level (RTL) design, understand the timing constraints of a silicon chip, and debug a trading strategy at the level of individual logic gates.

This talent is exceptionally rare and highly sought after. Firms can no longer simply recruit from the ranks of top computer science programs; they must actively cultivate relationships with electrical engineering departments and compete with semiconductor companies for the best minds. The talent strategy must evolve from one of recruitment to one of strategic acquisition and internal development, creating an environment where this unique hybrid talent can thrive.

Redefining the Technology Roadmap

A firm’s technology roadmap must be completely redrawn following the decision to adopt hardware acceleration. The roadmap shifts from a software-centric upgrade cycle to a hardware-centric development lifecycle. This involves long-term planning for silicon design, fabrication, and testing, which operates on a different timescale than agile software development. The roadmap must account for the procurement of specialized hardware, the development of custom firmware, and the creation of new testing and validation methodologies.

The following table illustrates the key differences between a traditional software-centric roadmap and a hardware-accelerated roadmap:

| Aspect | Software-Centric Roadmap | Hardware-Accelerated Roadmap |

|---|---|---|

| Primary Asset | Proprietary software algorithms and applications. | Integrated hardware/software systems; custom silicon. |

| Development Cycle | Agile sprints (2-4 weeks); continuous integration/deployment. | Long-term design cycles (months/years); multiple stages of simulation, synthesis, and physical testing. |

| Key Milestones | Feature releases, version upgrades, API enhancements. | Tape-out, silicon bring-up, firmware releases, system integration. |

| Resource Allocation | Investment in developer headcount, software licenses, and cloud computing resources. | Investment in FPGA/ASIC design tools, fabrication costs, lab equipment, and specialized engineering talent. |

| Risk Profile | Bugs in logic, performance bottlenecks, system crashes. | Design flaws in silicon (costly to fix), timing closure failures, hardware failures. |

This new roadmap necessitates a change in how the firm views technological investment. It is a shift from operational expenditure (software licenses, cloud services) to capital expenditure (custom hardware, design tools). This has significant financial implications and requires buy-in from the highest levels of management. The firm is building a long-term, defensible asset, and the roadmap must reflect this strategic commitment.

How Does Talent Acquisition and Retention Evolve?

The talent strategy must evolve to address a candidate-driven market where the required skills are scarce and the competition is fierce. A firm’s talent acquisition team can no longer rely on standard recruiting channels. It must build a presence in the specialized communities where hardware engineers and FPGA designers congregate.

This includes sponsoring academic research, participating in hardware engineering conferences, and contributing to open-source hardware projects. The firm’s brand must be repositioned to appeal to this new talent pool, emphasizing the exciting engineering challenges and the opportunity to work on cutting-edge technology.

Retention becomes a critical focus. These highly specialized engineers are often motivated by challenging problems and the opportunity for greenfield development. The firm must create a culture that supports deep engineering work, providing them with the resources, autonomy, and recognition they need. This can include:

- Dedicated Research Labs ▴ Providing state-of-the-art equipment for hardware design, testing, and validation.

- Dual Career Ladders ▴ Allowing engineers to advance to senior positions based on their technical contributions, without being forced into a management track.

- Intellectual Property Incentives ▴ Rewarding engineers for developing novel hardware designs and patents.

- Cross-Disciplinary Collaboration ▴ Fostering a close working relationship between hardware engineers, software developers, and quantitative analysts to ensure that the technology being built is aligned with the firm’s trading strategies.

The talent strategy becomes less about filling seats and more about cultivating a world-class engineering organization. It is an investment in human capital that is just as critical as the investment in silicon.

The New Economics of Trading Infrastructure

The adoption of hardware acceleration fundamentally alters the economics of a firm’s trading infrastructure. The cost structure shifts from a model dominated by recurring software costs and developer salaries to one with significant upfront capital investment in hardware design and fabrication. This requires a different approach to budgeting and financial planning, one that is more akin to a manufacturing or semiconductor company than a traditional financial firm. The firm must be prepared to make large, long-term investments in its infrastructure with the expectation of a significant competitive return over time.

The return on investment (ROI) calculation also changes. While a software project might be evaluated based on its ability to generate revenue or reduce costs in the short term, the ROI of a hardware project is more strategic. It is measured by the new classes of trading strategies it enables, the reduction in execution uncertainty, and the creation of a long-term, defensible competitive advantage. The economic model must account for the strategic value of being at the technological frontier.

This often involves a commitment to a multi-generational technology plan, where the lessons learned from one generation of hardware are used to inform the design of the next. This sustained investment is what creates a lasting technological edge.

Execution

The execution of a hardware acceleration strategy is a complex, multi-stage process that demands meticulous planning and deep expertise. It is the phase where strategic intent is translated into physical reality. The process begins with a rigorous assessment of the firm’s existing capabilities and the identification of the specific trading functions that will benefit most from acceleration. This is a critical filtering step.

Not all algorithms are suitable for hardware implementation. The ideal candidates are those that are computationally intensive, highly parallelizable, and central to the firm’s most time-sensitive strategies. This could include tasks like market data processing, order book construction, risk calculation, or the execution logic for a specific arbitrage strategy.

Once the target functions have been identified, the firm faces a critical build-versus-buy decision. It can choose to purchase off-the-shelf FPGA solutions from specialized vendors, which offer a faster time-to-market but less customization. Alternatively, it can embark on the more arduous path of building a bespoke solution in-house. This path offers the potential for a unique competitive advantage but requires a significant investment in talent and resources.

The choice depends on the firm’s risk appetite, its existing engineering capabilities, and the strategic importance of the function being accelerated. For many, a hybrid approach is optimal, using vendor solutions for common tasks like data feed handling while focusing in-house efforts on the “secret sauce” of the firm’s proprietary algorithms.

Executing a hardware acceleration strategy involves a disciplined process of identifying suitable algorithms, making a strategic build-versus-buy decision, and managing a complex hardware development lifecycle.

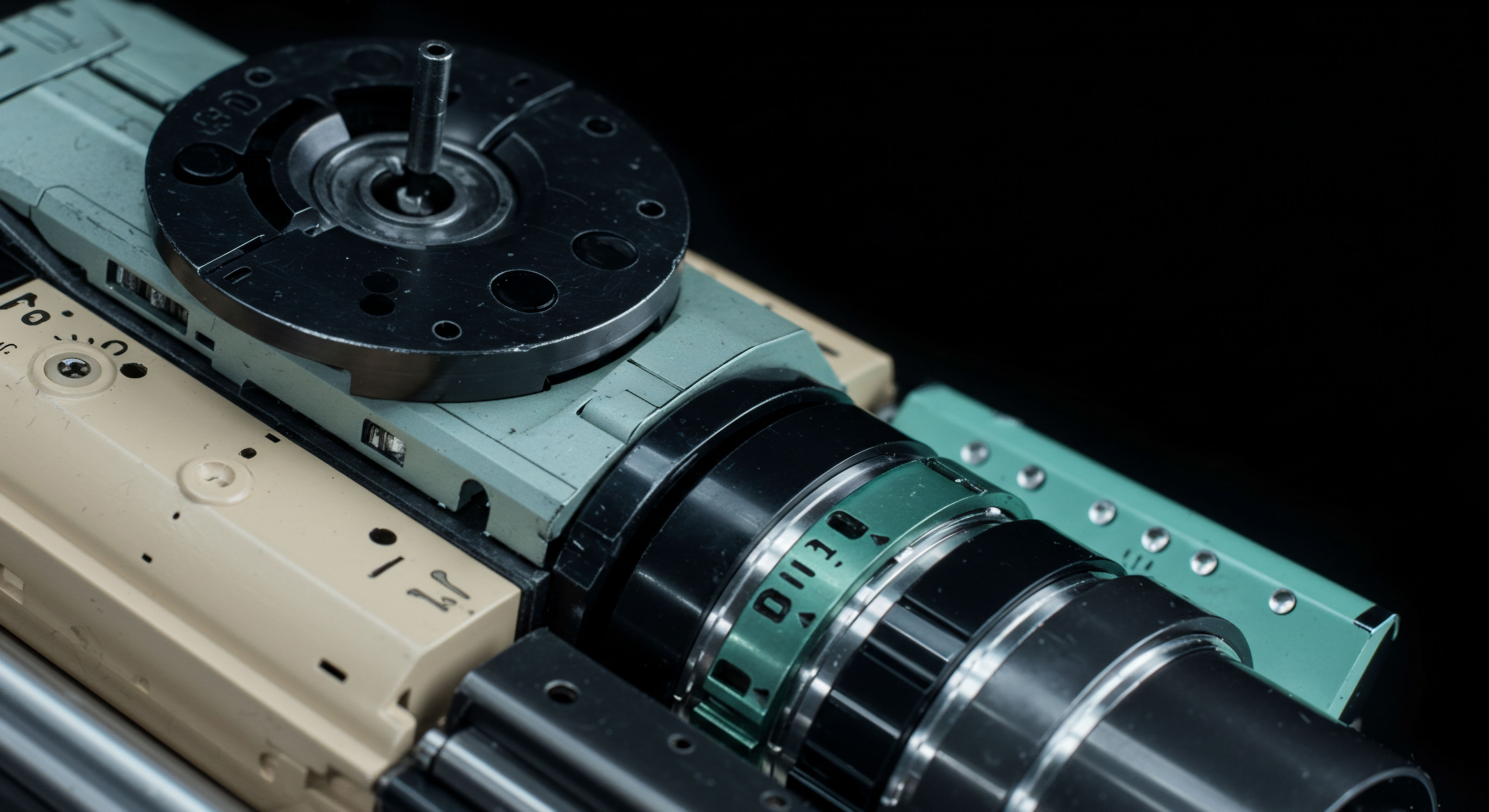

The execution phase itself is a highly structured engineering discipline. It follows a well-defined lifecycle that includes requirements specification, architectural design, implementation in a hardware description language (HDL) like Verilog or VHDL, extensive simulation and verification, synthesis (the process of converting the HDL code into a gate-level netlist), and finally, place-and-route, where the design is physically mapped onto the FPGA’s resources. Each of these stages is critical and requires specialized tools and expertise.

Verification is particularly important, as bugs in hardware are far more costly and time-consuming to fix than bugs in software. A significant portion of the development timeline is dedicated to creating comprehensive test benches that can simulate a wide range of market conditions and ensure the hardware will behave as expected under pressure.

The Implementation Playbook a Phased Approach

A successful transition to hardware acceleration is typically managed as a phased rollout. This approach allows the firm to build expertise, manage risk, and demonstrate value at each stage of the process. A typical implementation playbook might look like this:

- Phase 1 Assessment and Pilot Project ▴ This initial phase focuses on identifying a single, well-defined function for acceleration. The goal is to choose a project with a high probability of success that can serve as a proof-of-concept. A common starting point is the acceleration of market data feed handling. The firm would build or buy a solution to offload the processing of a single market data feed from the CPU to an FPGA. This project allows the team to gain experience with the hardware development toolchain and demonstrate the latency benefits of the technology.

- Phase 2 Expansion and Integration ▴ Building on the success of the pilot, this phase involves accelerating additional functions and integrating them into a cohesive system. For example, the firm might add an FPGA-based order book and integrate it with the accelerated feed handler. This stage requires the development of a low-latency communication fabric to pass data between different hardware components and the software application. The focus is on building a scalable architecture that can support multiple accelerated functions.

- Phase 3 Strategic Offloading ▴ In this phase, the firm begins to offload its most critical and proprietary trading logic to the hardware. This is the most complex and challenging stage, requiring a deep collaboration between quantitative analysts and hardware engineers. The goal is to create a closed-loop system where the entire trading cycle ▴ from market data in to order out ▴ can occur within the FPGA, with the CPU acting only as a supervisor.

- Phase 4 Optimization and Evolution ▴ The final phase is a continuous process of optimization. The team will work to further reduce latency, add new features to the hardware, and adapt the system to changing market conditions. This may involve migrating the design to newer, faster FPGAs or even designing a custom Application-Specific Integrated Circuit (ASIC) for maximum performance.

What Are the New Talent Profiles Required?

The execution of a hardware strategy hinges on acquiring and cultivating a new set of talent profiles. These roles are distinct from traditional software development and quantitative finance positions and are essential for bridging the gap between trading ideas and silicon implementation. The firm must build a team with a diverse set of skills that spans the entire hardware development lifecycle.

The following table outlines the key roles, their responsibilities, and the specialized skills required:

| Role | Primary Responsibilities | Essential Skills |

|---|---|---|

| FPGA Design Engineer | Translating algorithms into hardware description languages (HDL); designing and implementing logic on FPGAs. | Verilog/VHDL, RTL design, logic synthesis, timing closure, high-speed digital design. |

| Verification Engineer | Creating test benches and simulation environments to validate the correctness of hardware designs. | SystemVerilog, UVM/OVM methodologies, formal verification, scripting (Python/Perl). |

| Systems Architect | Designing the overall hardware/software system; defining interfaces and data flows. | Low-latency architecture, network protocols, PCIe, operating system internals. |

| Quantitative Hardware Developer | A hybrid role that bridges quant finance and hardware engineering; prototypes and implements trading logic in hardware. | Strong quantitative skills, C++, Python, and HDL proficiency. |

| Hardware Test Engineer | Bringing up and testing physical hardware in a lab environment; debugging issues at the physical layer. | Experience with lab equipment (oscilloscopes, logic analyzers), JTAG, board-level debug. |

Building this team requires a multi-pronged approach. The firm must recruit from a global talent pool, establish relationships with top engineering universities, and be prepared to offer competitive compensation packages. Just as importantly, it must create an internal culture that supports the long and rigorous development cycles of hardware engineering and fosters collaboration between these new roles and the firm’s existing software and quant teams.

References

- Selby Jennings. “Hardware Acceleration in Trading ▴ Introduction and Hiring Outlook.” Selby Jennings, Accessed August 5, 2025.

- AInvest. “The AI and Tariff-Driven Reshuffling of Tech Workforces ▴ Strategic Reallocation and Its Impact on Valuations and ESG Investing.” AInvest, 31 July 2025.

- McKinsey & Company. “McKinsey technology trends outlook 2025.” McKinsey & Company, 22 July 2025.

- Kim, J. & Lee, S. “The Impact of Technological Capability on Financial Performance in the Semiconductor Industry.” MDPI, 2021.

- McKinsey & Company. “Superagency in the workplace ▴ Empowering people to unlock AI’s full potential.” McKinsey & Company, 28 January 2025.

Reflection

The journey into hardware acceleration is a commitment to mastering the physical constraints of the market. It compels a firm to look beyond the elegance of its algorithms and confront the uncompromising realities of latency and time. The knowledge gained in this process ▴ the deep understanding of data pathways, clock cycles, and gate-level logic ▴ becomes a new form of intellectual property. It is an architectural intelligence that is difficult to replicate and serves as a powerful, long-term differentiator.

As you consider your own operational framework, the central question emerges ▴ is your firm’s strategy defined solely by its software, or is it being shaped by a deeper understanding of the hardware on which it runs? The answer will determine the ultimate ceiling of your performance in an increasingly competitive landscape. The path forward is one of co-design, where technology and talent are woven together to create a system that is not just fast, but deterministic, predictable, and purpose-built for the unique demands of modern markets.

Glossary

Hardware Acceleration

Physical Reality

Operating System

Market Data

Fpga

Development Lifecycle

Specialized Hardware

High-Frequency Trading

Logic Gates

Software Systems

Order Book

Strategy Becomes

Competitive Advantage

Electrical Engineering

Deterministic Execution

Talent Strategy

Technology Roadmap

Hardware Engineers

Hardware Engineering

Hardware Design

Hardware Acceleration Strategy

Verilog

Hardware Development

Market Data Feed

Hardware Development Lifecycle