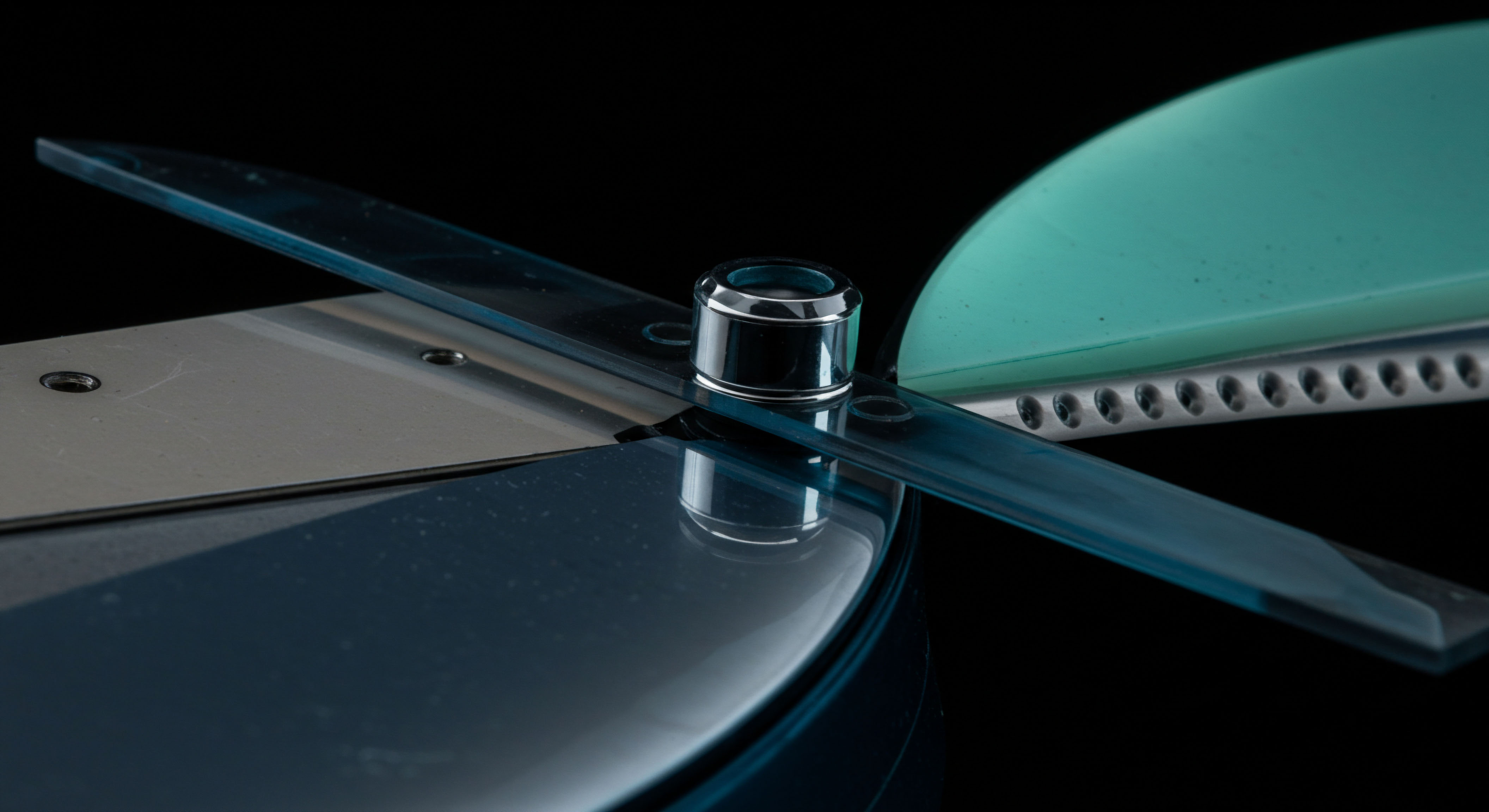

Concept

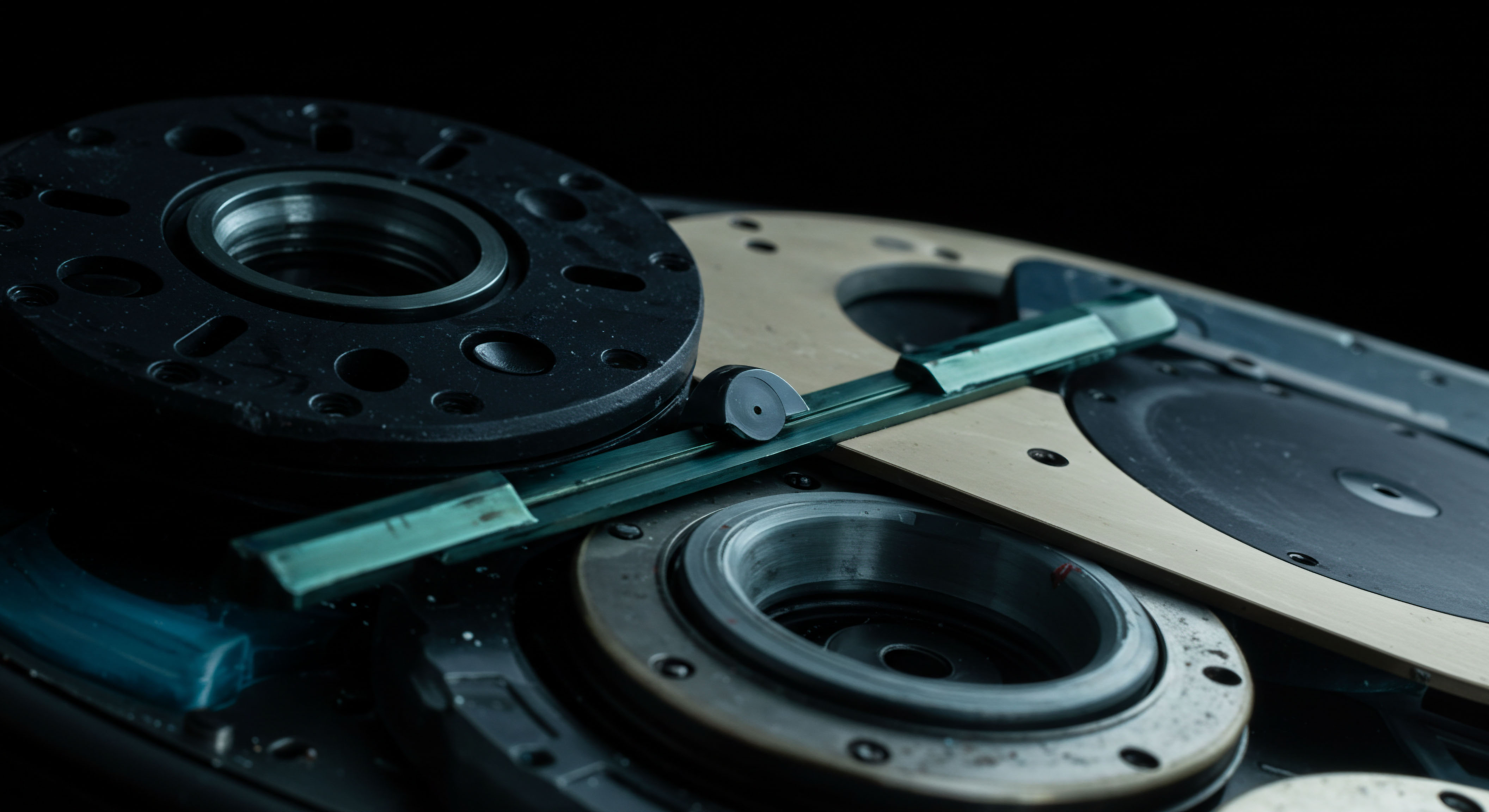

The Financial Information eXchange (FIX) protocol exists as the systemic bedrock of modern electronic trading, a testament to the market’s need for a universal communication standard. Its ubiquity, however, presents a central paradox for any institution focused on execution velocity. The very protocol designed to streamline and standardize communication across a fragmented global landscape is also a source of inherent latency.

Understanding this duality requires viewing the protocol not as a monolithic flaw, but as a specific component within a complex trading architecture, a component with a defined performance envelope and a series of deliberate engineering trade-offs. The latency contribution of FIX is a direct consequence of its design philosophy, one that prioritized human-readability and universal applicability in its initial stages over the raw, microsecond-level performance demanded by today’s automated execution venues.

At its core, the FIX protocol is a session-based, application-level messaging standard that governs the real-time exchange of securities transaction information. It operates over the Transmission Control Protocol (TCP), ensuring reliable, in-sequence delivery of messages. The trading lifecycle, which FIX was built to serve, can be broadly segmented into three phases ▴ pre-trade, trade, and post-trade. In the pre-trade phase, FIX messages handle indications of interest (IOIs) and quotes.

During the trade phase, the protocol is the vehicle for orders, modifications, and execution reports. The post-trade phase utilizes FIX for allocation instructions and settlement details. The latency introduced by the protocol itself manifests across every one of these stages, accumulating at each processing node in the chain from client to broker to exchange and back.

The text-based nature of classic FIX messages is a primary source of computational overhead, requiring significant processing time for parsing and validation.

The primary sources of this latency are baked into the protocol’s fundamental structure. The classic FIX message format is a human-readable, text-based string composed of tag=value pairs separated by a delimiter. While this design offers clarity for developers and compliance officers, it is profoundly inefficient for machine processing. Each message received by a FIX engine must be parsed, a process that involves scanning the string, identifying tags and their corresponding values, and converting these text representations into the native binary data types that a trading application can actually use, such as integers for quantity or doubles for price.

This serialization and deserialization process is computationally expensive and represents a significant and unavoidable latency chokepoint in the trading lifecycle. Furthermore, the protocol mandates validation of message fields for correctness, adding another layer of processing delay before the core business logic of the order can even be addressed.

Another significant latency contributor is the protocol’s session management layer. FIX was designed for reliability, featuring robust mechanisms to ensure no message is lost and that data integrity is maintained. These mechanisms include sequence numbers for every message, regular heartbeat messages to verify connection status, and the ability to request the retransmission of missed messages. While essential for ensuring the orderly and guaranteed exchange of financial information, these features create a constant stream of administrative overhead.

The logic required to manage sequence numbers, process heartbeats, and handle potential resend requests consumes CPU cycles and adds incremental delays to every transaction, a cost that becomes substantial in high-frequency environments where thousands of messages may be processed per second. The protocol’s reliance on TCP also introduces its own latency profile related to network acknowledgments and congestion control, which, while not a flaw of FIX itself, is an integral part of its standard implementation.

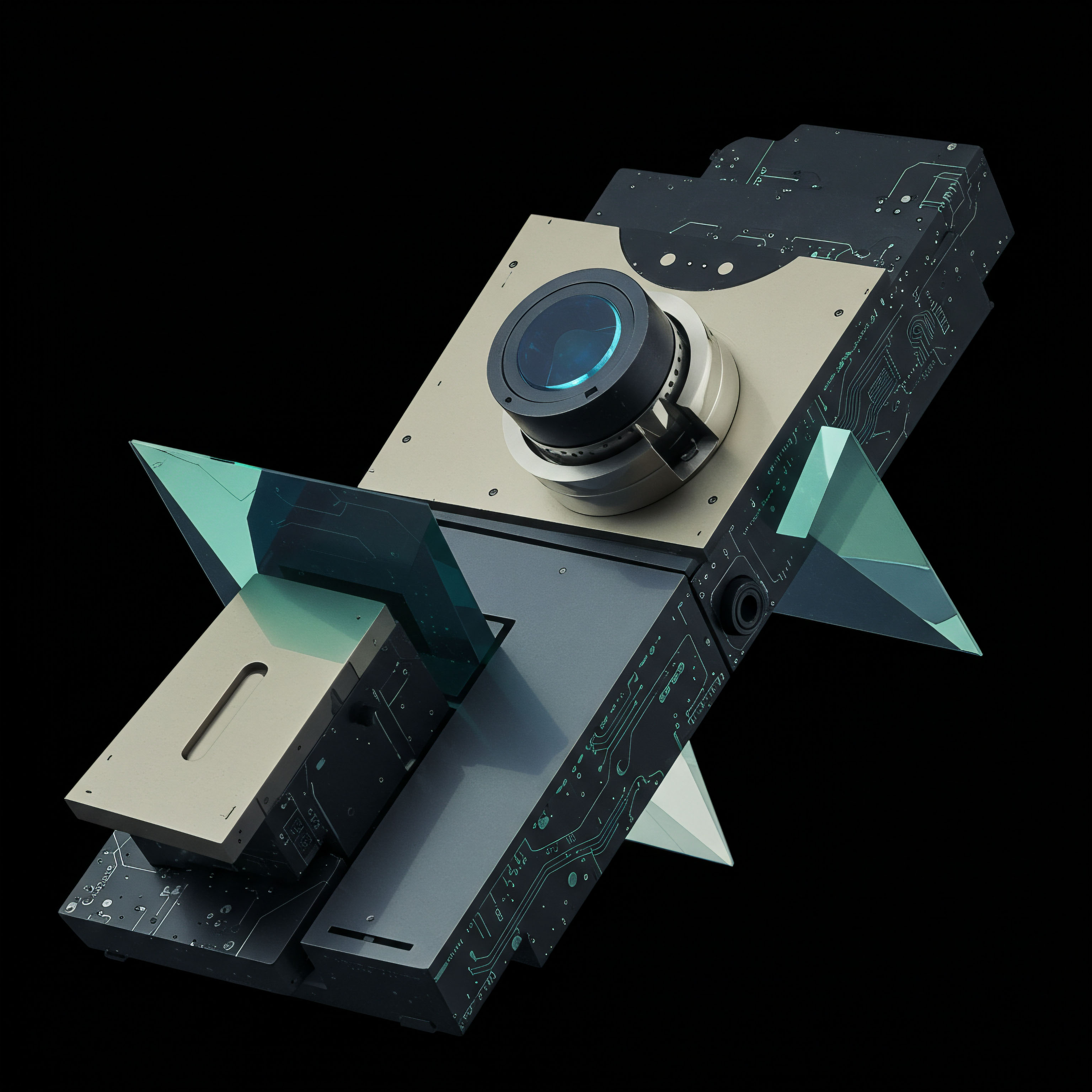

Strategy

The strategic decision to employ the FIX protocol is a calculated trade-off between interoperability and raw speed. For market participants, the protocol’s primary advantage is its universality. It provides a standardized language that eliminates the need to develop and maintain dozens of bespoke, proprietary interfaces to connect with different brokers, exchanges, and clients. This drastically reduces integration costs, development time, and operational complexity.

From a systems architecture perspective, this represents a strategic choice to accept a known latency cost in exchange for immense gains in connectivity and market access. The critical strategic challenge, therefore, becomes managing and mitigating that inherent latency within the standardized framework that FIX provides.

How Do Firms Mitigate Protocol-Induced Latency?

An effective strategy for mitigating FIX-related latency involves a multi-layered approach that addresses the protocol’s core inefficiencies. This begins with the evolution of the protocol itself. Recognizing the performance limitations of the classic tag=value syntax, the FIX Trading Community developed more efficient encodings. These are not replacements for FIX but rather alternative on-the-wire formats that retain the semantic meaning of the FIX dictionary while optimizing for machine processing.

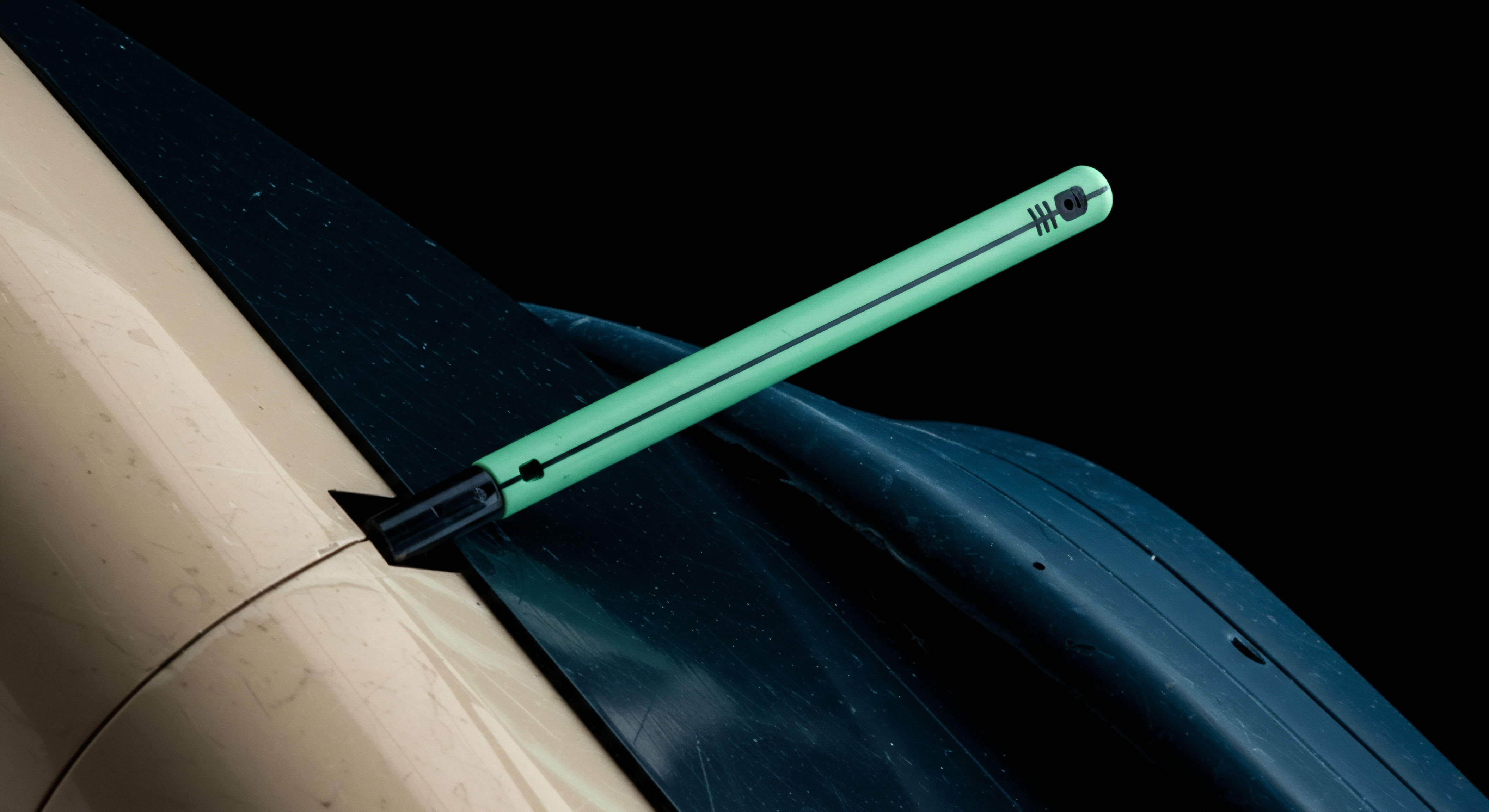

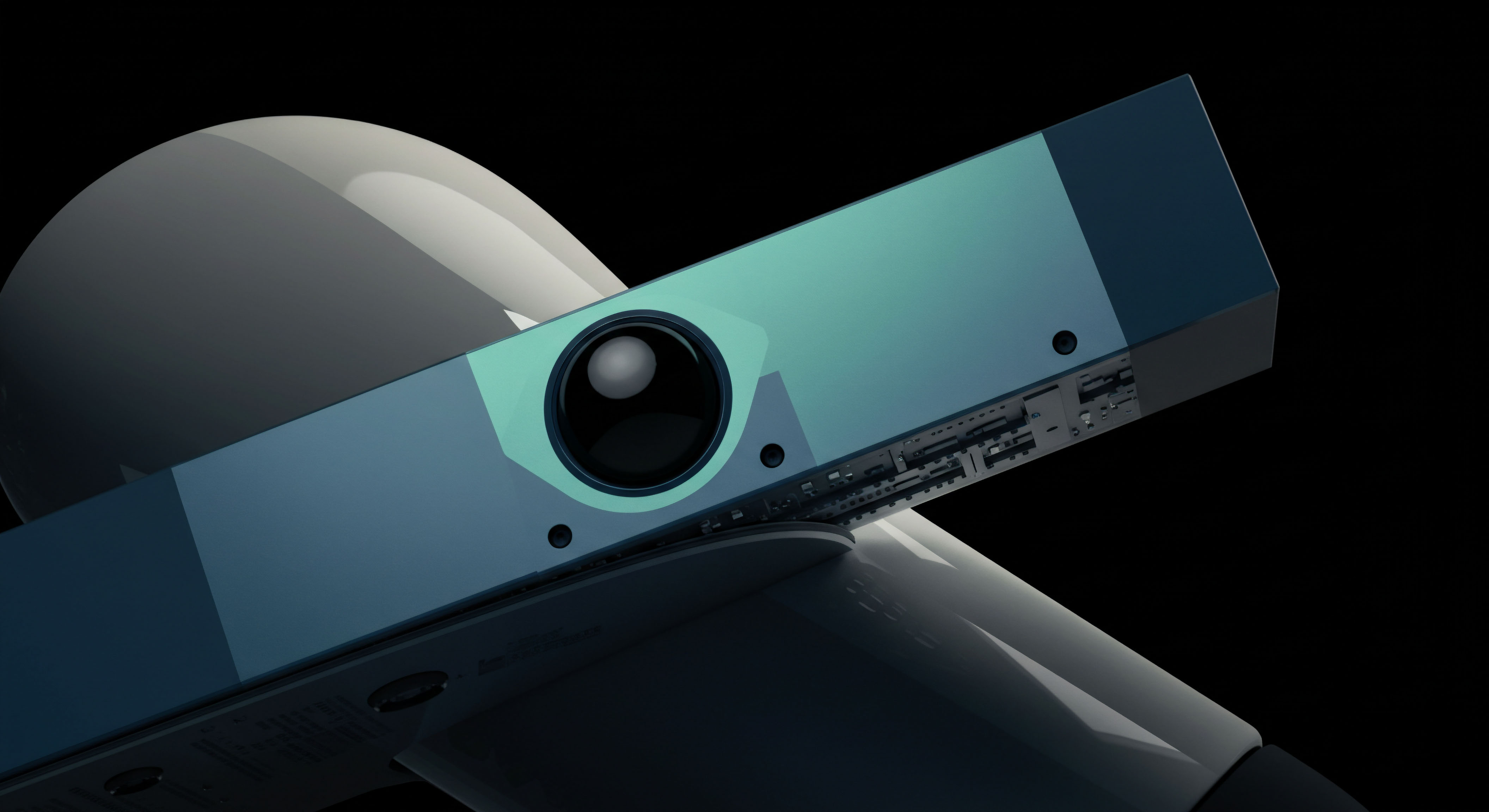

- FIX Adapted for STreaming (FAST) ▴ This standard was developed specifically to optimize the transmission of high-volume market data. FAST reduces message size and processing overhead through two key techniques ▴ field encoding and presence map templates. It uses binary representations for numeric data, which is far more compact and faster to process than text-based numbers. Furthermore, it employs templates that define the structure of a message, allowing for the omission of redundant tags and sending only the data that has changed from the previous message, a concept known as delta streaming.

- Simple Binary Encoding (SBE) ▴ SBE represents a further evolution aimed at achieving the lowest possible latency for encoding and decoding messages. It is a message-oriented binary encoding that uses fixed positions and native binary data types. This design allows an application to access data fields directly in memory without complex parsing or transformation logic. The focus is on “direct data access,” which makes SBE particularly suitable for the most latency-sensitive parts of the trading lifecycle, such as order entry and market data consumption in high-frequency trading (HFT).

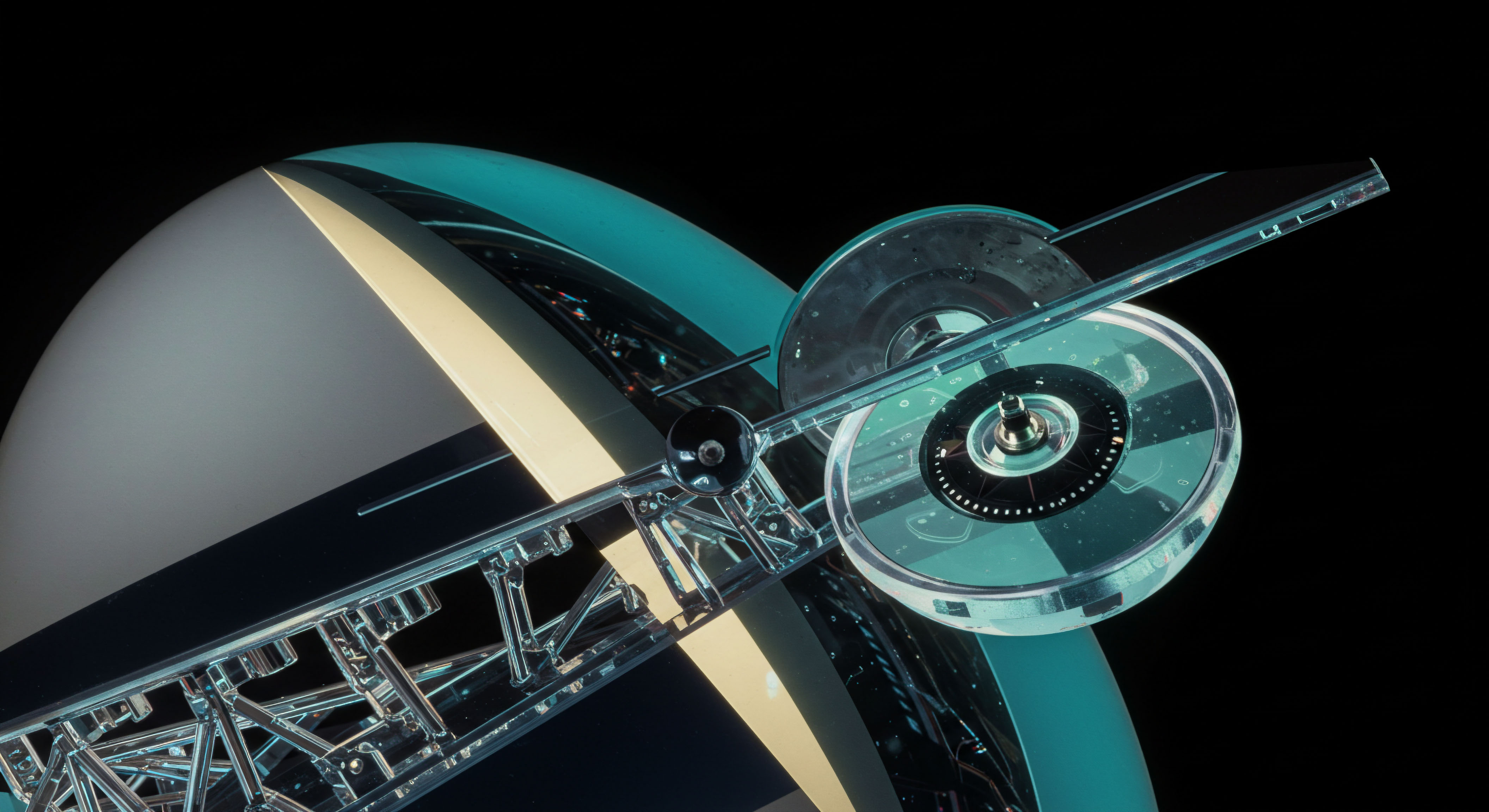

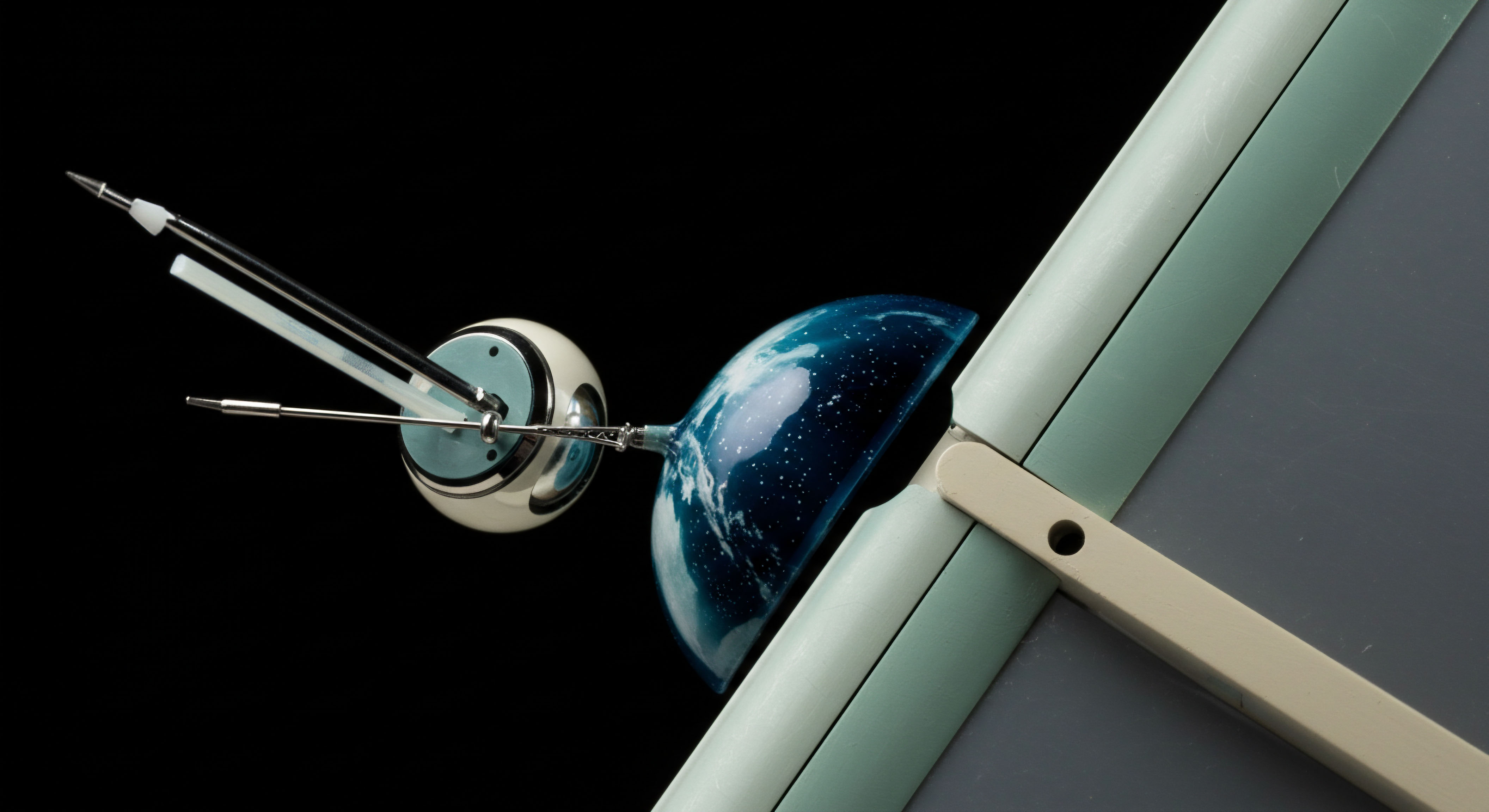

The Hybrid Protocol Architecture

A sophisticated strategy employed by many firms is a hybrid protocol architecture. This approach recognizes that not all parts of the trading lifecycle have the same latency sensitivity. A firm might use a highly optimized, low-latency protocol like SBE or a direct proprietary binary interface for its connection to an exchange’s matching engine, where every microsecond counts. Simultaneously, the same firm will use the classic tag=value FIX protocol for its client-facing connections.

This allows clients to connect using the industry standard they are familiar with, while the firm’s internal systems translate these messages into a high-performance format for execution. The same classic FIX protocol is then used again for post-trade clearing and allocation messages, where reliability and standardization are more important than sub-microsecond speed. This tiered approach isolates the latency-critical path while retaining the broad compatibility of standard FIX for less time-sensitive functions.

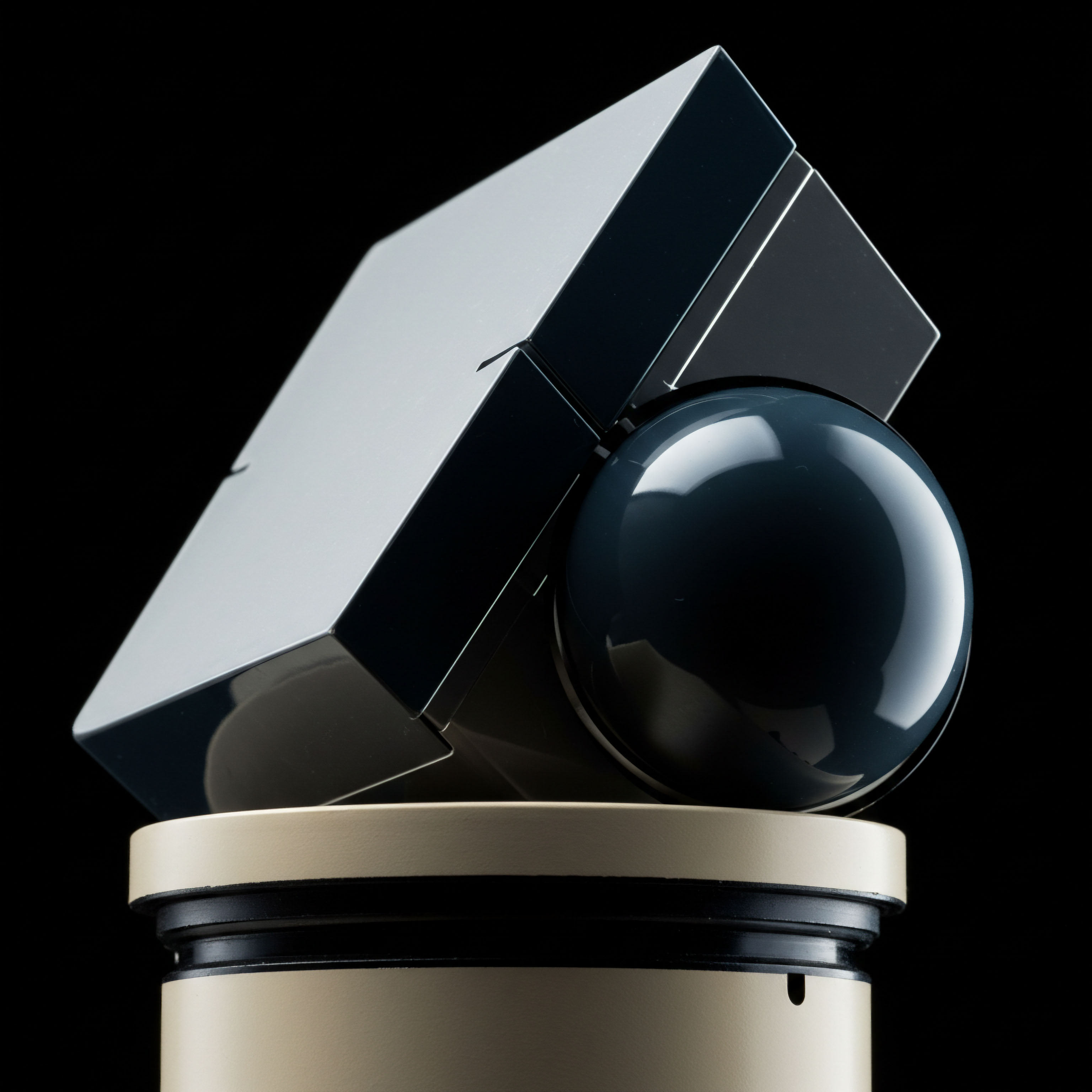

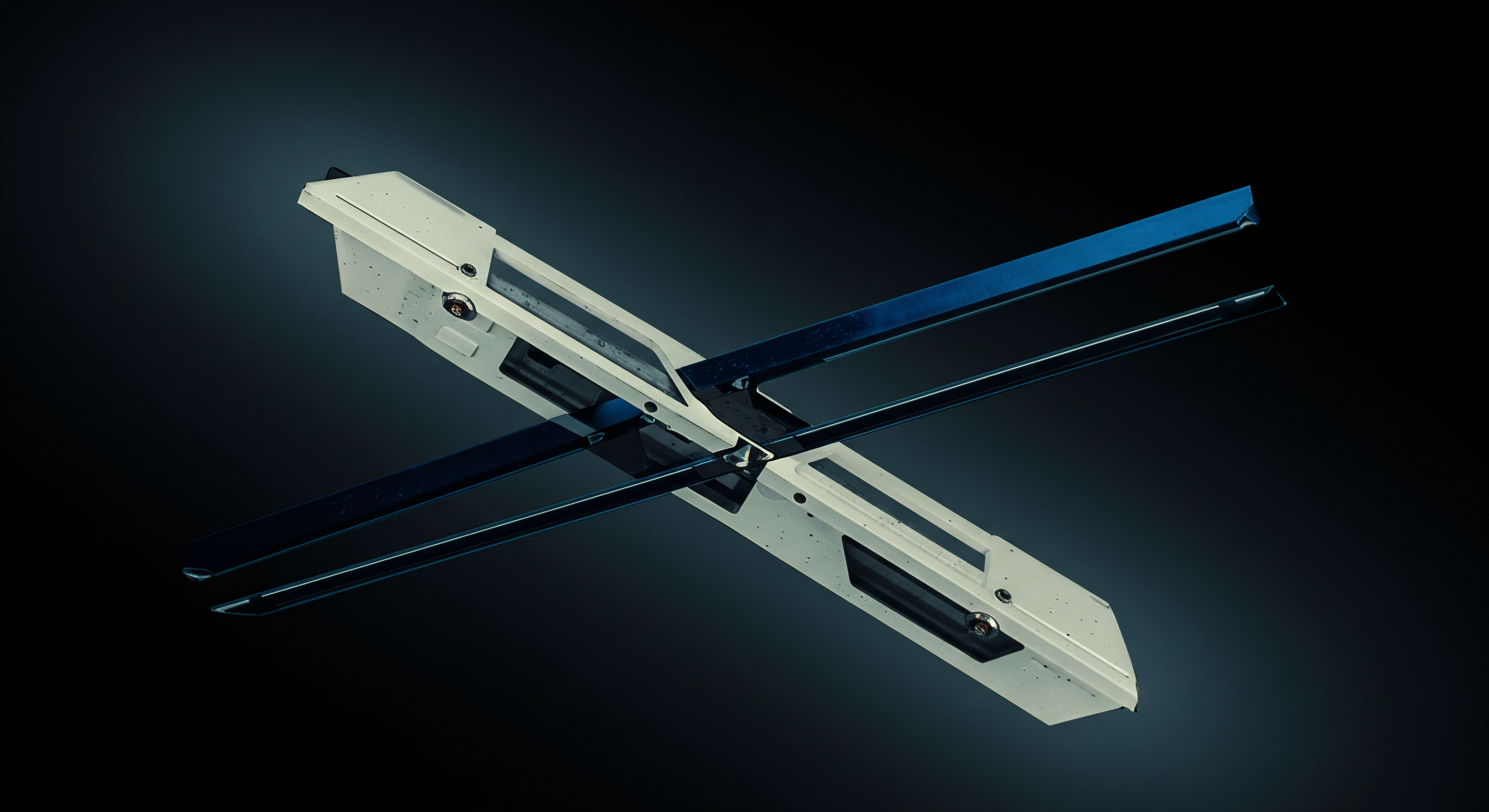

Optimizing the FIX engine, the software that processes protocol messages, is as critical as the choice of on-the-wire format for managing latency.

The performance of the FIX engine itself is a central pillar of any latency mitigation strategy. A FIX engine is the software component responsible for parsing, validating, and managing FIX sessions. High-performance engines are typically written in low-level languages like C++ to allow for fine-grained memory management and avoid the unpredictable pauses associated with garbage collection in languages like Java. Strategic choices in FIX engine design and configuration include:

- Parser Optimization ▴ Utilizing highly efficient algorithms to minimize the time taken to read the tag=value stream and convert it to usable data.

- Zero-Copy Operations ▴ Designing the engine to pass message data between network buffers and the application without intermediate copying, which saves CPU cycles.

- Off-Heap Memory Storage ▴ In Java-based systems, storing message objects off the main garbage-collected heap to prevent performance stutters during collection cycles.

- Kernel and Network Stack Tuning ▴ Configuring the underlying operating system and network drivers to prioritize low-latency data transfer, often through techniques like kernel bypass.

The following table provides a strategic comparison of the different FIX protocol variants, highlighting the trade-offs inherent in each choice.

| Protocol Variant | On-the-Wire Format | Primary Latency Source | Optimal Use Case | Strategic Advantage |

|---|---|---|---|---|

| Classic FIX (Tag=Value) | ASCII Text | String Parsing & Validation | Client Connectivity, Post-Trade | Universal Compatibility, Simplicity |

| FIX over FAST | Template-based Binary | Template Management | Market Data Streaming | Bandwidth Reduction, Lower Overhead |

| Simple Binary Encoding (SBE) | Positional Binary | Minimal (Direct Memory Access) | Ultra-Low Latency Execution | Lowest Possible Encoding/Decoding Time |

Execution

Executing a strategy to minimize FIX-related latency requires a granular understanding of where every microsecond is spent. This moves beyond high-level concepts into the precise mechanics of message processing and system architecture. From a systems architect’s perspective, the trading lifecycle is a sequence of latency-adding events, and optimizing execution is a process of systematically identifying and compressing each of these events.

The Operational Playbook for Latency Analysis

A foundational step in execution is to create a detailed map of the message lifecycle. This operational playbook outlines every processing stage a FIX message transits from inception to finality. By instrumenting each stage with high-resolution timestamps, an institution can build a precise latency profile of its trading workflow.

- T0 – Order Creation ▴ An order is generated within the client’s Order Management System (OMS) or by an algorithmic trading strategy. The data exists as a native object in the application’s memory.

- T1 – FIX Serialization ▴ The application’s FIX engine takes the native order object and serializes it into a classic tag=value string. The time difference (T1 – T0) is the serialization latency.

- T2 – Network Transmission (Client to Broker) ▴ The message is handed to the operating system’s network stack and transmitted over the physical network. Latency here is a function of network card performance, driver efficiency, and physical distance.

- T3 – Broker FIX Engine Ingress ▴ The broker’s FIX engine receives the first byte of the message from its network card. The time difference (T3 – T2) is the network transit time.

- T4 – FIX Deserialization and Validation ▴ The broker’s engine parses the tag=value string, validates the fields, and converts it back into a native object. The time difference (T4 – T3) is the core FIX processing latency on the broker side. This is often the largest single contributor.

- T5 – Business Logic and Routing ▴ The broker’s system performs risk checks, locates liquidity, and prepares to route the order to an exchange.

- T6 – Exchange Protocol Serialization ▴ The order is serialized into the exchange’s native protocol (often SBE or another binary format).

- T7 – Exchange Ingress and Acknowledgment ▴ The exchange receives the order and sends back an acknowledgment. The entire process then runs in reverse for the execution report, adding more latency at each step.

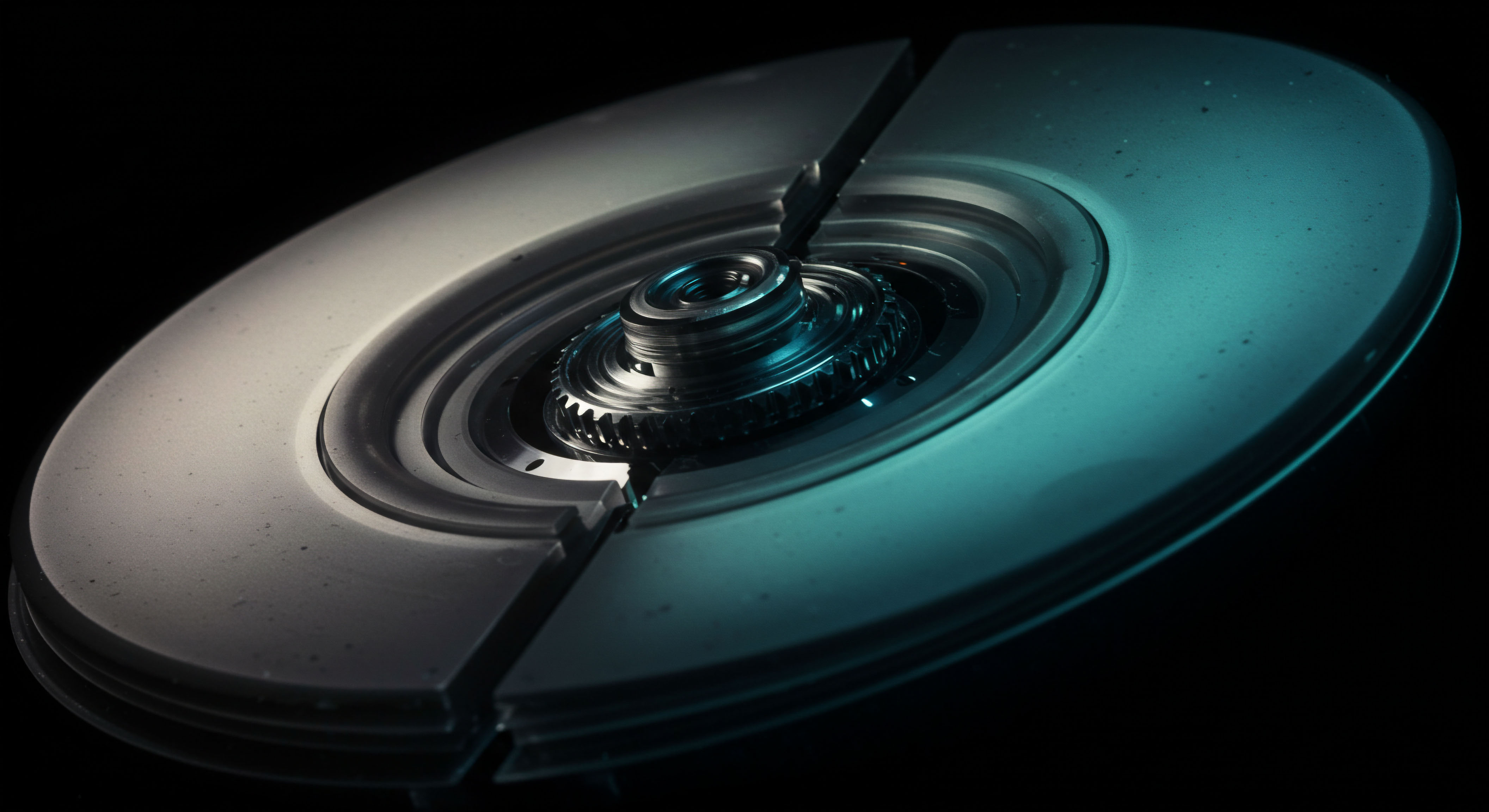

Quantitative Modeling of FIX Latency Contribution

To translate this procedural map into an actionable quantitative model, firms must measure these timestamps with microsecond precision. The resulting data allows for the construction of a detailed latency breakdown table, which becomes the primary tool for identifying optimization targets. The table below presents a hypothetical but realistic model of this breakdown for a standard equity order.

| Workflow Event (Timestamp) | Latency (µs) | Cumulative Latency (µs) | Primary Contributor |

|---|---|---|---|

| T1 ▴ FIX Serialization (Client) | 5.2 | 5.2 | CPU / Engine Efficiency |

| T3 ▴ Network Transit (Co-located) | 2.5 | 7.7 | Fiber Distance / Switch Hops |

| T4 ▴ FIX Deserialization (Broker) | 15.8 | 23.5 | Protocol Verbosity / Parser Inefficiency |

| T5 ▴ Broker Business Logic | 3.1 | 26.6 | Risk Checks / Routing Rules |

| T6 ▴ SBE Serialization (Broker) | 0.9 | 27.5 | Binary Encoding Efficiency |

| T7 ▴ Network Transit (To Exchange) | 1.5 | 29.0 | Direct Fiber Cross-Connect |

This quantitative model demonstrates that in a co-located environment where network delay is minimal, the FIX deserialization step (T4) is the single largest source of latency, nearly three times greater than the initial serialization (T1) and more than five times the internal business logic processing time. This is because deserialization is a more complex operation, involving not just parsing but also data type conversion and validation against the FIX dictionary. The model also starkly illustrates the performance difference between classic FIX and a binary protocol like SBE, where the serialization time (T6) is almost negligible.

The execution of a low-latency strategy hinges on a relentless, data-driven effort to compress every stage of the message lifecycle.

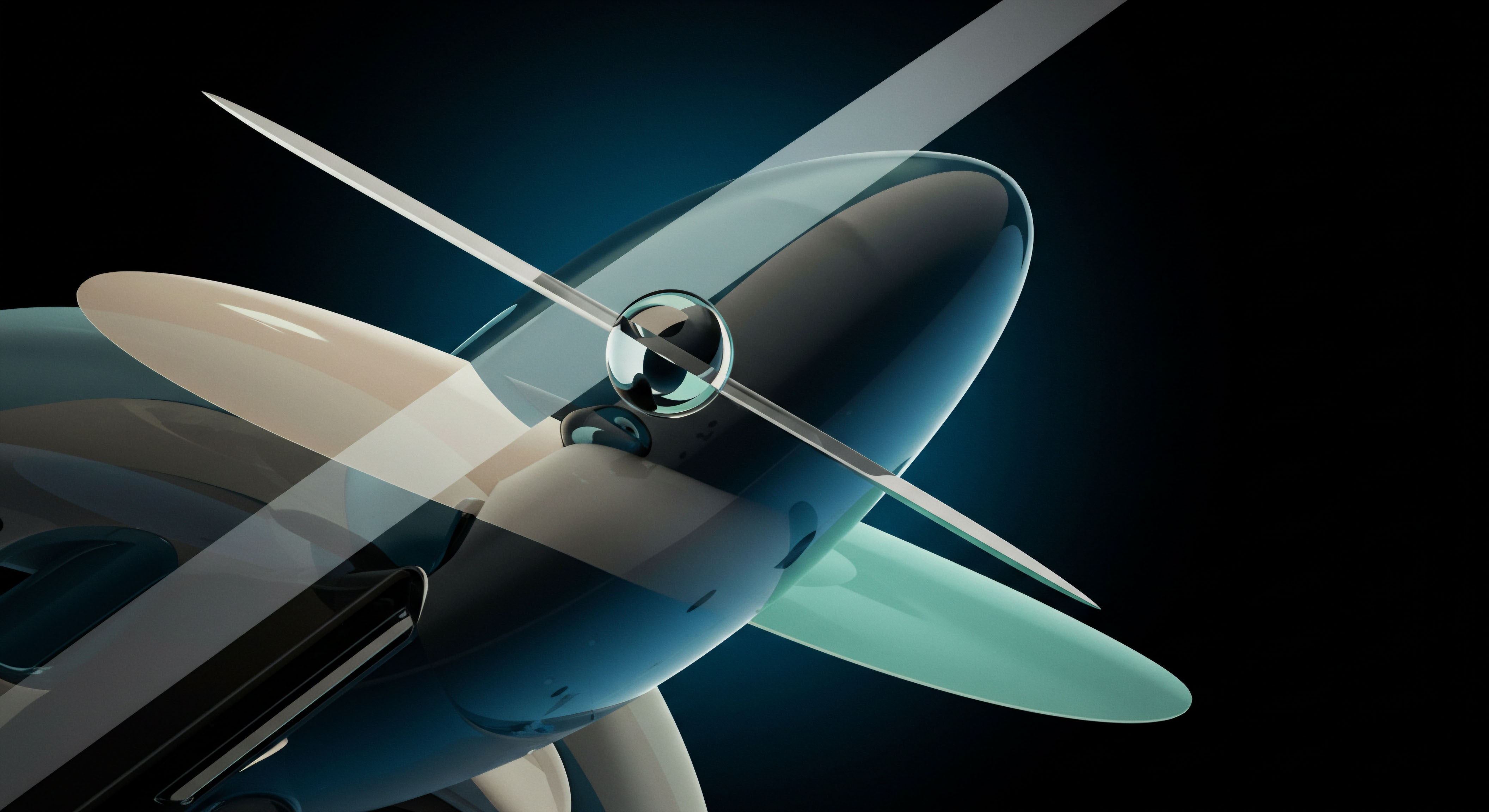

System Integration and Technological Architecture

The final layer of execution involves tuning the underlying technology stack. This is where hardware, software, and protocol choices converge.

- Hardware Architecture ▴

- Colocation ▴ Placing trading servers in the same data center as the exchange’s matching engine is the most effective way to reduce network latency. This reduces transmission delay from milliseconds to microseconds.

- High-Performance NICs ▴ Network Interface Cards with features like kernel bypass allow applications to communicate directly with the network hardware, avoiding the latency of the operating system’s network stack.

- CPU Pinning ▴ Assigning specific processes (like the FIX engine’s I/O threads) to specific CPU cores to prevent context switching and ensure consistent performance.

- Software and FIX Engine Architecture ▴

- Engine Selection ▴ Choosing a FIX engine implemented in a low-level language (e.g. C++) with a proven low-latency track record.

- Memory Management ▴ Employing techniques like memory pooling and avoiding dynamic memory allocation during critical path processing to prevent unpredictable delays.

- Concurrency Models ▴ Using non-blocking, event-driven architectures to handle thousands of simultaneous connections efficiently without the overhead of managing a large number of threads.

References

- FIXSOL. “Latency Optimization in Trading.” FIXSOL, 2023.

- Andersson, Rolf. “Low Latency Market Data ▴ Are Proprietary Protocols Needed?” Global Trading, 15 June 2010.

- FIXSIM. “7 Key Benefits of FIX Protocol | The Advantages for Financial Communication.” FIXSIM, 2 April 2024.

- Das, Dhanjit. “FIX Trading Protocol ▴ Benefits and Recent Developments.” QuantInsti Blog, 8 February 2016.

- BJF Trading Group. “How FIX protocol works ▴ Forex & Cryptocurrencies Arbitrage Software.” BJF Trading Group, 7 March 2022.

Reflection

The analysis of FIX protocol latency moves an institution’s focus from a simple question of speed to a more profound consideration of architectural intent. The data reveals that latency is not a uniform penalty but a series of specific, measurable costs introduced at discrete points in the trading workflow. Viewing the protocol through this lens transforms the challenge. It becomes an exercise in systemic design ▴ structuring a trading infrastructure that intelligently deploys the universal standard of FIX where its connectivity benefits are paramount, while surgically applying higher-performance binary protocols where every microsecond confers a competitive advantage.

The ultimate objective is the creation of a coherent, multi-protocol architecture where each component is selected not in isolation, but for its optimal function within the entire execution system. How does your current operational framework measure and balance this fundamental trade-off between universal access and execution velocity?

Glossary

Latency

Trading Lifecycle

Fix Protocol

Fix Engine

Tag=value

Deserialization

Business Logic

Session Management

Systems Architecture

Market Data

High-Frequency Trading

Simple Binary Encoding

Where Every Microsecond