Concept

The decision to architect a trading system around a Central Processing Unit (CPU) versus a Field-Programmable Gate Array (FPGA) is a foundational choice that dictates the entire operational reality of a trading desk. It defines not just the latency profile of an execution strategy, but the very DNA of the development workflow, the skill sets required of the engineering team, and the cadence at which the firm can adapt to market structure evolution. Viewing this as a simple choice between “software” and “hardware” is a profound mischaracterization. The reality is a choice between two distinct philosophies of computation and control, each with its own deeply embedded workflow, risk profile, and strategic implications.

A CPU-based system operates on a principle of sequential execution, guided by a stored program. The development workflow is an iterative process of writing, compiling, and executing software code in high-level languages like C++. This paradigm offers immense flexibility and a rapid development cycle for complex, branching logic. The system architect thinks in terms of algorithms, data structures, and process management.

The workflow is fluid, enabling rapid prototyping and deployment of new strategies. The core competency lies in software engineering excellence, algorithmic complexity, and the ability to manage the layers of abstraction inherent in modern operating systems.

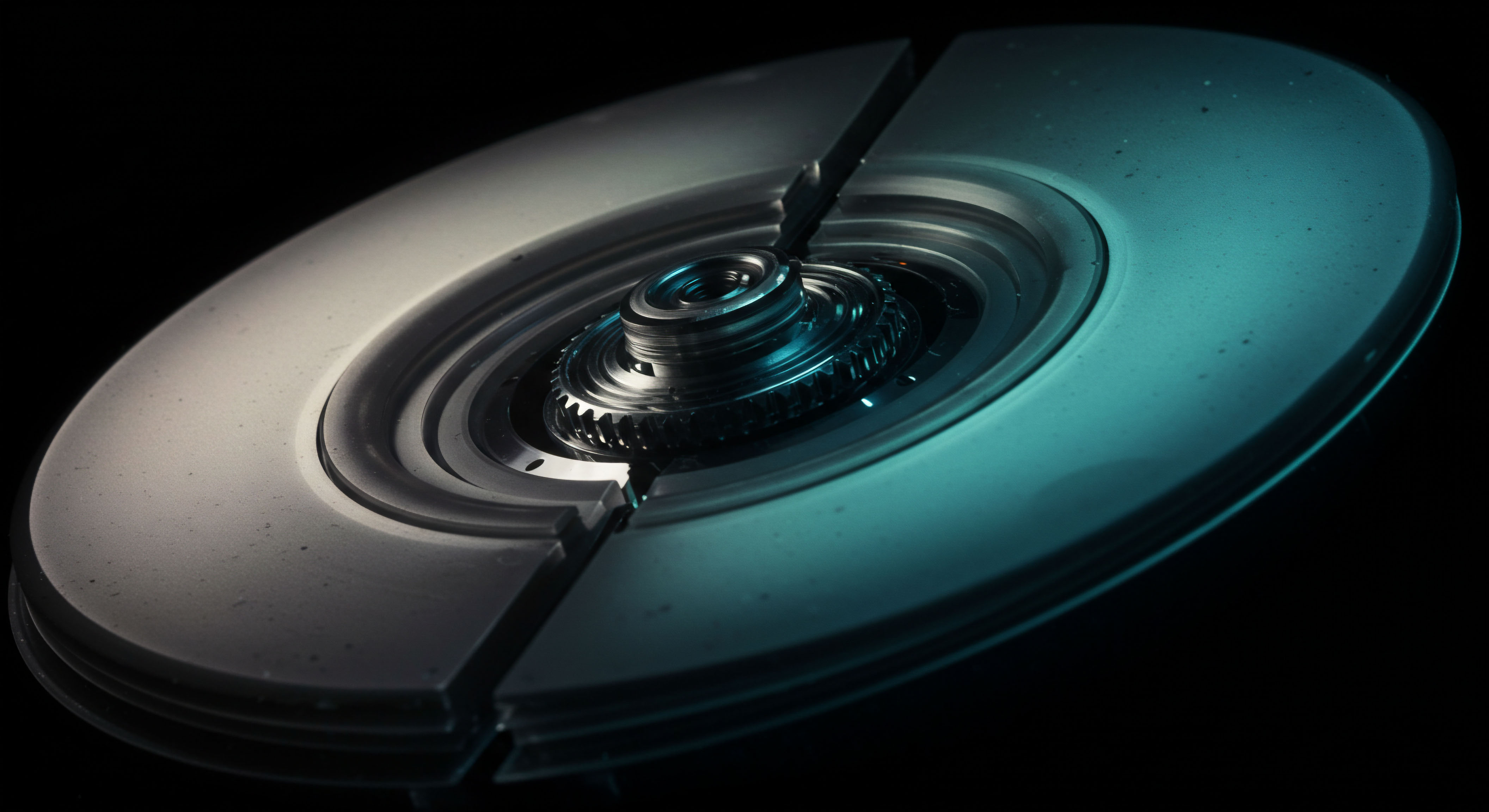

The core distinction lies in whether logic is executed sequentially as a set of instructions on a general-purpose processor or implemented directly as a physical circuit.

Conversely, an FPGA-based system embodies the principle of spatial or parallel computation. The development workflow is a process of designing a digital circuit. Instead of writing instructions to be executed, engineers describe the hardware logic itself using a Hardware Description Language (HDL) like Verilog or VHDL. This description is then synthesized into a configuration file, or bitstream, that physically arranges the logic gates on the FPGA chip to perform a specific task.

The workflow is more rigid and deterministic, mirroring the design cycle of a physical integrated circuit. The system architect thinks in terms of data paths, clock cycles, and gate-level parallelism. The focus shifts from algorithmic elegance to hardware efficiency and the physics of signal propagation. The result is a system where the trading logic is not just a program; it is the circuit itself, offering deterministic, ultra-low latency performance for specific, repetitive tasks. This path demands a deep expertise in digital engineering and a workflow that prioritizes meticulous verification and validation before deployment, as errors are far more costly to rectify than in a software-centric environment.

The divergence in these workflows is absolute. The CPU path is one of abstraction and rapid iteration, managed by software engineers. The FPGA path is one of physical implementation and deterministic performance, managed by hardware engineers.

The strategic choice between them hinges on the firm’s core trading philosophy ▴ is the primary competitive vector the sophistication and adaptability of its complex models, or the raw speed and determinism of its execution path? Understanding this distinction is the first principle in architecting a trading system that aligns with a firm’s fundamental source of market edge.

Strategy

Strategically approaching the development of a trading system requires a clear-eyed assessment of the trade-offs between the CPU and FPGA paradigms. The selection is a commitment to a specific operational posture, influencing everything from talent acquisition to the types of market opportunities a firm can realistically pursue. The strategic framework for this decision rests on three pillars ▴ Latency Profile, Development Velocity, and Operational Risk.

Latency Profile and Determinism

The most cited reason for adopting FPGAs is the pursuit of ultra-low latency. A CPU-based system, for all its power, operates with inherent non-determinism. The execution time of a piece of code can be affected by operating system interrupts, cache misses, context switching, and other processes competing for resources.

For most applications, these microsecond-level variations are inconsequential. In high-frequency trading, they represent a critical loss of control.

An FPGA, by contrast, offers deterministic latency. Because the trading logic is implemented as a physical circuit, the time it takes for a signal to travel from an input pin (e.g. receiving a market data packet) to an output pin (e.g. sending an order) is fixed and predictable, measured in nanoseconds. This provides a powerful strategic advantage in latency-sensitive strategies like statistical arbitrage or market making, where being first in the queue is paramount.

The strategic choice between CPU and FPGA development workflows is fundamentally a choice between maximizing adaptability and maximizing deterministic speed.

The strategic implication is clear ▴ firms whose strategies depend on being at the absolute top of the order book for simple, repetitive tasks (like market data parsing and order entry) derive immense value from the FPGA’s deterministic nature. Firms whose strategies involve more complex, multi-faceted decision-making that can tolerate a few microseconds of jitter find the CPU’s flexibility more strategically valuable.

Development Velocity and Adaptability

The second strategic pillar is the speed at which a firm can develop, test, and deploy new trading logic. This is where the CPU-based workflow holds a distinct advantage. The software development lifecycle is mature and highly optimized for rapid iteration.

- CPU Workflow ▴ A quantitative analyst can prototype a new model in a language like Python, and a C++ developer can translate it into a production-ready application within days or weeks. Deployment can be as simple as pushing a new executable to a server. This agility allows firms to quickly respond to changing market conditions or to experiment with new alpha signals.

- FPGA Workflow ▴ The hardware development lifecycle is inherently more deliberate and time-consuming. Writing HDL code is a specialized skill. The synthesis, place-and-route, and bitstream generation process can take hours or even days for a complex design. Verification is a far more intensive process, as a bug in the hardware can have catastrophic consequences and is much harder to patch. A seemingly small change to the logic can require a full re-verification cycle.

High-Level Synthesis (HLS) tools are emerging to bridge this gap, allowing developers to write in C-like languages and automatically generate HDL. While HLS accelerates the initial coding phase, it does not eliminate the need for rigorous hardware verification. The generated HDL often requires manual optimization to achieve the desired performance, and the developer still needs a fundamental understanding of hardware design principles. The strategic choice here is between the rapid, iterative adaptability of software and the more methodical, deliberate pace of hardware development.

How Does the Operational Risk Profile Differ?

The final strategic consideration is the nature of operational risk in each workflow. The risks associated with CPU-based systems are well understood ▴ software bugs, memory leaks, race conditions, and system crashes. These can be mitigated through robust testing, code reviews, and resilient system architecture.

The risks in an FPGA workflow are different in character. A bug in an FPGA design is not just a software error; it is a flaw in a custom-built processing chip. The potential for subtle timing errors, logic flaws that only manifest under specific data conditions, or incorrect state machine transitions is high. The verification process must be exhaustive, often involving a combination of simulation, formal verification, and hardware-in-the-loop testing.

The Universal Verification Methodology (UVM) has become a standard for this, providing a structured, reusable framework for verifying complex digital designs. A failure in an FPGA can be silent and difficult to detect, potentially leading to significant financial losses before it is identified. The strategic decision must weigh the risk of software-level instability against the risk of hard-to-detect hardware-level flaws.

The table below outlines the strategic trade-offs across these three pillars.

| Strategic Pillar | CPU-Based System | FPGA-Based System |

|---|---|---|

| Latency Profile | Microsecond-level, non-deterministic latency. Subject to OS jitter and resource contention. | Nanosecond-level, deterministic latency. Predictable performance based on circuit path. |

| Development Velocity | High. Rapid prototyping and iterative development cycles. Agile response to market changes. | Low. Deliberate, lengthy design cycles. Synthesis and verification are time-intensive. |

| Adaptability | Very High. New strategies and logic can be deployed quickly. | Low. Changes to logic require a full hardware re-synthesis and verification cycle. |

| Core Competency | Software Engineering, Algorithmic Complexity, System Administration. | Digital Hardware Engineering, HDL, Verification, Timing Closure. |

| Operational Risk | Software bugs, system crashes, resource contention. Mitigated by software testing and resilience. | Hardware bugs, timing violations, synthesis errors. Mitigated by exhaustive simulation and formal verification (e.g. UVM). |

Execution

The execution of a development workflow for CPU and FPGA-based trading systems represents two fundamentally different operational paradigms. The day-to-day tasks, toolchains, and team structures are distinct, reflecting the core difference between manipulating software instructions and designing physical circuits. A granular examination of these workflows reveals the practical implications of the strategic choices discussed previously.

The CPU Development Workflow a Cycle of Iteration

The CPU workflow is characterized by its iterative and software-centric nature. The process is managed by software developers, quantitative analysts, and system engineers. The primary goal is to translate a trading idea into efficient, robust, and maintainable code.

- Strategy Prototyping ▴ The lifecycle often begins with a quantitative analyst or trader developing a model. This is typically done in a high-level, interactive environment like Python or MATLAB, allowing for rapid experimentation with data and statistical models.

- Production Implementation ▴ Once a prototype is validated, it is handed over to a C++ development team for production implementation. This phase focuses on performance, stability, and integration with the firm’s existing trading infrastructure. The code is written to be highly optimized, but it still operates within the confines of the operating system and the CPU architecture.

- Compilation and Linking ▴ The C++ code is compiled into an executable binary. This process is relatively fast, typically taking minutes. The executable is linked against various libraries for market data handling, order management, and risk controls.

- Testing and QA ▴ The compiled application undergoes several layers of testing. Unit tests verify the correctness of individual components. Integration tests ensure the application works correctly with other parts of the trading system. Finally, simulation testing runs the application against historical or live market data in a controlled environment to validate its behavior and performance.

- Deployment ▴ Once testing is complete, the executable is deployed to the production servers. This can often be done dynamically, with minimal downtime. Rollback procedures are typically straightforward, involving the redeployment of a previous version of the executable.

The FPGA Development Workflow a Pipeline to Hardware

The FPGA workflow is a more linear and hardware-focused pipeline. It requires a specialized team of FPGA engineers who are proficient in digital logic design and verification. The goal is to create a physical circuit that executes the trading logic with maximum speed and determinism.

The process is far more structured and less forgiving of error. Each stage builds upon the previous one, and a flaw discovered late in the process can force a restart from a much earlier stage.

Phase 1 Design and Implementation

This phase involves translating the trading algorithm into a hardware description.

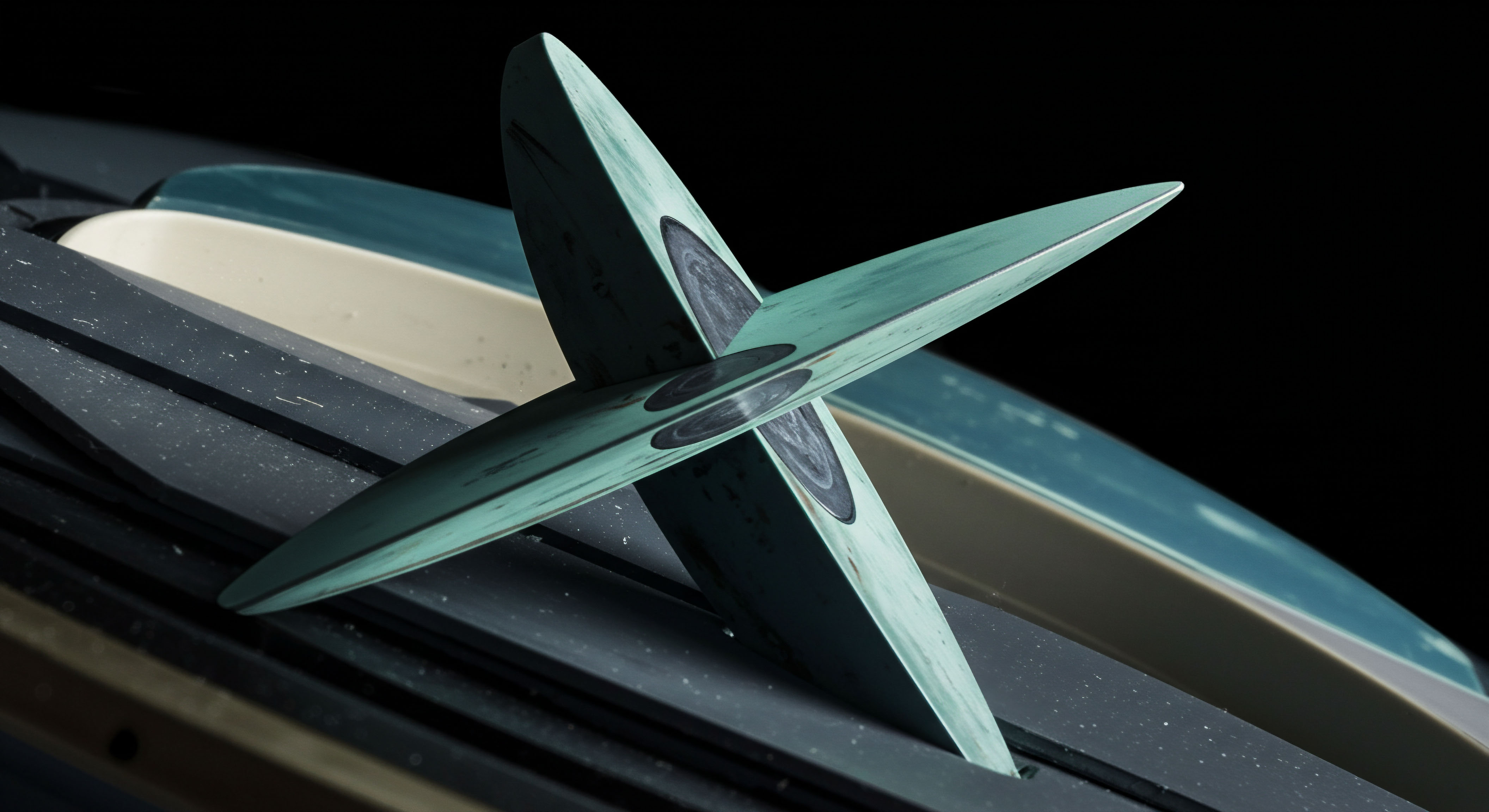

- Algorithmic Decomposition ▴ The trading logic must be broken down into its most fundamental components, suitable for parallel execution in hardware. This involves thinking in terms of data flows, state machines, and parallel processing paths.

- HDL Coding ▴ The engineer writes the hardware description in Verilog or VHDL. This code does not describe a sequence of operations; it describes the physical components of a circuit and their interconnections. Alternatively, High-Level Synthesis (HLS) can be used, where C/C++ code is written and then translated into HDL by a tool. While HLS can speed up initial development, the engineer must still structure the C/C++ code with a hardware implementation in mind and often needs to refine the generated HDL.

Phase 2 Verification the Critical Gate

Verification is the most time-consuming and critical part of the FPGA workflow, often consuming 70% or more of the total project time. A bug that makes it to production hardware can be disastrous.

In an FPGA workflow, the verification phase is paramount, as post-deployment fixes are orders of magnitude more complex than patching software.

The primary methodology used is the Universal Verification Methodology (UVM), an industry standard for creating robust, reusable, and structured verification environments.

- Testbench Development ▴ Using UVM, engineers build a sophisticated testbench that acts as a virtual world for the FPGA design (the “Design Under Test” or DUT). This testbench includes components like drivers to send stimulus, monitors to check outputs, and scoreboards to verify correctness.

- Simulation ▴ The HDL code is simulated within this testbench. This is a software-based process where the logic of the design is executed on a computer. Engineers run thousands of tests, including constrained-random tests, to try and uncover bugs in corner cases.

- Formal Verification ▴ In some cases, formal methods are used to mathematically prove that the design meets certain properties under all possible conditions, providing a level of assurance that simulation alone cannot.

Phase 3 Synthesis and Implementation

Once the design is verified in simulation, it must be translated into a physical configuration for the FPGA.

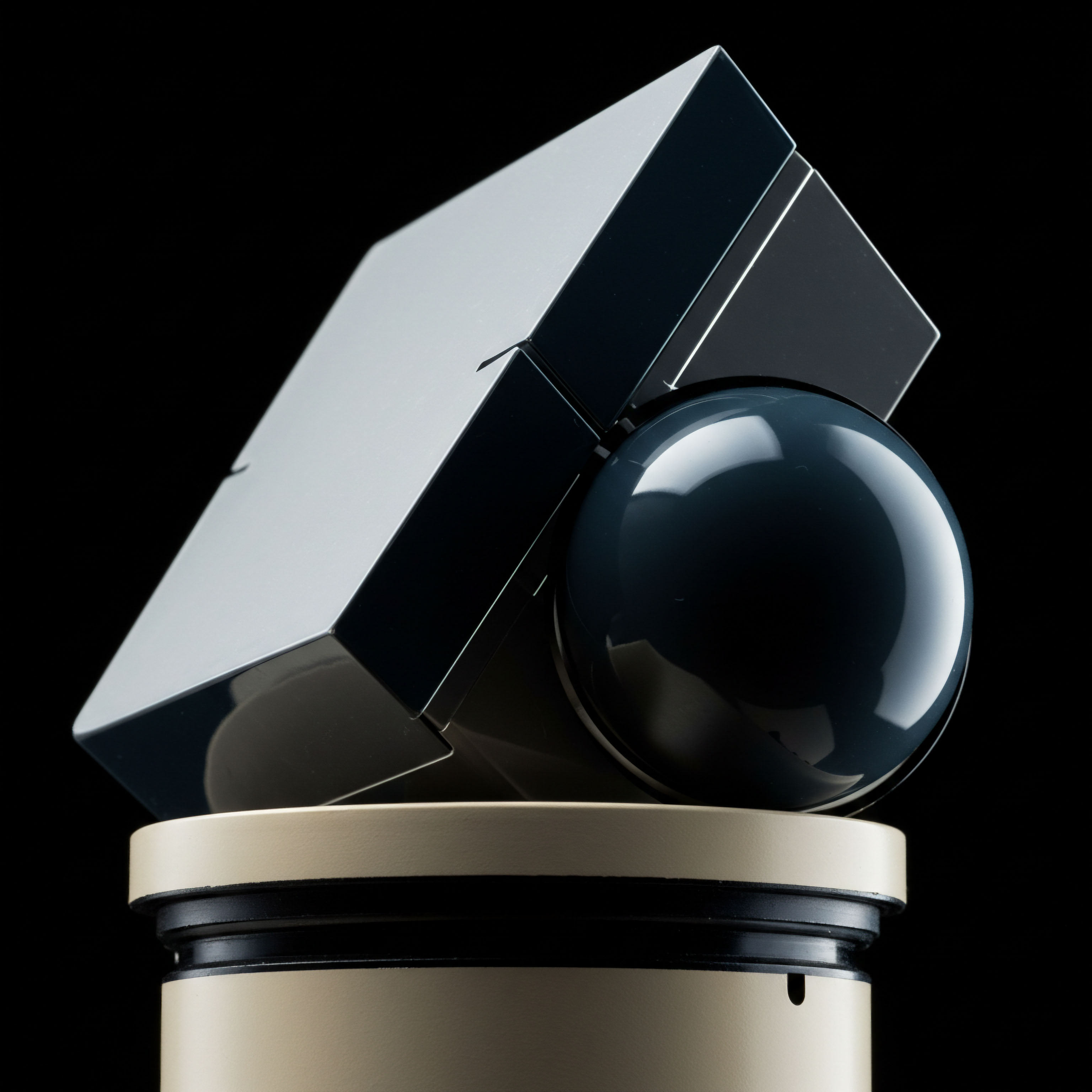

- Synthesis ▴ The verified HDL code is fed into a synthesis tool. This tool converts the abstract hardware description into a netlist, which is a list of fundamental logic gates (like AND, OR, and flip-flops) and their connections.

- Place and Route ▴ The synthesis output is then processed by a place-and-route tool. This tool takes the netlist and maps it onto the specific architecture of the target FPGA chip. It decides where to place each logic gate and how to route the electrical connections between them. This process is computationally intensive and can take many hours. A key challenge here is “timing closure,” ensuring that all signals can travel between gates within a single clock cycle.

- Bitstream Generation ▴ The final output is a bitstream file. This file contains the configuration data that will be loaded onto the FPGA to program its logic blocks and interconnects, creating the physical circuit.

Phase 4 Hardware Testing and Deployment

The final stage is to test the actual hardware.

- Hardware-in-the-Loop Testing ▴ The bitstream is loaded onto an FPGA on a development board, and the board is connected to a test system. This allows for real-world testing with live or recorded data, verifying that the hardware behaves as it did in simulation.

- Deployment ▴ Once validated, the FPGA card is installed in a production server in the data center. Any subsequent logic change requires repeating the entire workflow, from HDL modification through verification, synthesis, and bitstream generation.

The following table provides a comparative summary of the toolchains and key stages in each workflow.

| Development Stage | CPU Workflow | FPGA Workflow |

|---|---|---|

| Language/Input | C++, Python, Java | Verilog, VHDL, SystemVerilog, C/C++ (for HLS) |

| Primary Toolchain | GCC/Clang Compiler, IDE (e.g. Visual Studio), Debugger (GDB) | Xilinx Vivado / Intel Quartus, Mentor Questa / Synopsys VCS (for simulation), Synthesis Tools |

| Core Process | Write -> Compile -> Link -> Execute | Describe -> Verify -> Synthesize -> Place & Route -> Generate Bitstream |

| Verification Method | Unit Testing, Integration Testing, System Testing | UVM Simulation, Formal Verification, Hardware-in-the-Loop Testing |

| Typical Cycle Time | Hours to Days | Weeks to Months |

| Error Correction | Modify code, recompile (minutes). Deploy new executable. | Modify HDL, re-verify, re-synthesize (hours to days). Deploy new bitstream. |

References

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- O’Hara, Maureen. Market Microstructure Theory. Blackwell Publishers, 1995.

- Lehalle, Charles-Albert, and Sophie Laruelle. Market Microstructure in Practice. World Scientific Publishing, 2018.

- Pellerin, David, and Scott Thibault. Practical FPGA Programming in C. Prentice Hall, 2005.

- Ashenden, Peter J. The Designer’s Guide to VHDL. Morgan Kaufmann, 2008.

- Bergeron, Janick. Writing Testbenches ▴ Functional Verification of HDL Models. Springer, 2003.

- Spear, Chris, and Greg Tumbush. SystemVerilog for Verification ▴ A Guide to Learning the Testbench Language Features. Springer, 2012.

- Achronix Semiconductor. “FPGA vs. CPU vs. GPU for High-Performance Computing.” White Paper, 2021.

- Xilinx, Inc. “Vivado Design Suite User Guide ▴ High-Level Synthesis.” UG902, 2022.

- Intel Corporation. “Introduction to the Quartus II High-Level Synthesis.” White Paper, 2019.

Reflection

The examination of these two distinct development workflows moves beyond a simple technical comparison. It compels a deeper introspection into the core identity of a trading organization. The choice is not merely about selecting a technology; it is about defining the firm’s metabolic rate ▴ its capacity for adaptation, its tolerance for risk, and its fundamental approach to capturing market alpha.

Does your operational framework prioritize the fluid creativity of algorithmic development, allowing for rapid evolution and complex strategy deployment? Or does it demand the unyielding precision of hardware, sacrificing agility for the deterministic certainty of nanosecond-level execution?

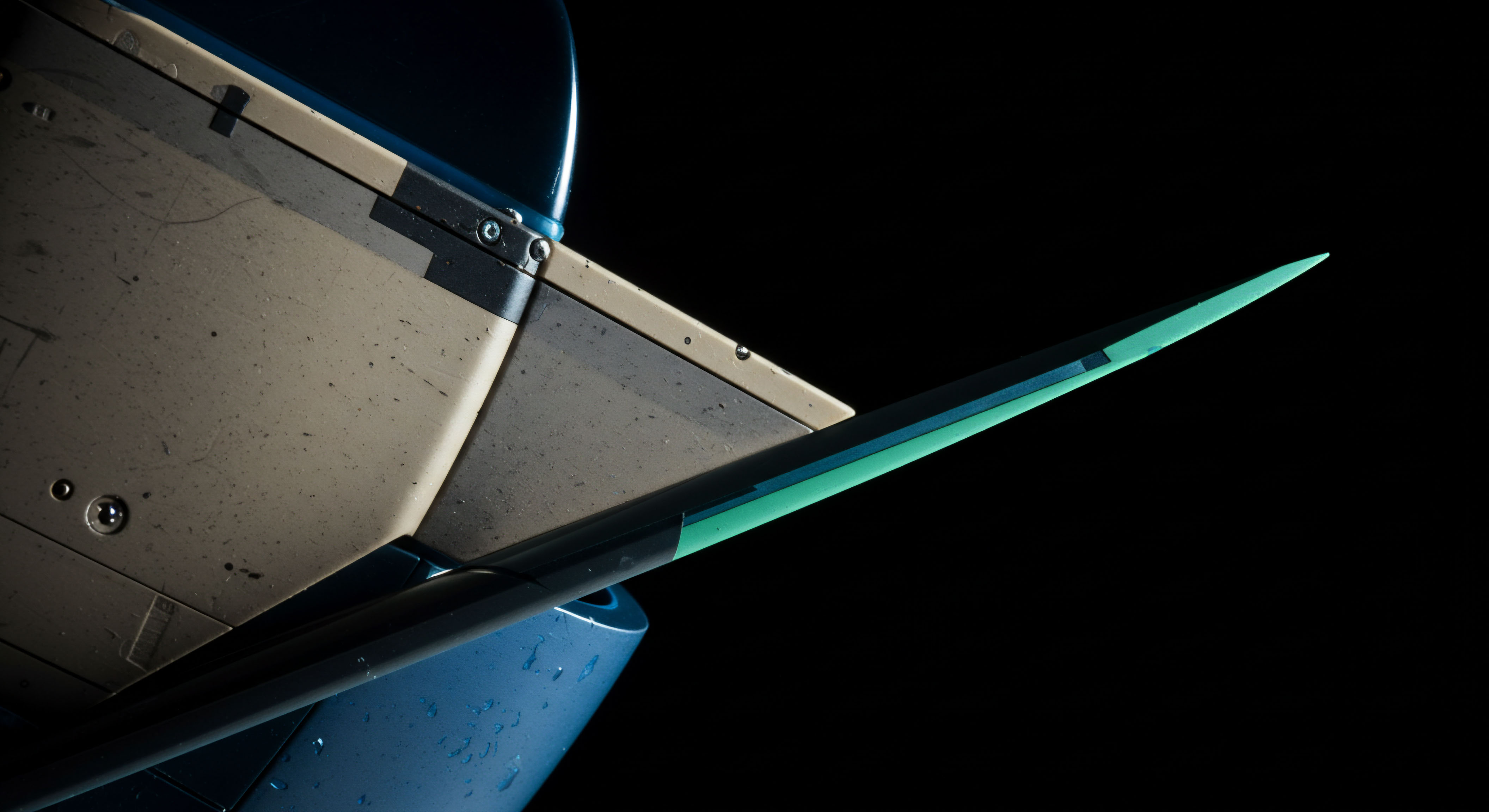

Viewing this decision through the lens of a systems architect reveals that the optimal solution is rarely a binary choice. Instead, the most sophisticated trading architectures are hybrid systems. They leverage each paradigm for its inherent strengths, creating a symbiotic relationship between software and hardware. In such a system, FPGAs are deployed at the edge, handling the most latency-critical tasks of data ingestion and order execution with ruthless efficiency.

CPUs, operating just microseconds behind, are tasked with the higher-level cognitive load ▴ managing overall strategy, performing complex risk calculations, and adapting to broader market dynamics. The true strategic edge, therefore, lies not in choosing one workflow over the other, but in mastering the integration of both. It is in the design of the interface between the deterministic speed of the hardware and the adaptive intelligence of the software that a firm’s most profound competitive advantages are forged.

Glossary

Development Workflow

Latency Profile

Hardware Description

Bitstream

Trading Logic

Latency

Trading System

Choice Between

Operational Risk

Determinism

High-Frequency Trading

Physical Circuit

Market Data

Place-And-Route

Synthesis

High-Level Synthesis

Formal Verification

Verification Methodology

Uvm

Verilog