Concept

The Physics of Financial Intent

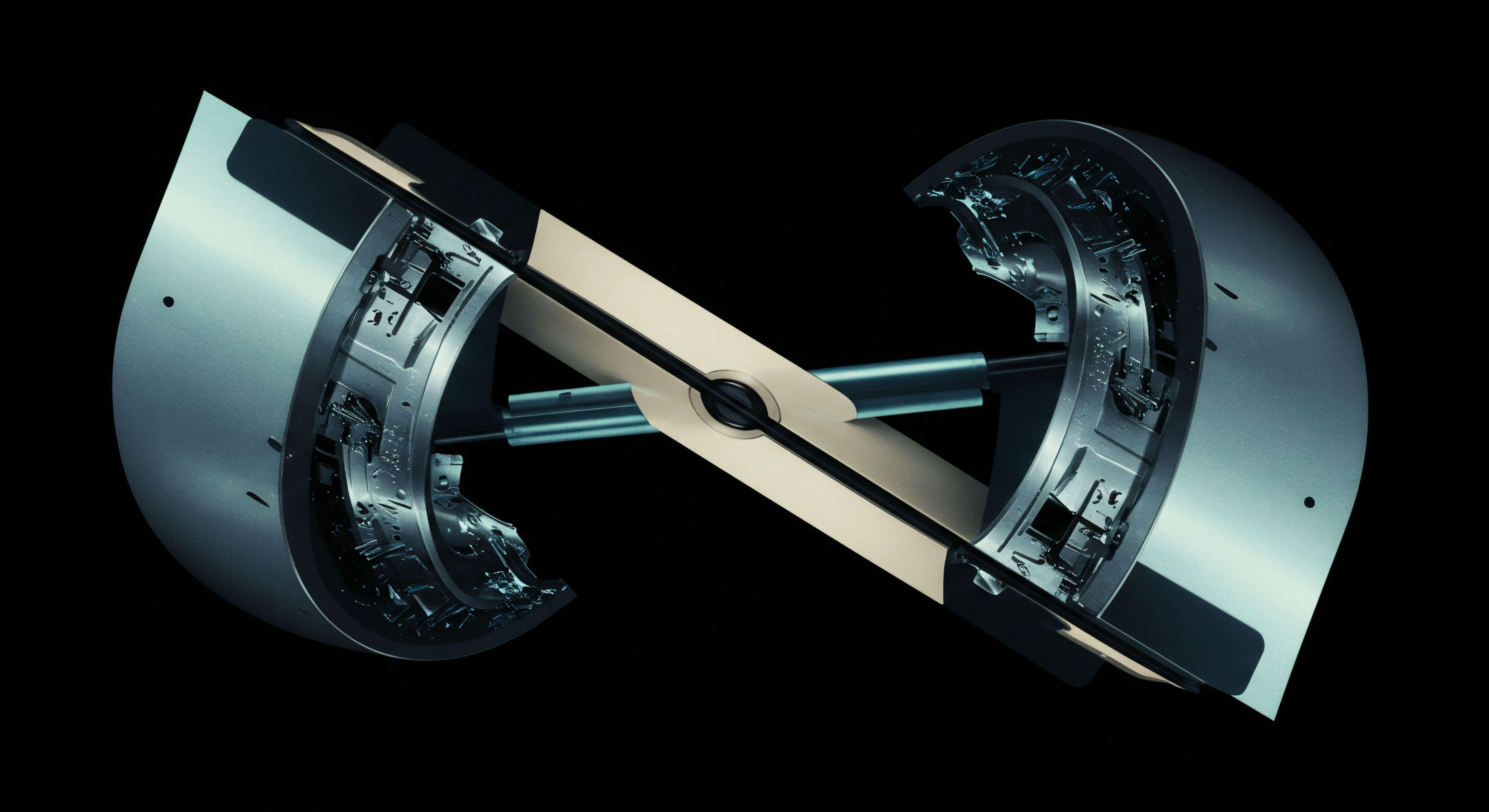

The migration of trading logic from the mutable realm of software to the crystalline structure of a Field-Programmable Gate Array represents a profound operational transformation. It is the process of translating abstract financial strategy, expressed in sequential lines of code, into a physical, deterministic system of interconnected logic gates. The primary challenge resides within this act of translation. A software-based algorithm is an orchestration of instructions, executed by a general-purpose processor that juggles countless tasks.

An FPGA implementation, conversely, is the strategy itself, rendered in silicon, where each logical step is a dedicated, physical pathway. This transition demands a complete reframing of how a firm perceives and interacts with its own intellectual property.

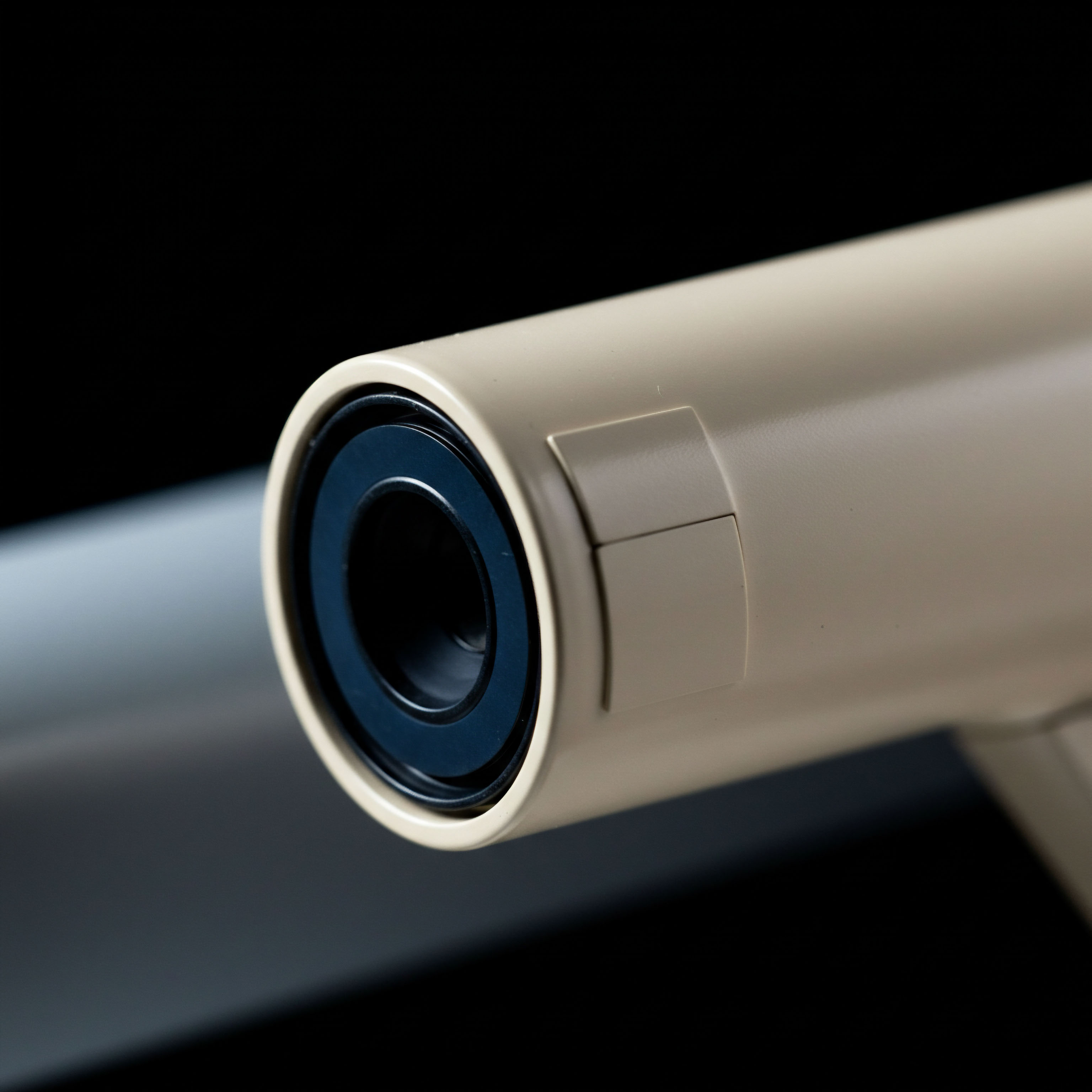

In the world of crypto derivatives, where market data arrives in torrential, parallel streams from fragmented liquidity venues, the sequential nature of CPU processing introduces non-deterministic latency. Operating system interrupts, cache misses, and process scheduling create a fog of uncertainty measured in microseconds, a timescale wholly incompatible with maintaining a competitive edge in options market-making or high-frequency delta hedging. The FPGA operates on the nanosecond scale, a domain governed by the speed of electrical signals through copper. The core intellectual hurdle is moving from managing sequences of commands to designing a purpose-built machine, an apparatus whose very architecture is the embodiment of a single, highly-optimized trading function.

From Probabilistic Execution to Deterministic Response

Software developers are masters of abstraction, building complex logic upon layers of existing frameworks and operating systems. This layered approach provides immense flexibility but obscures the underlying mechanics of execution. The FPGA engineer works with no such buffer.

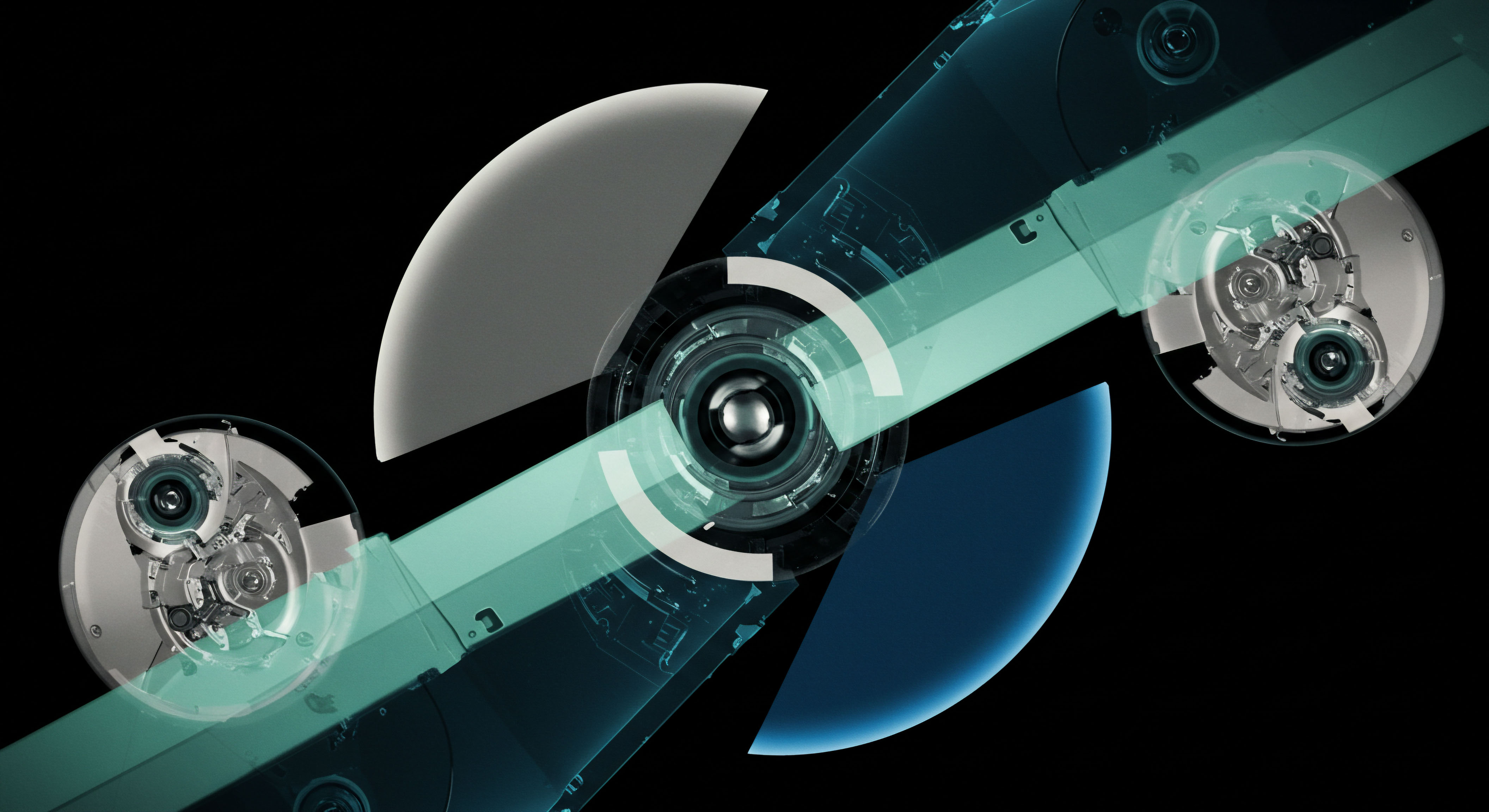

The challenge is one of irreducible complexity; the designer must confront the physical constraints of the chip itself, budgeting logic elements, managing heat dissipation, and accounting for signal propagation delays across the silicon die. Every component of a trading strategy, from the parsing of a WebSocket market data feed for a BTC perpetual future to the calculation of Greeks for a multi-leg ETH options spread, must be deconstructed and rebuilt as a network of parallel circuits.

The fundamental challenge is the intellectual and engineering shift from writing instructions for a machine to designing the machine itself.

This process exposes the true nature of the algorithm. In software, inefficiencies can be masked by faster processors or clever code optimization. In hardware, every inefficiency manifests as a physical limitation, consuming finite resources on the FPGA fabric. The migration is therefore an exercise in conceptual purification.

It forces a trading desk to distill its strategy to its most essential logical components, as only the most streamlined and parallelizable logic can be effectively transcribed into a hardware implementation. This is the central challenge ▴ it is a discipline of radical simplification and physical instantiation, demanding a rare synthesis of quantitative finance acumen and deep electrical engineering expertise.

Strategy

The Calculus of Irreversible Commitment

Choosing to migrate a critical trading function to an FPGA is a strategic commitment to a specific operational doctrine. This decision transcends a simple technology upgrade; it represents a firm’s declaration that a particular strategy’s latency profile is a primary driver of its profitability. The immense upfront investment in specialized talent and hardware necessitates a rigorous analysis of the trade-offs.

The high-level synthesis (HLS) toolchains that allow C++ code to be translated into hardware logic offer a bridge, yet they do not eliminate the underlying paradigm shift. The strategic challenge is identifying which components of the trading lifecycle benefit most from the deterministic, low-latency execution of an FPGA, versus those that require the adaptive flexibility of software.

For a crypto derivatives desk, this calculus is particularly sharp. A strategy focused on arbitraging pricing discrepancies in BTC options across multiple exchanges is a prime candidate for hardware acceleration. Its logic is repetitive, highly sensitive to latency, and involves processing parallel data streams.

Conversely, a newer, more exploratory strategy that requires frequent modification based on changing market volatility patterns or the introduction of new derivative products would be hindered by the rigid development cycle of hardware. The strategic imperative is to build a hybrid system where the FPGA handles the most latency-critical tasks ▴ market data processing, order acknowledgement, and risk checks ▴ while a software layer manages higher-level strategy decisions, parameter adjustments, and communication with the broader firm infrastructure.

Comparative Analysis of a Hedging System Deployment

The strategic implications of the software-versus-hardware path become tangible when examining the lifecycle of a specific system, such as an automated delta-hedging engine for a portfolio of Ethereum options. The table below outlines the divergent paths for development, deployment, and adaptation, illustrating the profound operational differences.

| Lifecycle Phase | Software-Based System (C++/Python) | FPGA-Based System (Verilog/HLS) |

|---|---|---|

| Initial Development |

Utilizes existing quant developers and software engineers. Rapid prototyping is possible. Focus is on algorithmic correctness and integration with existing libraries. |

Requires specialized hardware engineers with financial knowledge. Involves logic design, simulation, and synthesis. Prototyping is slow and methodical. |

| Testing & Verification |

Conducted in simulated environments and via replay of historical market data. Debugging is an iterative process using software tools. |

Requires extensive simulation with testbenches to verify every possible state. Hardware-in-the-loop testing is essential. Debugging is complex, often requiring logic analyzers. |

| Latency Profile |

Variable and non-deterministic (typically 5-50 microseconds). Subject to OS jitter, network stack delays, and CPU context switching. |

Fixed and deterministic (typically 50-500 nanoseconds). Latency is predictable down to the clock cycle. Jitter is virtually eliminated. |

| Adaptation & Modification |

Strategy logic can be modified, recompiled, and redeployed within hours. High flexibility to adapt to changing market conditions. |

Minor parameter changes can be fast. Significant logic changes require a full redesign, synthesis, and verification cycle, potentially taking weeks. |

| Operational Alpha Source |

Derived from the sophistication and adaptability of the trading model itself. |

Derived from the structural speed advantage in reacting to market events faster than competitors. |

The strategic decision hinges on whether a firm’s competitive advantage is rooted in algorithmic adaptability or raw execution speed.

Key Strategic Decision Factors

An institutional trading firm must evaluate several core factors before committing resources to an FPGA initiative. The process is one of intense internal scrutiny, weighing the potential gains in execution quality against the substantial operational costs and constraints.

- Strategy Longevity ▴ Is the trading logic foundational and unlikely to change for a significant period? A long-term, stable strategy justifies the high fixed costs of hardware development.

- Latency Sensitivity ▴ Can the P&L impact of a 100-nanosecond speed improvement be quantified? The value proposition is clearest in zero-sum, speed-based strategies like market making and latency arbitrage.

- Internal Skillset ▴ Does the firm possess, or can it acquire, the highly specialized talent required to design, verify, and maintain hardware systems? This is often the most significant barrier to entry.

- Infrastructure Readiness ▴ Is the entire trading stack, from network connectivity to exchange co-location, optimized to a level where nanosecond improvements at the logic layer are meaningful? An FPGA is only one component of an ultra-low latency system.

- Risk Profile ▴ The operational risk associated with deploying a rigid, hard-to-modify system into the volatile 24/7 crypto market must be fully understood and accepted. A bug in hardware is far more consequential than a bug in software.

Execution

Restructuring Logic for True Parallelism

The most demanding phase of the migration is the operational execution, which begins with the fundamental restructuring of the trading algorithm. A software algorithm designed for a CPU is inherently sequential. An FPGA design must be parallel from its inception.

Consider a simple Request for Quote (RFQ) response for a multi-leg BTC options spread on a platform like greeks.live. In software, the process might be:

- Receive the RFQ packet.

- Parse the packet to identify the legs of the spread.

- For each leg, fetch the current underlying price and implied volatility from memory.

- For each leg, calculate the theoretical price using a model like Black-Scholes.

- Aggregate the leg prices to get the spread price.

- Apply a pre-determined spread and generate the quote.

- Transmit the quote packet.

This sequential process is antithetical to the FPGA’s nature. The execution challenge is to re-architect this flow into a series of independent, parallel tasks. A dedicated hardware block would be built for each function. A parser block, multiple parallel pricing engine blocks (one for each potential leg), an aggregation block, and a transmission block would all operate simultaneously, pipelined together.

The data flows from one block to the next on each clock cycle. This architectural discipline of breaking down a problem into its most granular, parallelizable components is the core of effective FPGA execution.

Latency Attribution in the Execution Path

The ultimate goal of an FPGA deployment is the compression of time. Achieving this requires a granular understanding of where every nanosecond is spent. The following table provides a comparative breakdown of latency sources for a crypto options RFQ response, highlighting the profound difference in the execution path.

| Process Step | Typical Software Latency (ns) | Typical FPGA Latency (ns) | Rationale for Difference |

|---|---|---|---|

| Market Data Ingress (Packet to App) |

3,000 – 10,000 |

50 – 150 |

FPGA bypasses the kernel and network stack entirely (kernel bypass), feeding data directly from the NIC to the logic fabric. |

| Message Parsing & Decoding |

500 – 2,000 |

20 – 60 |

Dedicated parallel hardware parsers operate on the data stream as it arrives, character by character. |

| Trading Logic & Price Calculation |

1,000 – 5,000 |

40 – 100 |

Calculations are performed in parallel hardware pipelines, not as sequential CPU instructions. No cache misses or context switches. |

| Risk & Compliance Checks |

500 – 1,500 |

10 – 30 |

Pre-trade risk limits are encoded as hardware checks, executing in parallel with the core logic. |

| Order Generation & Egress |

2,000 – 8,000 |

50 – 120 |

The FPGA constructs the outbound packet directly and pushes it to the NIC, again bypassing the host OS and its associated jitter. |

| Total (Wire-to-Wire) |

7,000 – 26,500 ns |

170 – 460 ns |

The cumulative effect of eliminating software overhead and embracing parallelism results in a 1-2 order of magnitude latency reduction. |

Executing on FPGA is an exercise in mastering the physics of data flow, eliminating every source of non-deterministic delay.

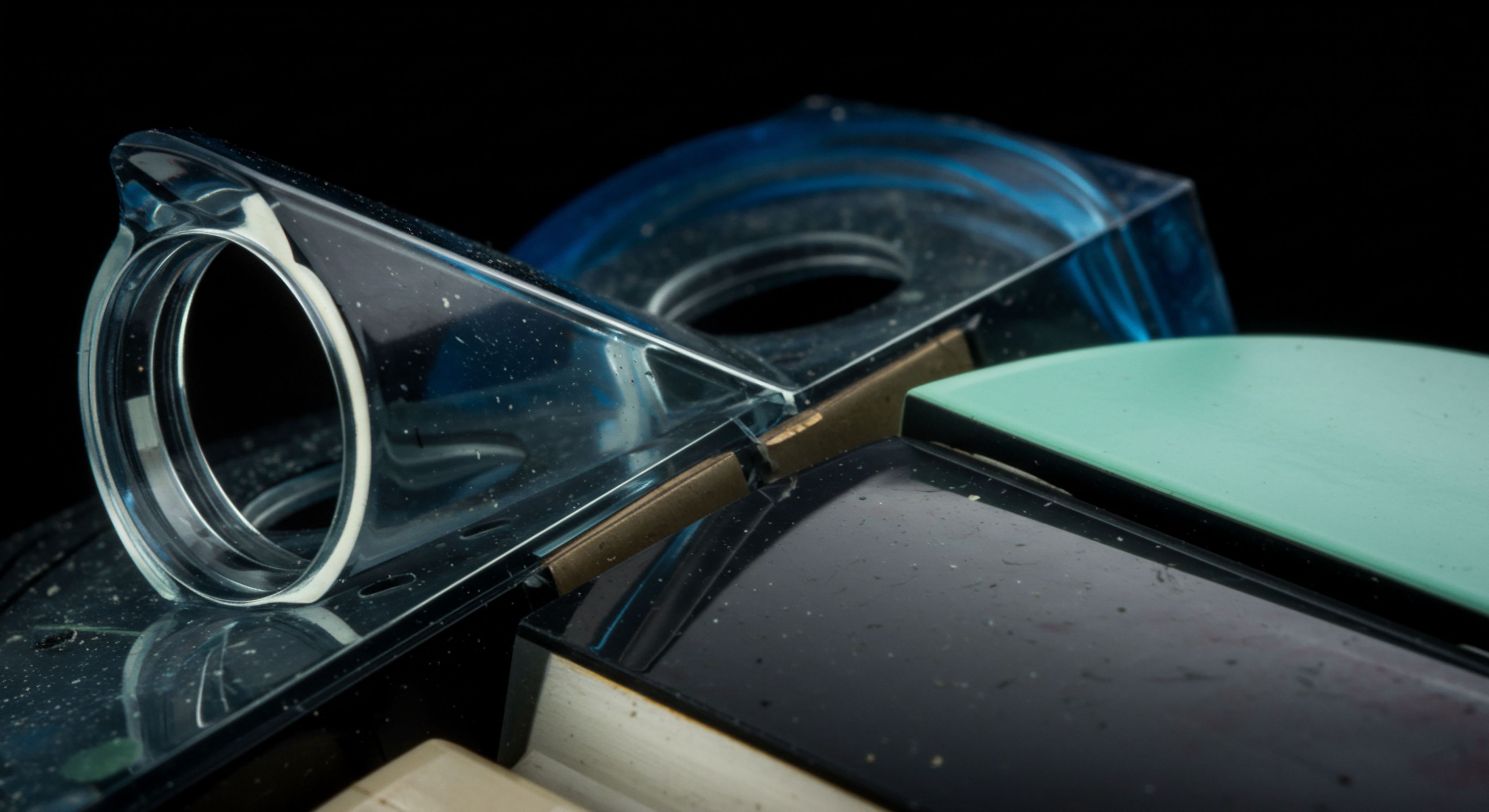

Hardware Resource Management

The physical space on an FPGA chip is a finite resource. The execution phase involves a meticulous budgeting process, allocating logic cells, memory blocks, and specialized processing units to different parts of the trading algorithm. An engineer must balance the performance requirements of the strategy against the physical constraints of the target device. Overly complex logic may not “fit” on the chip, or it may fail to meet the strict timing requirements needed for high-speed operation.

This resource management is a critical discipline, ensuring the final design is both performant and physically realizable. The challenge is one of optimization under constraint, a constant negotiation between algorithmic ambition and silicon reality.

References

- O’Hara, Mike. “FPGA & Hardware Accelerated Trading, Part Four – Challenges and Constraints.” WatersTechnology, 19 July 2012.

- Enyx. “Still using software? The 5 questions I get asked most about moving to FPGA trading.” Enyx, 22 Sept. 2020.

- Electronic Trading Hub. “Low Latency Trading Systems ▴ A Comparative Study of Software-based vs FPGA-based Solutions.” Electronic Trading Hub, 8 Feb. 2023.

- Exablaze. “Why More Trading Firms Are Moving to FPGA for Low-Latency Gains.” Exablaze, 1 July 2025.

- Various Authors. “What is the role of FPGAs in finance aside from HFT?” Quora, 22 April 2017.

Reflection

The Inscription of Strategy

The journey from software to hardware is ultimately about permanence. A software algorithm is a fluid entity, constantly evolving. An FPGA design is a crystallization of that logic, an inscription of strategic intent onto a physical medium. Contemplating this migration forces a deeper inquiry into the nature of a firm’s competitive advantage.

It compels a rigorous examination of which strategies are truly foundational, which elements of execution are non-negotiable, and where the line between adaptability and speed should be drawn. The process itself, independent of the outcome, yields a more profound understanding of the operational mechanics that drive profitability. The resulting system is a reflection of the firm’s highest convictions about how the market functions, rendered in silicon.

Glossary

Deterministic Latency

Crypto Derivatives

Market Data

High-Level Synthesis

Hardware Acceleration

Low Latency

Options Rfq