Concept

The decision to build a trading system upon a Central Processing Unit (CPU) or a Field-Programmable Gate Array (FPGA) is a foundational architectural choice that dictates the operational physics of the entire execution lifecycle. Viewing this choice through the lens of latency alone simplifies a more profound systemic distinction. The core of the matter resides in the fundamental processing paradigm of each technology. A CPU operates as a sequential instruction machine.

It fetches, decodes, and executes a stream of commands from memory, a process that, while incredibly fast and versatile, introduces inherent non-determinism through operating system interrupts, context switching, and complex memory hierarchies. This architecture excels at handling a vast and unpredictable range of tasks, making it the bedrock of general-purpose computing.

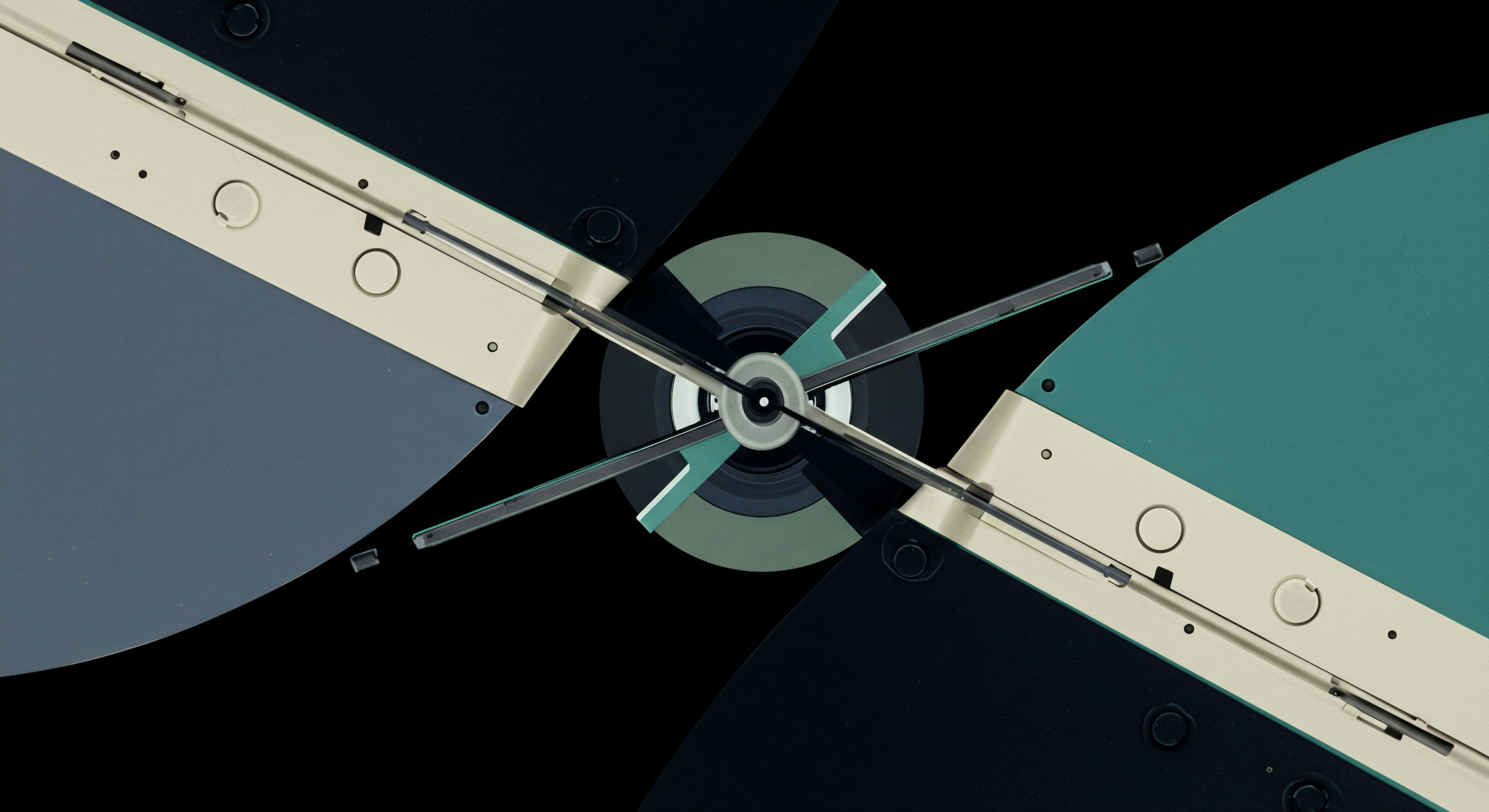

An FPGA represents a different philosophy of computation. It is a blank slate of logic gates and memory blocks that a hardware engineer configures to create a bespoke digital circuit. Once programmed, the FPGA performs its specific task not by executing a sequence of software instructions, but by physically embodying the algorithm in silicon. Data flows through a dedicated, parallel hardware path, eliminating the overhead of an operating system and the unpredictability of a general-purpose processor’s task scheduling.

This results in deterministic, repeatable, and ultra-low latency for the specific functions it is designed to perform. The primary distinction, therefore, is one of sequential versatility versus parallel specificity. A CPU-based system asks a generalist to perform a specialized task very quickly. An FPGA-based system forges a specialist for a single purpose, hardwiring its function into the physical layer of the machine itself.

A CPU offers flexibility through software instructions, while an FPGA provides speed through dedicated hardware circuits.

What Is the True Nature of Processing in Trading?

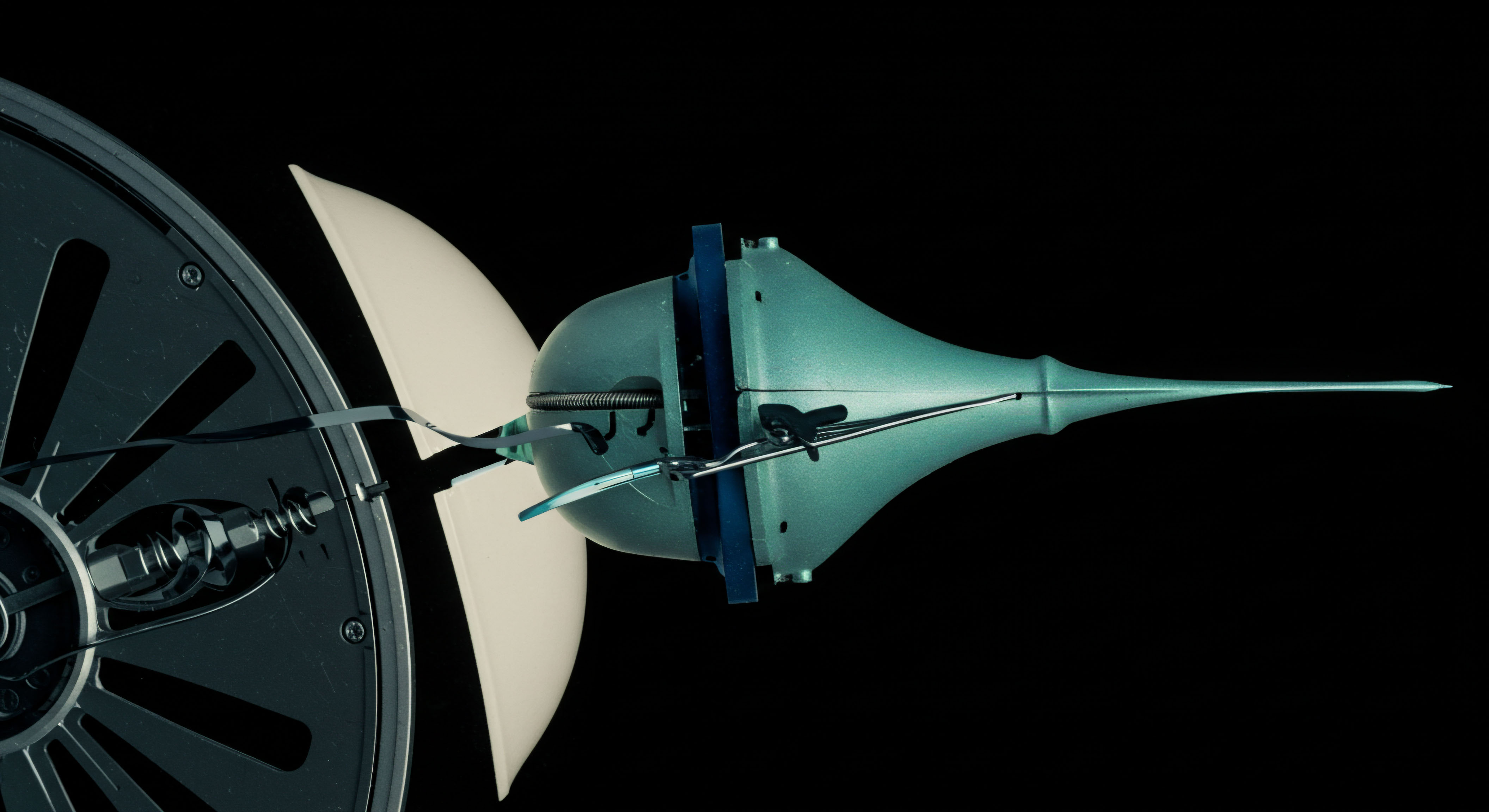

In the context of institutional trading, the processing of information is not a monolithic task. It is a chain of discrete events, from the moment a market data packet arrives at the network interface card to the instant an order is dispatched. A CPU approaches this chain as a series of software tasks to be managed by the kernel and executed by the processor cores. An FPGA, when integrated into the system, can excise specific links in this chain and replace them with dedicated hardware logic.

For instance, the task of decoding a FIX or FAST protocol message, which on a CPU involves parsing strings and handling various data fields in software, can be implemented as a hardware pipeline on an FPGA. As raw network data streams in, it flows through logic gates that are physically arranged to perform the decoding, producing the structured message with a latency measured in nanoseconds. This is a level of performance that a software program running on a CPU, regardless of optimization, struggles to match due to the fundamental overhead of its instruction-based architecture.

Architectural Philosophy and Systemic Impact

The selection of CPU or FPGA hardware establishes the architectural philosophy of a trading firm. A purely CPU-based approach prioritizes flexibility and speed of development. New strategies can be coded in high-level languages like C++, compiled, and deployed rapidly.

This system is adaptable, capable of running complex predictive models, and benefits from a vast ecosystem of software development tools and a large talent pool of programmers. The systemic trade-off is accepted latency and jitter, the small, unpredictable variations in processing time that can affect queue position at the exchange.

An FPGA-centric philosophy, conversely, prioritizes deterministic low latency above all else. The firm makes a strategic commitment to hardware engineering, accepting longer development cycles and higher complexity in exchange for a structural speed advantage in specific, latency-sensitive operations. This choice has a cascading impact on the entire organization, requiring specialized engineering talent (hardware description language experts), different testing methodologies, and a more rigid development process.

The most advanced trading systems today reflect a synthesis of these two philosophies, creating a hybrid architecture where each component is deployed according to its intrinsic strengths. This allows the system as a whole to achieve a superior operational state, blending the raw speed of hardware with the strategic flexibility of software.

Strategy

The strategic deployment of CPU and FPGA technologies within a trading system is a function of a firm’s market objectives, risk tolerance, and technological maturity. The choice is not a simple binary selection but a nuanced allocation of resources to forge a competitive edge. The strategies governing their use are deeply intertwined with the market microstructure and the specific alpha-generating activities the firm pursues.

The CPU Strategy a Focus on Agility and Complexity

A strategy centered on CPU-based systems is one that prioritizes analytical depth and developmental velocity. This approach is optimal for firms whose trading models rely on complex calculations, statistical arbitrage, or machine learning algorithms that are too intricate or dynamic for direct implementation in hardware. The strategic advantage of a CPU system lies in its ability to rapidly iterate on and deploy sophisticated logic.

- Development Speed A new trading idea can be translated from a quantitative model into C++ or Python code and deployed within days or weeks. This agility allows the firm to adapt quickly to changing market conditions or to exploit newly discovered inefficiencies.

- Algorithmic Complexity CPUs can execute highly complex, multi-faceted algorithms that may require large amounts of memory or involve decision trees with numerous branches. This is suitable for strategies that are not purely latency-sensitive, such as mid-frequency statistical arbitrage or the execution of large institutional orders using algorithms like VWAP or TWAP.

- Talent Accessibility The pool of elite software engineers proficient in languages like C++ is substantially larger than the pool of hardware engineers skilled in Verilog or VHDL. A CPU-centric strategy aligns with a more readily available talent base, reducing recruitment friction and cost.

The operational plan for a CPU-based strategy involves continuous software optimization. This includes kernel bypass techniques to reduce network stack overhead, careful management of CPU cache to ensure data locality, and fine-tuning compiler flags to produce the most efficient machine code. The goal is to minimize software-induced latency to the greatest extent possible, creating a highly-tuned general-purpose machine.

The FPGA Strategy the Pursuit of Deterministic Speed

An FPGA-based strategy is a direct assault on latency. It is predicated on the understanding that in many high-frequency scenarios, being microseconds, or even nanoseconds, faster than a competitor is the primary determinant of profitability. The strategic objective is to gain a persistent advantage in the time-priority queue of the exchange’s matching engine.

In high-frequency trading, the architecture that processes market data and places orders the fastest often captures the opportunity.

This strategy is most potent for specific, well-defined tasks that occur at the very edge of the trading system, closest to the exchange. These include:

- Market Data Processing FPGAs can parse raw market data feeds (e.g. ITCH/OUCH) and update an order book in hardware, often before a CPU-based system has even processed the network packet at the kernel level.

- Pre-Trade Risk Checks Simple risk checks, such as fat-finger error prevention or position limit validation, can be hardwired into the FPGA. This allows an order to be validated and passed on for execution with minimal delay.

- Ultra-Low Latency Order Execution For simple, reflexive strategies (“if event A occurs, send order B”), the entire logic can be contained within the FPGA. The system can react to a market data update and dispatch an order in a few hundred nanoseconds, a speed unattainable by software-based systems.

The strategic commitment here is significant. FPGA development is resource-intensive, requiring specialized hardware, expensive software licenses, and a highly skilled engineering team. The verification and testing process is also more rigorous, as bugs in hardware are more difficult to patch than software bugs. The payoff is a system with deterministic performance; the latency for a given operation is constant and predictable, a quality known as low “jitter.”

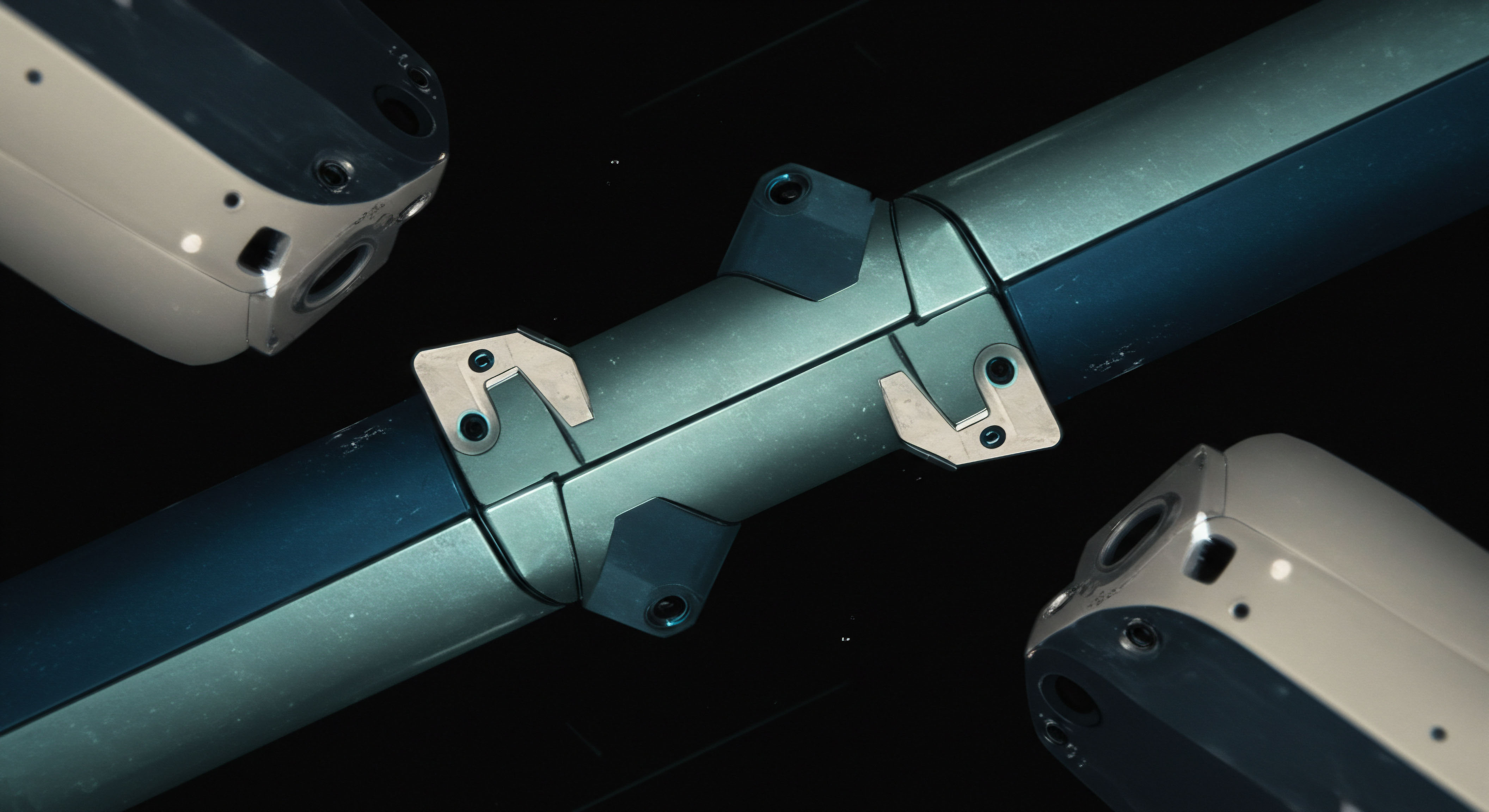

The Hybrid System a Synthesis of Strengths

The dominant strategy in modern electronic trading is the hybrid system, which combines the strengths of both CPU and FPGA architectures. This approach recognizes that a trading workflow contains components with different performance requirements. The strategy is to offload the most latency-critical and deterministic tasks to the FPGA, while leaving the more complex, higher-level strategic decisions to the CPU.

A typical hybrid architecture functions as follows:

- An incoming market data packet from the exchange is received directly by an FPGA.

- The FPGA handles the network protocol stack (e.g. TCP/IP), decodes the financial protocol (e.g. FAST/FIX), performs initial order book updates, and may even apply simple, pre-programmed trading logic.

- The processed data, now in a clean and structured format, is passed to the CPU via a low-latency interconnect like PCI Express.

- The CPU executes the core trading strategy, which may involve more complex calculations, historical data analysis, or risk management assessments.

- If a trading decision is made, the CPU sends a command back to the FPGA, which then constructs the order packet and sends it to the exchange, again bypassing the host operating system’s network stack.

This symbiotic relationship allows a firm to achieve the best of both worlds. It gains the nanosecond-level reaction time of the FPGA for the most competitive parts of the trade lifecycle, while retaining the flexibility and analytical power of the CPU for sophisticated strategy development. The following table provides a strategic comparison of these architectures.

| Strategic Factor | CPU-Centric Strategy | FPGA-Centric Strategy | Hybrid System Strategy |

|---|---|---|---|

| Primary Goal | Algorithmic flexibility and rapid development. | Deterministic low latency and queue priority. | Optimized latency for critical paths, flexibility for complex logic. |

| Optimal Use Case | Mid-frequency stat-arb, complex execution algos (VWAP), strategies requiring large datasets. | Market making, liquidity sniping, simple reflexive arbitrage. | Nearly all modern HFT and sophisticated electronic trading strategies. |

| Development Cycle | Short (days/weeks). | Long (months/quarters). | Mixed; hardware cycle is long, but software can iterate faster. |

| Associated Cost | Lower initial hardware cost, primary cost in software developers. | High cost for hardware, EDA tools, and specialized engineers. | Highest overall cost, requiring investment in both hardware and software expertise. |

| Performance Profile | Microsecond-level latency, higher jitter. | Nanosecond-level latency, very low jitter. | Nanosecond-level latency for FPGA tasks, microsecond for CPU tasks. |

Execution

The execution framework for a trading system is where architectural theory translates into operational reality. The differences in execution between CPU and FPGA-based systems are stark, manifesting in everything from the physical system architecture to the development workflow and the quantitative performance metrics that define success in electronic markets.

How Does the System Architecture Differ in Practice?

The physical and logical layout of a trading system is fundamentally shaped by the choice of processing technology. A deep dive into the architecture reveals the granular differences in how data flows from the market to the trading logic and back again.

The Pure CPU Execution Path

In a system relying solely on CPUs, the journey of a market data packet is governed by a series of software layers.

- Network Interface Card (NIC) The packet arrives at a standard server NIC.

- Kernel Network Stack The packet is handed off to the operating system’s kernel. The kernel processes the TCP/IP headers, a task that consumes valuable microseconds and introduces context-switching overhead.

- Application Layer The data is copied from kernel space to user space, where the trading application is running. This copy operation itself adds latency.

- Protocol Decoding The C++ application receives a raw data buffer and must parse it to decode the financial protocol (e.g. FIX), identify the instrument, price, and volume.

- Strategy Logic The decoded information is used as an input to the trading strategy algorithm running on the CPU.

- Order Generation If a trade is triggered, the application constructs a new packet, which must travel back down through the user-space/kernel-space boundary and the kernel’s network stack before being sent out by the NIC.

While techniques like kernel bypass (e.g. DPDK) can remove some of these steps, the core logic and protocol handling remain software-bound processes executed sequentially by the CPU.

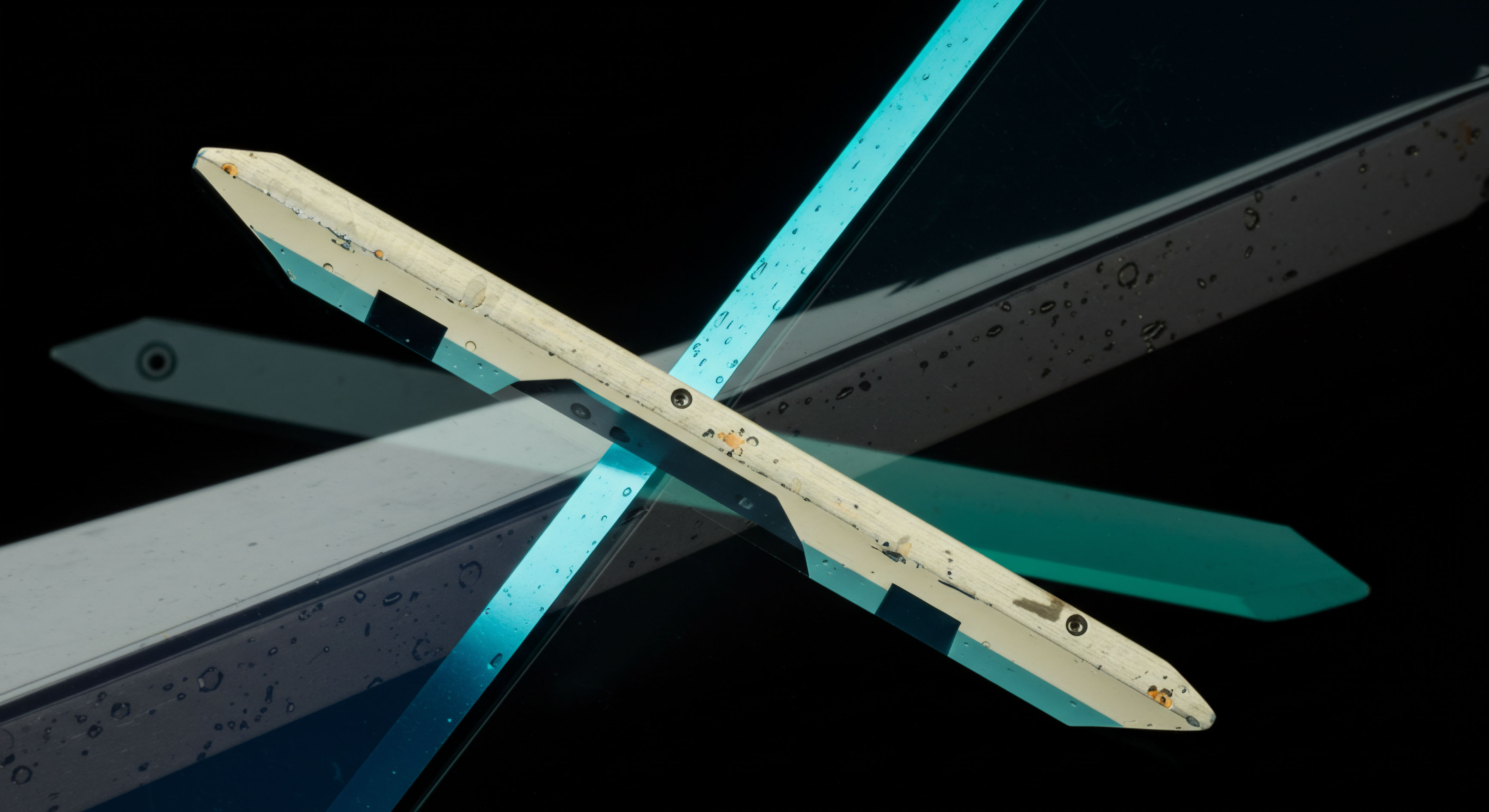

The FPGA-Accelerated Execution Path

A hybrid system incorporating an FPGA fundamentally re-engineers this data path for speed.

- FPGA NIC The packet arrives at a specialized NIC that contains an FPGA. The raw Ethernet frames are fed directly into the FPGA’s logic fabric, completely bypassing the server’s main CPU and operating system.

- Hardware-Based Processing Inside the FPGA, a dedicated, pipelined circuit performs several tasks in parallel:

- TCP/IP Offload The network session is managed directly in hardware.

- Protocol Decoding The FIX/FAST message is decoded instantly as it streams through the logic gates.

- Book Building The FPGA can maintain a copy of the limit order book for the most critical instruments in its own on-chip memory (BRAM).

- Triggering Simple trading logic (“if price drops below X, fire order Y”) can be executed directly on the FPGA.

- Low-Latency Handoff For more complex decisions, the FPGA passes the structured, decoded data directly to the CPU’s memory over a high-speed bus like PCIe. This handoff is highly efficient.

- CPU-Level Strategy The CPU performs its higher-level analysis using the pre-processed data from the FPGA.

- Hardware Order Path When the CPU decides to trade, it sends a small command to the FPGA. The FPGA constructs the full order packet in hardware and sends it to the exchange network, again with zero OS involvement.

A hybrid system uses the FPGA as a highly specialized co-processor, handling the most time-sensitive tasks at the hardware level.

Quantitative Performance and Development Workflow

The operational differences are most clearly illustrated by comparing the quantitative metrics and the development processes associated with each technology. The choice of architecture is a trade-off between raw performance and development agility.

The table below provides a quantitative comparison of key performance and operational metrics. These figures represent typical values and highlight the order-of-magnitude differences between the approaches.

| Metric | Optimized CPU System | FPGA-Accelerated System | Systemic Implication |

|---|---|---|---|

| End-to-End Latency | 2 – 10 microseconds (µs) | 200 – 800 nanoseconds (ns) | FPGA provides a 10-50x reduction in latency, critical for queue priority. |

| Latency Jitter | High (tens of µs) | Extremely Low (tens of ns) | FPGA offers deterministic, predictable performance; CPU performance varies due to OS/cache effects. |

| Throughput | High (millions of messages/sec) | Very High (tens of millions of messages/sec) | FPGA can process data at line rate without being a bottleneck. |

| Development Language | C++, Java, Python | Verilog, VHDL, HLS (High-Level Synthesis) | CPU development uses common software skills; FPGA requires specialized hardware engineering expertise. |

| Time-to-Market | Fast (days to weeks) | Slow (months to a year) | CPU allows for rapid strategy iteration; FPGA development is a long-term infrastructure investment. |

| Flexibility/Adaptability | Very High | Low | Software is easily changed; hardware changes require a full re-synthesis and verification cycle. |

The development workflow for FPGAs is a significant operational consideration. It mirrors the process of designing a physical microchip. Engineers write code in a Hardware Description Language (HDL) that describes the desired circuit. This code is then synthesized, a process where software tools translate the HDL into a low-level configuration of logic gates.

Finally, the design goes through place-and-route, where the synthesizer maps the logic onto the physical resources of the FPGA. This entire cycle can take hours or even days for a complex design, a stark contrast to the seconds or minutes it takes to compile a C++ application. This lengthy feedback loop makes FPGA development inherently slower and more deliberate than software engineering.

References

- Purohit, Aarush. “FPGA for High-Frequency Trading ▴ Reducing Latency in Financial Systems.” ResearchGate, 2021.

- Subramoni, Hari, et al. “High Frequency Trading Acceleration using FPGAs.” 2012 IEEE 26th International Parallel and Distributed Processing Symposium Workshops & PhD Forum, 2012.

- Thomas, Ben, et al. “I feel the need for speed ▴ Exploiting latest generation FPGAs in providing new capabilities for high frequency trading.” Proceedings of the Platform for Advanced Scientific Computing Conference, 2021.

- Gupta, Anshul. “High Frequency Trading on FPGA.” MIT, 2014.

- “Automated Trading Systems ▴ Architecture, Protocols, Types of Latency.” QuantInsti Blog, 11 Sept. 2024.

- “How the first true Low-Latency market was designed and architected.” Electronic Trading Hub, 6 Mar. 2025.

- “Financial Services Solutions | Altera FPGAs for Low Latency.” Intel Corporation, 2023.

- “Revolutionizing Finance and Fintech with FPGA Development Boards.” Medium, 25 May 2024.

- “Self-Evolving Machine Learning Algorithm for Stock Market Trading Implemented on an FPGA.” Electrical & Computer Engineering, University of Massachusetts Amherst, 2020.

- “Xilinx Seeks to Democratise FPGA in Trading with Accelerated Algo Framework.” A-Team Insight, 24 Feb. 2021.

Reflection

The analysis of CPU versus FPGA architectures ultimately leads to a reflection on the nature of a firm’s core competencies. The selection of a technology stack is an expression of institutional identity. Is the organization’s primary strength in its quantitative researchers and software engineers, capable of devising and rapidly deploying complex models?

Or does its advantage lie in a deep-seated engineering culture, committed to building and maintaining a structural, hardware-based speed advantage? The hybrid model, while architecturally superior, presents its own challenge ▴ the effective fusion of two distinct engineering cultures.

What Is the Ultimate Goal of Your System Architecture?

Answering this question requires looking beyond simple metrics of latency or throughput. It demands an honest assessment of the firm’s strategic horizon. The knowledge gained about these systems is a component in a larger operational framework.

A truly superior edge is achieved when the technological architecture is a perfect reflection of the firm’s trading philosophy and risk appetite. The ultimate goal is to build a system where technology becomes a seamless extension of strategy, creating a cohesive whole that is resilient, adaptive, and relentlessly efficient in its pursuit of alpha.

Glossary

Trading System

Fpga

Logic Gates

Low Latency

Cpu

Market Data

Fast Protocol

Market Microstructure

Verilog

Network Stack

Kernel Bypass

Fpga Development

Hybrid System