Concept

The Nature of the Machine

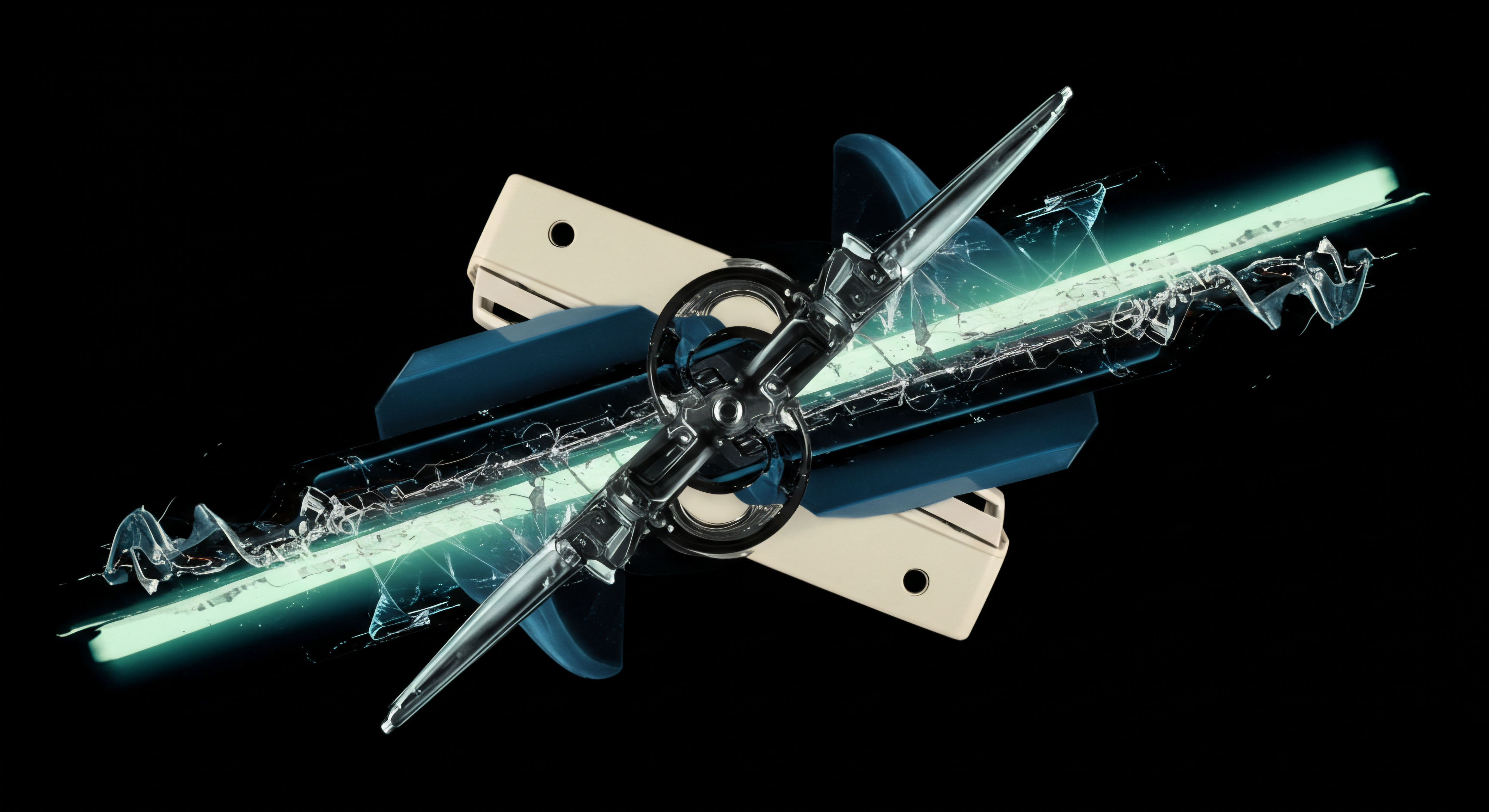

The decision between a Field-Programmable Gate Array (FPGA) and a software-based engine for quote validation is a choice between two fundamentally different philosophies of computation. It is an election between bespoke, forged hardware and versatile, malleable software. A software-based system operates on a general-purpose processor (CPU), a marvel of sequential instruction execution.

The CPU is an executive, capable of performing any task given the correct instructions, but it must process these instructions in a sequence, managed by an operating system that introduces its own delays and non-determinism. This architecture provides immense flexibility; changing the task is as simple as loading a new program.

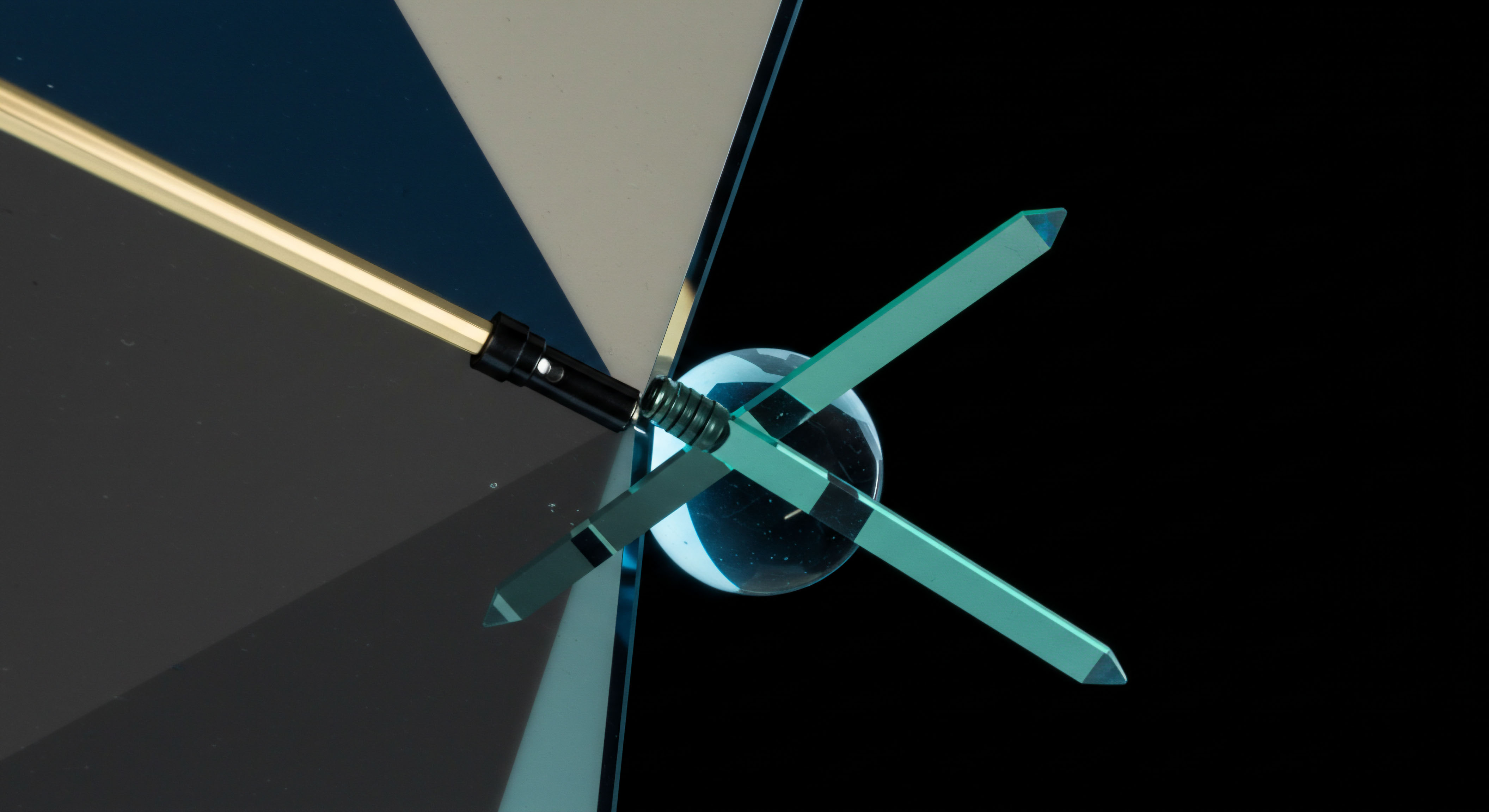

An FPGA, conversely, is a silicon canvas of uncommitted logic gates. It is not programmed in the traditional sense; it is configured. Using a Hardware Description Language (HDL), a developer describes a digital circuit that is then physically mapped onto the chip. The result is a piece of hardware tailored to a single, specific purpose, such as the validation of a financial quote.

This configuration performs its task not by executing a sequence of instructions, but through the physical flow of electrons through a purpose-built circuit. This distinction is the root of every primary difference that follows, from latency and determinism to development cycles and operational costs.

Parallelism versus Sequential Logic

The core operational divergence stems from how each engine processes a task. A software-based quote validation engine, running on a multi-core CPU, must break the problem down into a series of steps. Even with modern multi-threading, the process is governed by the CPU’s need to fetch, decode, and execute instructions, with an operating system scheduling and managing resources.

This introduces variability, or “jitter,” in processing times. The validation of one quote may take a few microseconds, the next one slightly longer, depending on other processes competing for the CPU’s attention.

An FPGA executes its logic in parallel, as the circuit is physically wired to perform all necessary checks simultaneously, providing a deterministic and predictable outcome.

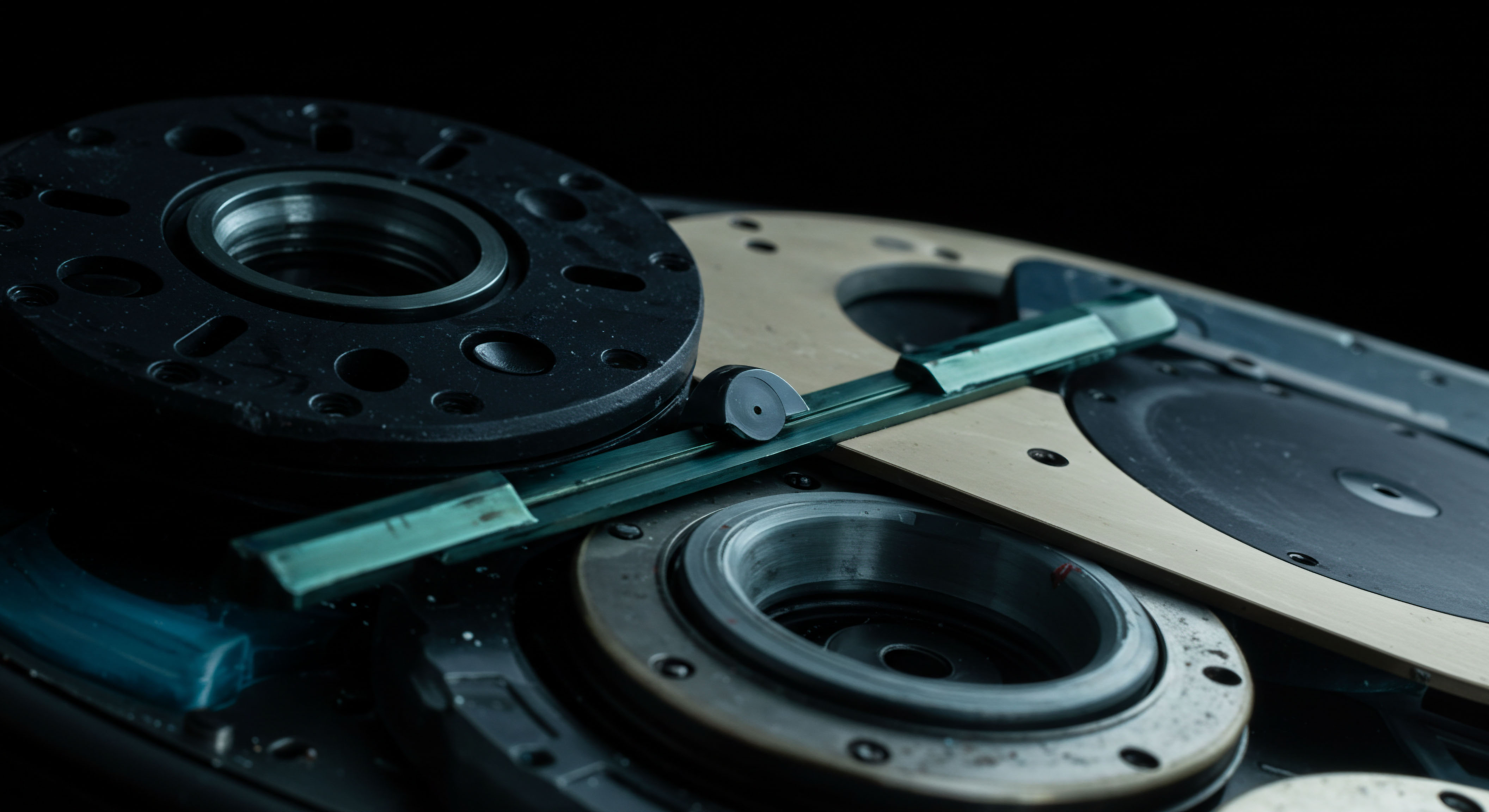

An FPGA-based engine, having been configured at the hardware level, operates with massive parallelism. A quote arriving at the engine’s input triggers a cascade of logic that occurs simultaneously. All validation checks ▴ format, price limits, size, checksums ▴ can be performed in parallel within a fixed number of clock cycles.

The time taken to validate a quote is therefore deterministic and predictable down to the nanosecond. This is the operational equivalent of a bespoke assembly line built for one product, where every stage happens in perfect, unvarying synchrony, contrasted with a master craftsman who, while versatile, must perform each task one after another.

Strategy

The Strategic Calculus of Speed and Agility

Choosing between an FPGA and a software-based quote validation engine is a strategic decision that balances the immutable laws of physics against the practical demands of business agility. The selection process requires a clear-headed assessment of an institution’s operational goals, risk tolerance, and competitive landscape. A software-based approach prioritizes a rapid time-to-market and operational flexibility.

The availability of a large pool of C++ or Java developers means that new validation logic can be developed, tested, and deployed within familiar agile frameworks. This adaptability is paramount in markets where regulations or exchange rules change frequently, allowing a firm to modify its logic swiftly.

Conversely, the adoption of an FPGA-based engine is a strategic commitment to achieving the lowest possible latency and the highest degree of determinism. This path is chosen when the competitive advantage is measured in nanoseconds, a common reality in high-frequency market making and certain arbitrage strategies. The trade-off for this raw performance is a significant increase in development complexity and a reduction in flexibility.

Hardware development cycles are inherently longer, and the skillset required is far scarcer. The strategic implication is clear ▴ FPGA is a tool for weaponizing speed where speed is the primary variable for success.

Comparative Strategic Factors

The decision matrix for selecting the appropriate engine technology involves a multi-faceted analysis of costs, performance, and operational realities. Each factor represents a strategic trade-off that must align with the firm’s overarching objectives.

| Strategic Factor | Software-Based Engine | FPGA-Based Engine |

|---|---|---|

| Time-to-Market | Fast. Leverages existing software development talent and agile methodologies. | Slow. Requires lengthy hardware design, synthesis, and verification cycles. |

| Development Cost | Lower initial cost due to widespread availability of developers and tools. | Higher initial cost due to specialized hardware, expensive development tools, and scarcity of talent. |

| Operational Cost (Power) | Higher. General-purpose CPUs are less power-efficient for specialized tasks. | Significantly lower. FPGAs offer superior performance-per-watt for targeted computations. |

| Performance Ceiling | Limited by CPU architecture and operating system overhead. Latency is higher and non-deterministic. | Extremely high. Offers the lowest possible latency, measured in nanoseconds, with deterministic processing. |

| Flexibility & Updates | High. Logic can be updated and redeployed quickly. | Low. Changes require a full hardware recompilation, which is time-consuming and complex. |

Systemic Impact on Trading Infrastructure

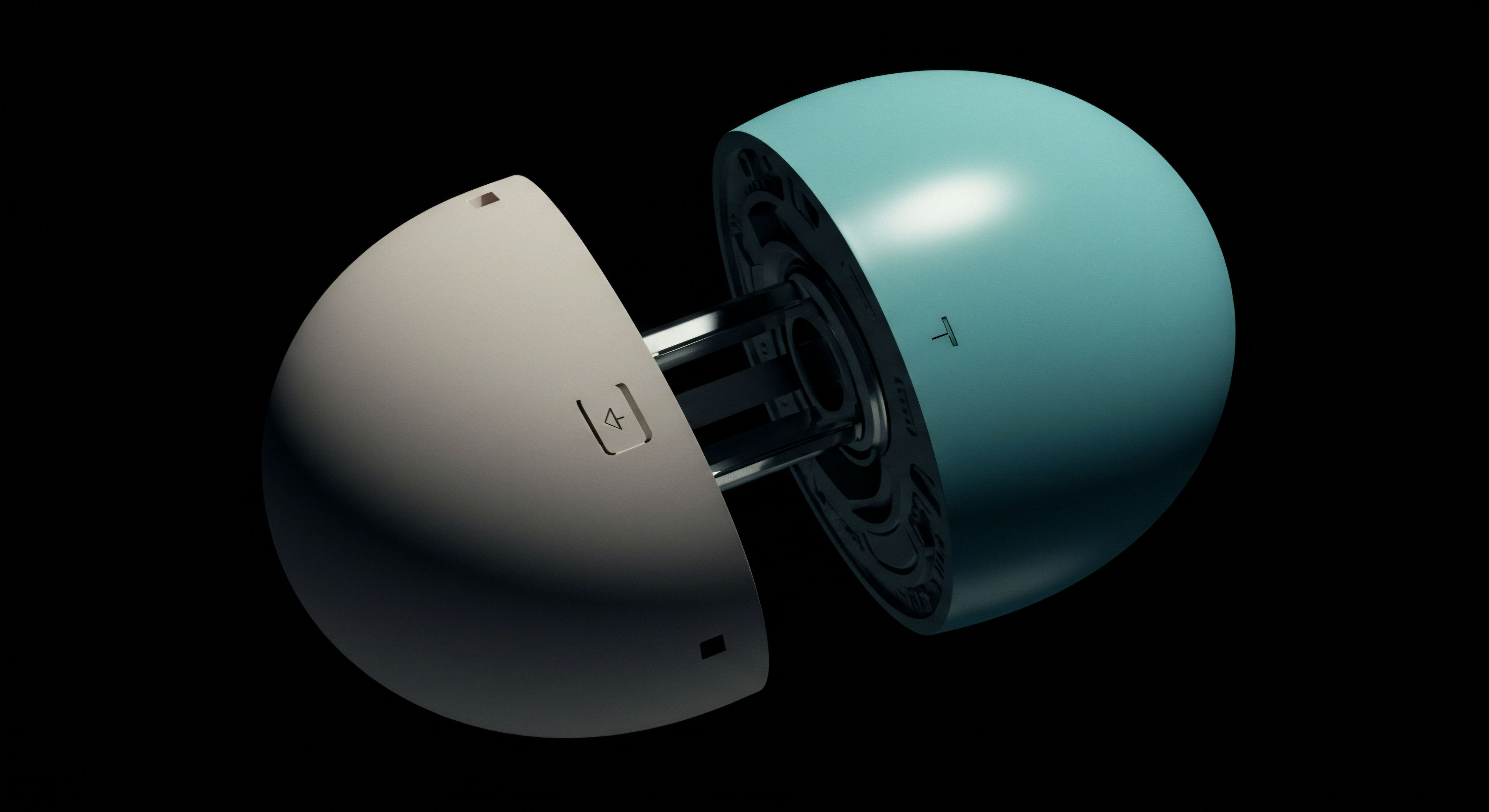

The integration of a quote validation engine has systemic consequences for the entire trading apparatus. A software-based engine fits neatly into existing server-based architectures. It runs as another process on a server, managed by the same IT infrastructure that handles other trading components. This simplifies system administration and monitoring.

The choice of validation engine technology dictates not just performance, but also shapes the surrounding infrastructure and required operational expertise.

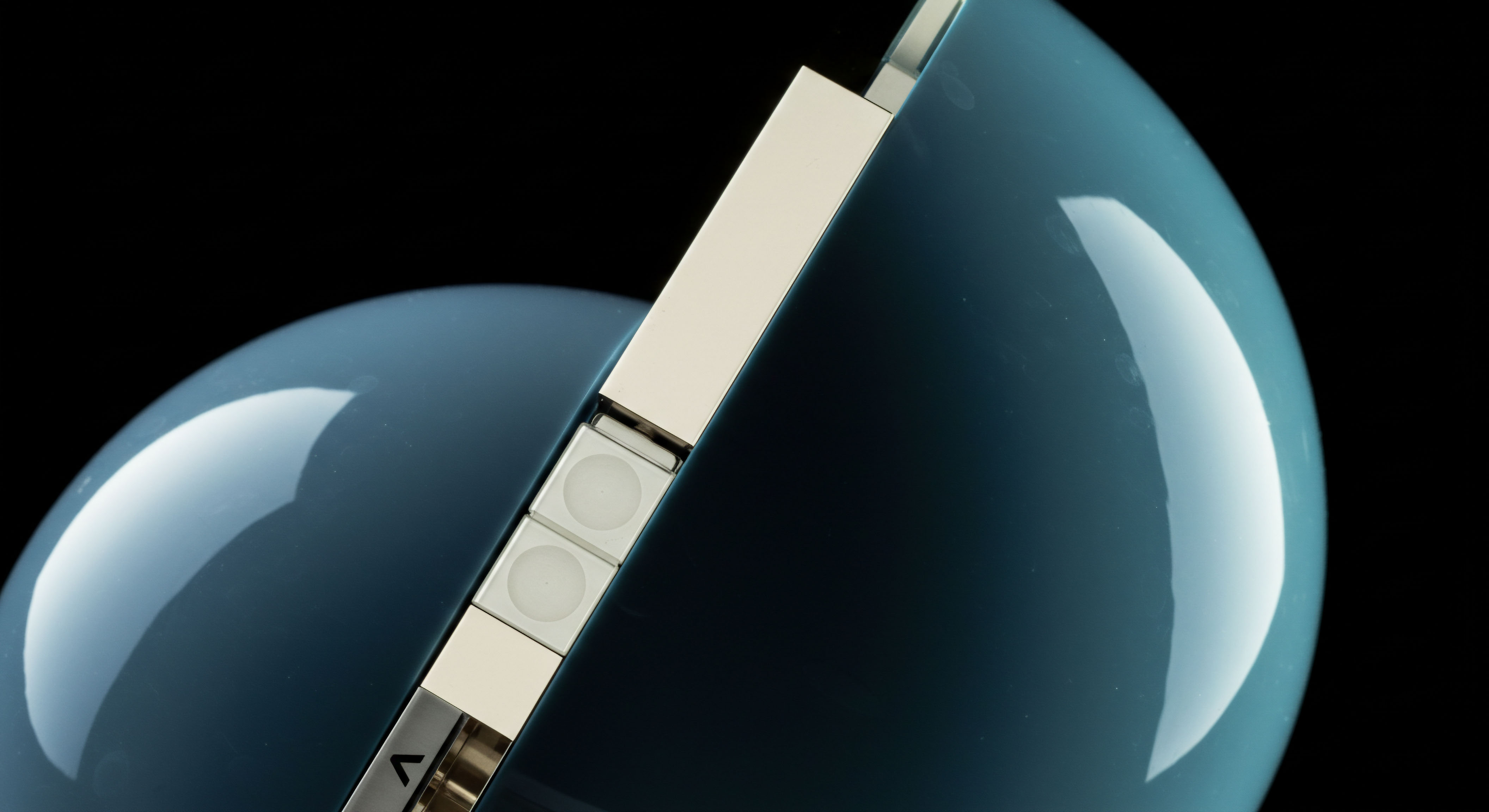

An FPGA-based engine demands a different approach. It is a specialized hardware component, often deployed on a network card or in a dedicated appliance placed physically as close to the exchange’s matching engine as possible. This requires expertise in hardware deployment, network engineering, and an understanding of co-location data center environments. The strategic decision, therefore, extends beyond the engine itself to the very architecture of the firm’s trading plant and the composition of its technology team.

Execution

The Mechanics of Nanosecond Performance

In execution, the differences between FPGA and software manifest as a chasm in performance profiles. A software-based validation engine’s latency is measured in microseconds and is subject to jitter. The operating system’s kernel, network stack, and process scheduler all contribute to unpredictable delays.

For many trading strategies, this level of performance is perfectly adequate. However, for ultra-latency-sensitive applications, this variability is a critical flaw.

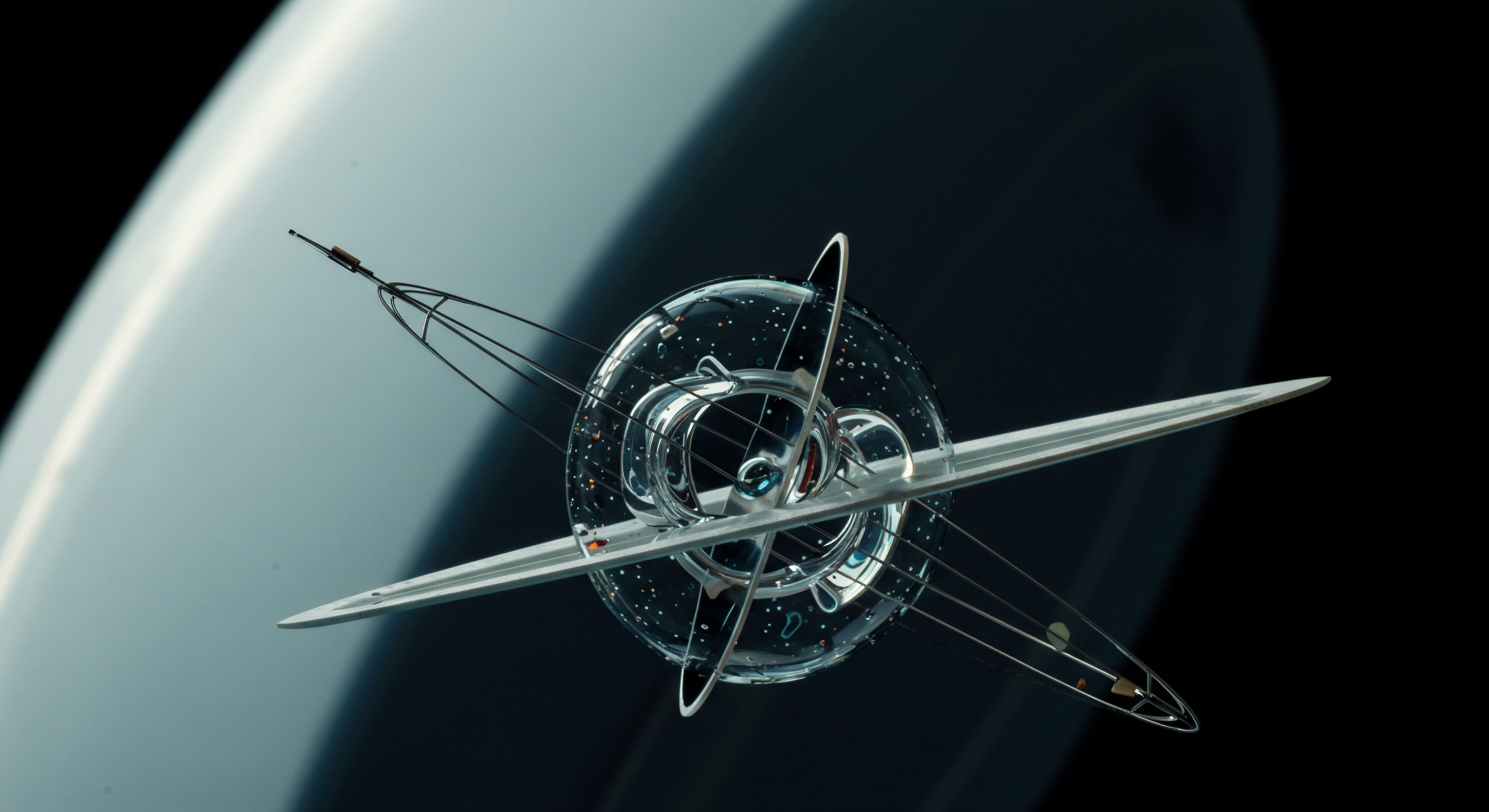

An FPGA engine operates in a different temporal domain. Its latency is measured in nanoseconds and is deterministic. Once a data packet containing a quote hits the network interface of the FPGA, it is processed by the custom circuit without any software or operating system intervention. The path through the logic gates is fixed, and thus the processing time is constant.

Research and industry benchmarks have shown FPGAs outperforming software solutions by factors ranging from 340 to over 750 times for specific financial computations. This performance differential is the execution-level reality that drives the adoption of FPGAs in the most competitive echelons of trading.

At the point of execution, the theoretical differences become a tangible gap in latency, measured in orders of magnitude.

This performance extends to power efficiency. An FPGA configured for a specific task consumes a fraction of the power of a high-end CPU attempting the same task. In large-scale deployments, this translates into substantial savings in data center power and cooling costs, a critical consideration for total cost of ownership. Studies have documented FPGAs being over 5 times more energy-efficient than their software counterparts for financial modeling.

Operational Deployment and Lifecycle

The lifecycle of deploying and maintaining these two types of engines is starkly different. Understanding these workflows is essential for any team tasked with their implementation.

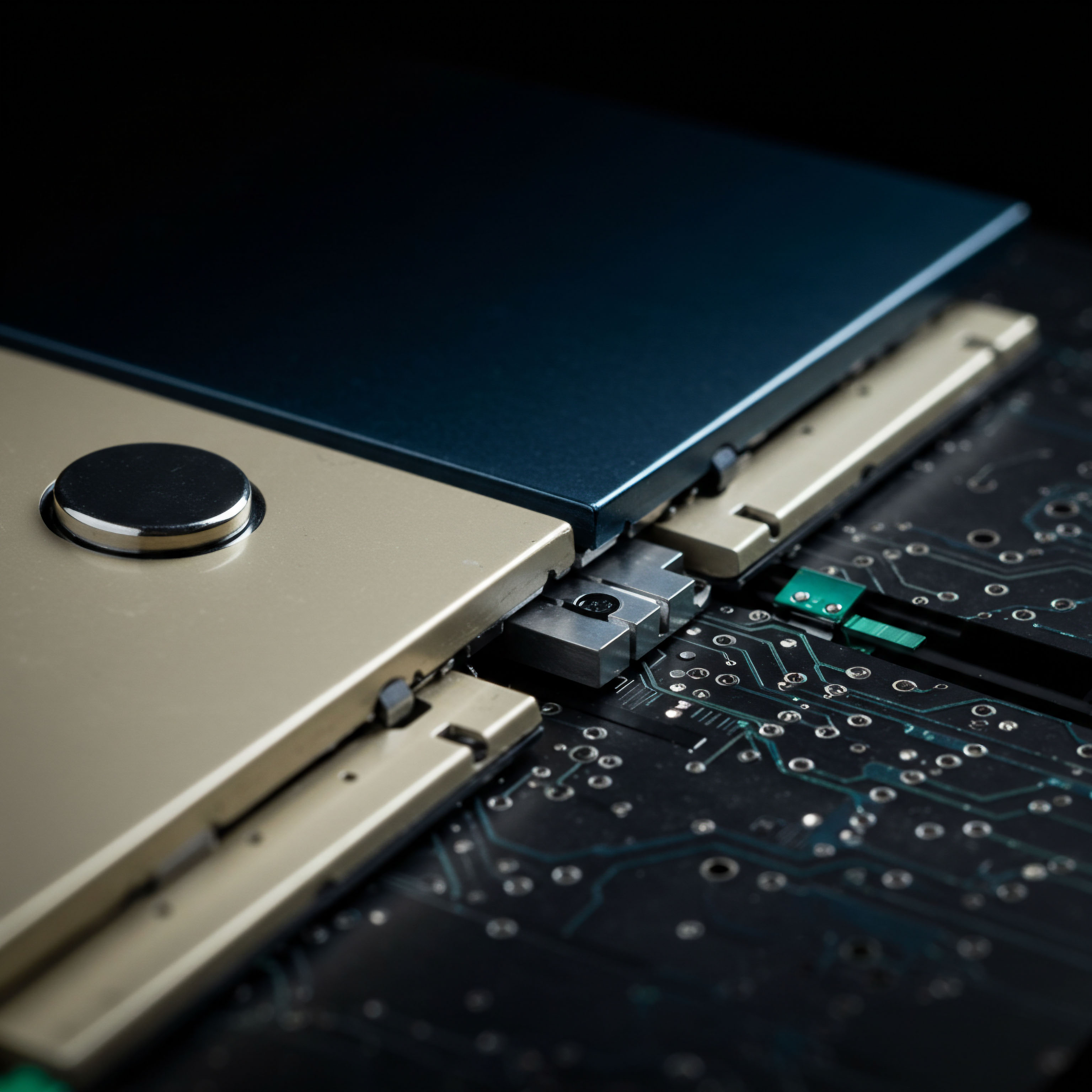

- Software Engine Deployment ▴ This process follows a standard Continuous Integration/Continuous Deployment (CI/CD) pipeline. Code is written in a high-level language like C++, compiled into a binary, and deployed to servers. Rollbacks and updates can be automated and executed within minutes.

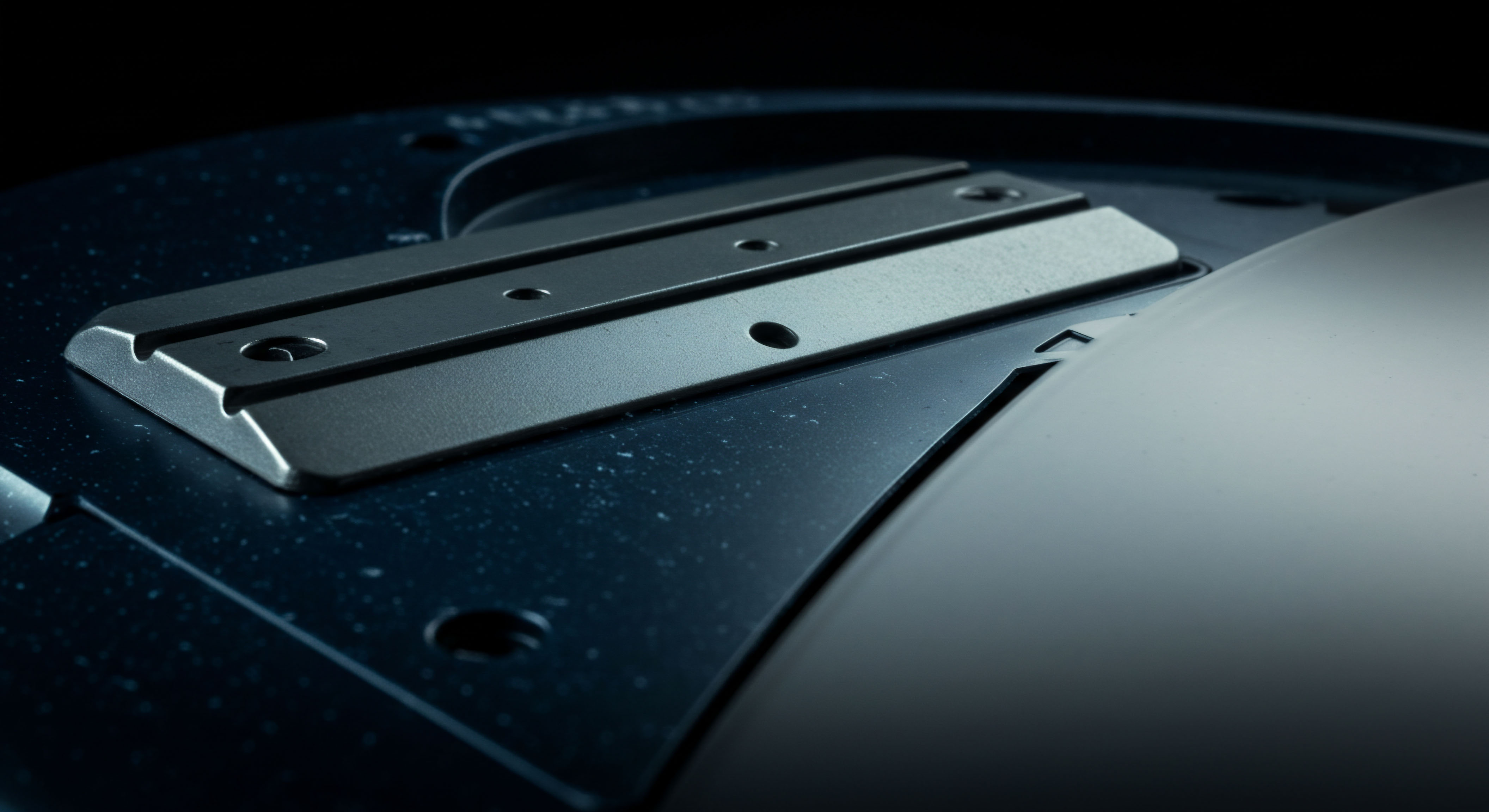

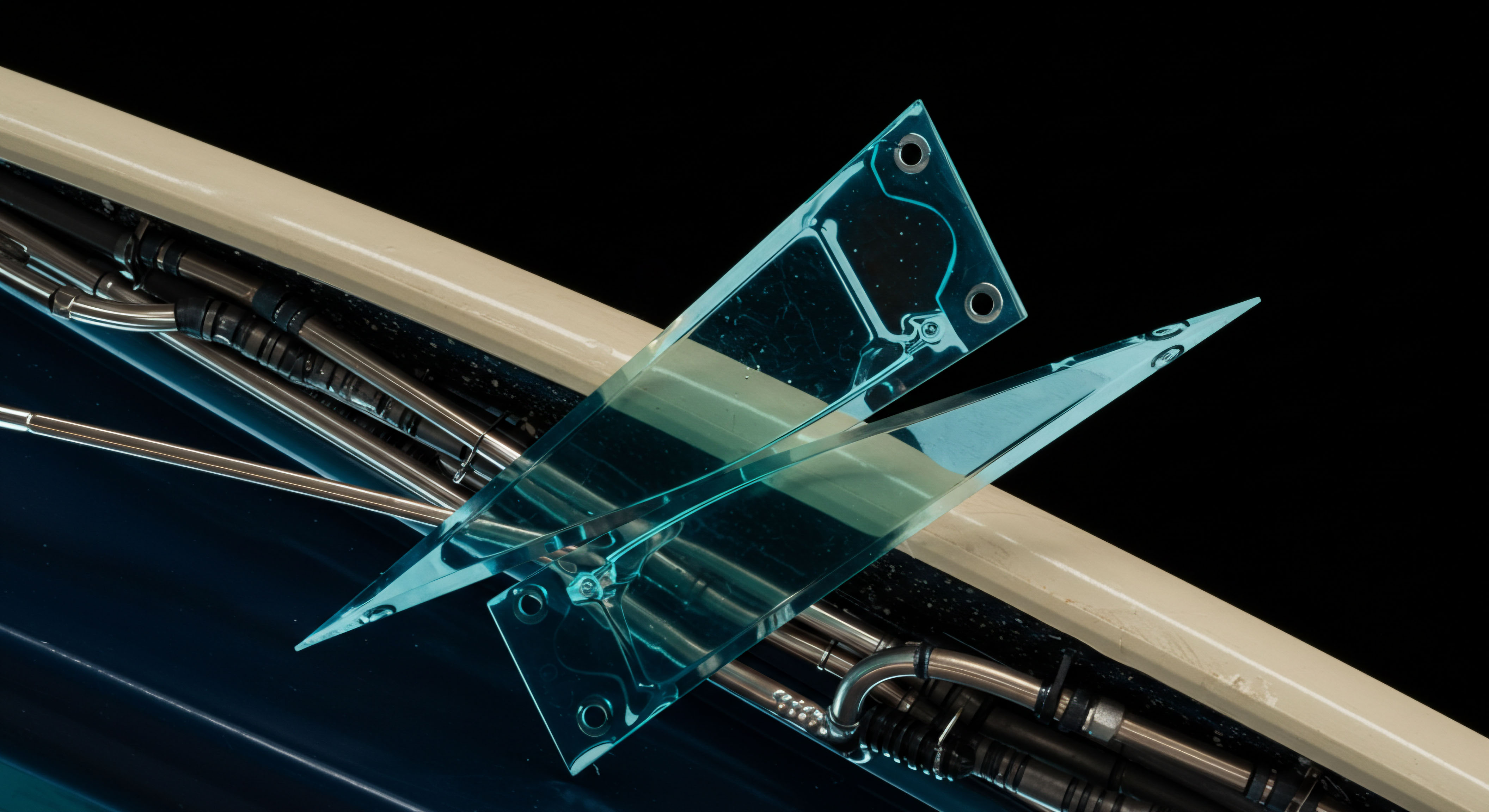

- FPGA Engine Deployment ▴ This workflow is more akin to manufacturing. The logic is designed in a Hardware Description Language (VHDL or Verilog). The design is then put through a “place and route” process, where software tools determine the optimal way to map the logic onto the FPGA’s physical resources. This process can take hours or even days. The resulting “bitfile” is then loaded onto the FPGA chip. Updates are a heavy-lift operation, requiring a full regeneration of the bitfile.

A Tale of Two Timelines

The table below provides a granular view of the execution-level differences that define the operational reality of each technology.

| Operational Metric | Software-Based Engine | FPGA-Based Engine |

|---|---|---|

| Typical Latency | 10-100+ microseconds | 50-500 nanoseconds |

| Latency Profile | Variable (Jitter) | Deterministic (Fixed) |

| Primary Language | C++, Java | VHDL, Verilog |

| Update Cycle | Minutes (Agile) | Hours to Days (Waterfall) |

| Monitoring | Standard OS-level tools (CPU load, memory usage) | Specialized hardware monitoring tools (chip temperature, logic utilization) |

| Primary Failure Mode | Software bug, OS crash, resource contention | Hardware failure, bitfile corruption, thermal issues |

References

- Kouretas, Ioannis, et al. “The Role of FPGAs in Modern Option Pricing Techniques ▴ A Survey.” Applied Sciences, vol. 11, no. 18, 2021, p. 8388.

- Mittal, S. “A survey of techniques for improving the energy efficiency of general-purpose and high-performance processors.” Green Computing and Communications (GreenCom), 2013 IEEE and Internet of Things (iThings/CPSCom), IEEE International Conference on and IEEE Cyber, Physical and Social Computing. IEEE, 2013.

- Wang, Z. & Benkrid, K. “High-performance and low-power FPGA-based option pricing.” 2014 24th International Conference on Field Programmable Logic and Applications (FPL). IEEE, 2014.

- Guo, K. et al. “A survey of FPGA-based accelerators for financial applications.” 2017 IEEE International Symposium on Parallel and Distributed Processing with Applications and 2017 IEEE International Conference on Ubiquitous Computing and Communications (ISPA/IUCC). IEEE, 2017.

- Lachmair, Mathias. “FPGA-based low latency trading ▴ a survey.” 2015 25th International Conference on Field Programmable Logic and Applications (FPL). IEEE, 2015.

Reflection

The Engine as an Expression of Intent

The choice of a quote validation engine is ultimately an expression of a firm’s core identity within the market ecosystem. It reflects a deep-seated philosophy on how to compete and where to allocate finite resources of capital, time, and intellectual talent. A firm that builds its strategy around market intelligence, sophisticated modeling, and operational flexibility will find a powerful ally in a software-based system. Its malleability allows for the rapid iteration of ideas, a critical capability in evolving markets.

A firm that defines its edge through the relentless pursuit of speed and the elimination of uncertainty will inevitably be drawn to the deterministic world of FPGAs. This is a commitment to a different kind of perfection ▴ one of absolute predictability and control at the most granular level. The knowledge of these systems is a component in a larger operational intelligence. The ultimate question is not which technology is superior in isolation, but which system, when integrated into your firm’s unique operational framework, most powerfully amplifies your intended strategic posture in the market.

Glossary

Quote Validation

Fpga

Determinism

Hardware Description Language

Quote Validation Engine

Jitter

Fpga-Based Engine

Validation Engine

Time-To-Market

Verilog