Concept

The Silicon Heart of Market Velocity

In the dissemination of financial quotes, latency is not a passive metric; it is an active arbiter of profit and loss. The physical medium through which a price update travels from exchange to trading engine dictates the boundary of what is possible. At the core of this process lies a fundamental choice in hardware architecture, a decision between two distinct philosophies of computation ▴ the Field-Programmable Gate Array (FPGA) and the Application-Specific Integrated Circuit (ASIC). Understanding this choice requires acknowledging that every nanosecond of delay represents a tangible risk of trading on stale information, a risk that sophisticated market participants systematically seek to eliminate.

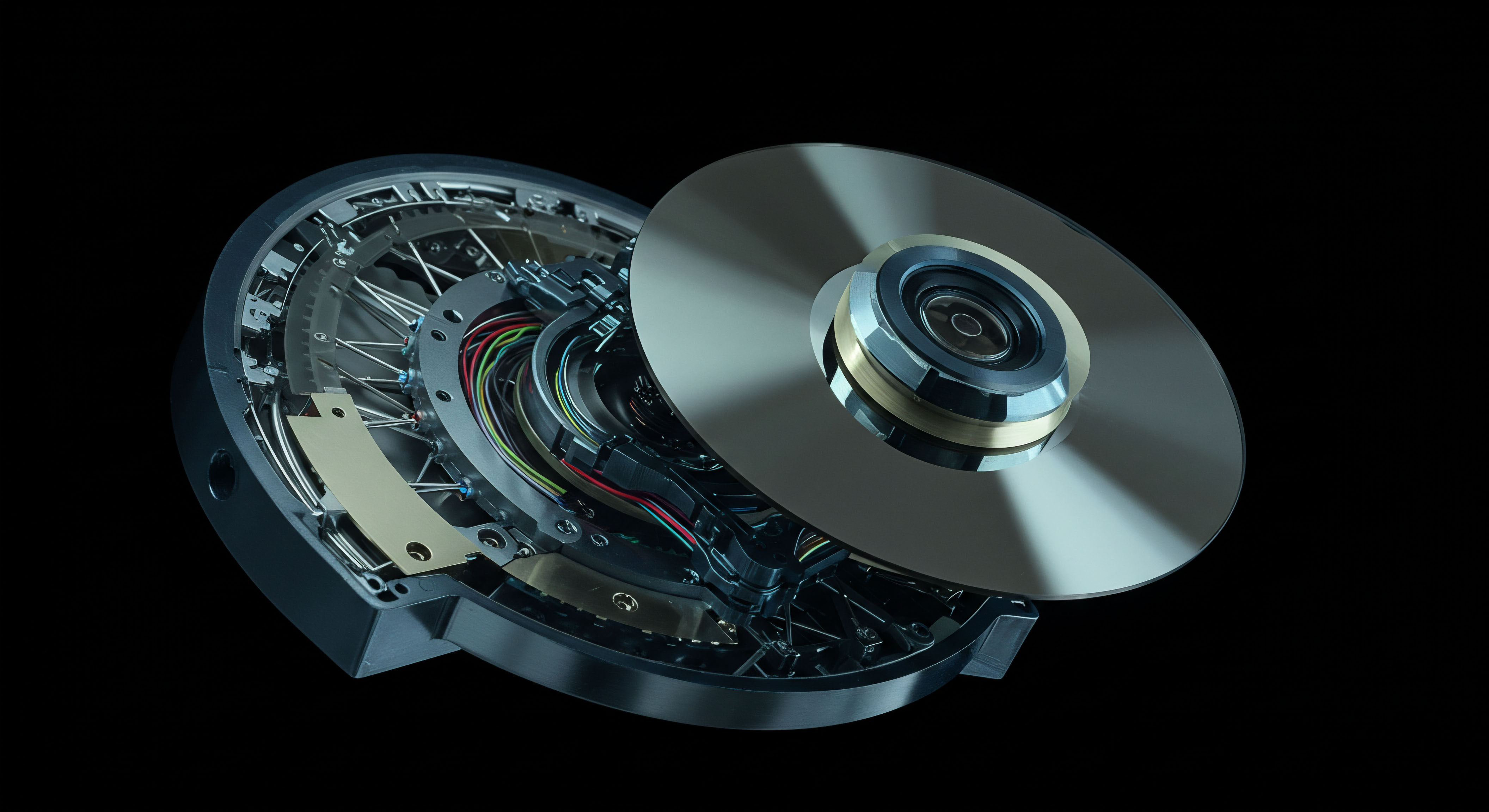

FPGAs represent a paradigm of reconfigurable hardware. They consist of a matrix of configurable logic blocks and programmable interconnects, allowing developers to define and redefine custom digital circuits after manufacturing. For quote dissemination, this means an FPGA can be programmed to perform a specific task, such as parsing a raw market data feed like ITCH or FIX, with extreme efficiency and parallelism, far exceeding the capabilities of a general-purpose CPU.

The logic is physically mapped onto the chip, creating a dedicated data path that executes its function at speeds approaching the physical limits of silicon. The intrinsic value of this technology is its adaptability; as market data protocols evolve or a firm wishes to refine its data handling logic, the FPGA can be reprogrammed in the field with a new “bitstream” file, a process that can be completed in minutes or hours.

The core distinction between FPGAs and ASICs is the trade-off between post-manufacturing flexibility and absolute, singular-purpose optimization.

ASICs, conversely, embody permanence. An Application-Specific Integrated Circuit is a chip custom-designed and fabricated for one exact purpose. Its logic is permanently etched into the silicon during the manufacturing process. This singular focus yields the highest possible performance in terms of speed and power efficiency for that specific task.

An ASIC designed for quote dissemination would contain a circuit optimized exclusively for decoding a particular data feed, filtering relevant symbols, and perhaps even managing an order book in hardware. Once fabricated, it cannot be changed. The development of an ASIC is an intensive and costly undertaking, involving significant non-recurring engineering (NRE) costs and a lengthy design, verification, and manufacturing cycle. The result, however, is a device that performs its designated function with the lowest possible latency and power consumption, establishing the absolute pinnacle of performance for a known, stable task.

Strategy

The Strategic Calculus of Hardware Selection

Choosing between an FPGA and an ASIC for quote dissemination is a profound strategic decision that extends far beyond a simple technical comparison. It reflects a firm’s operational philosophy, its projections on market structure evolution, and its tolerance for different forms of risk. The selection process is an exercise in optimizing a multi-variable equation that balances time-to-market, long-term cost, performance ceilings, and the critical element of adaptability.

Time-to-Market versus Performance Horizon

The temporal dimension is a primary strategic consideration. FPGAs offer a significantly faster path to deployment. A skilled hardware engineering team can develop, test, and deploy a custom feed handler on an FPGA within weeks or months.

This agility allows a firm to react swiftly to new market opportunities, exchange protocol updates, or changes in trading strategy. A firm might utilize FPGAs to be first-to-market with a handler for a new asset class or to experiment with novel data filtering techniques without committing to a permanent hardware design.

ASICs operate on a much longer timescale. The design, verification, tape-out, and fabrication process can span from many months to over a year. This prolonged development cycle introduces a significant risk ▴ the market or technology landscape may shift by the time the chip is ready for deployment.

The strategic justification for an ASIC, therefore, rests on a high degree of confidence in the stability of the target application. It is a commitment made for high-volume, long-duration operations where the upfront investment in time and capital can be amortized through superior performance and lower per-unit costs over an extended period.

Economic Frameworks Total Cost of Ownership

The economic analysis of FPGA versus ASIC is nuanced, hinging on the concept of Total Cost of Ownership (TCO) rather than upfront expense alone. FPGAs present lower initial barriers to entry, with development starting with a relatively modest investment in hardware and software tools. The primary cost is centered on engineering talent. The per-unit cost of high-performance FPGAs, however, is substantial and remains constant regardless of volume.

ASICs invert this cost structure. They demand a formidable upfront investment in Non-Recurring Engineering (NRE) costs, which can easily run into the millions of dollars for design, verification, and mask sets for fabrication. However, the per-unit manufacturing cost of an ASIC is dramatically lower than that of a comparable FPGA. This creates a clear breakeven point; for applications requiring mass deployment across hundreds or thousands of servers, the lower unit cost of ASICs will eventually offset the high initial NRE, resulting in a lower TCO for large-scale, stable deployments.

The strategic choice is an assessment of whether a firm’s competitive advantage lies in rapid adaptation or in achieving ultimate performance at scale.

The table below illustrates a simplified economic model comparing the two approaches for a hypothetical deployment.

| Cost Component | FPGA-Based Solution | ASIC-Based Solution |

|---|---|---|

| Initial Development Cost | Low (Primarily engineering hours) | Very High (NRE, mask sets, fabrication setup) |

| Time-to-Market | Fast (Weeks to Months) | Slow (Months to Years) |

| Per-Unit Hardware Cost | High | Low |

| Flexibility to Adapt | High (Reprogrammable in-field) | None (Function is permanent) |

| Optimal Deployment Scale | Low-to-Medium Volume, Prototyping | High-Volume, Mass Production |

Risk Mitigation and Operational Resilience

The final strategic pillar is risk. The reprogrammability of FPGAs is a powerful risk mitigation tool. If a bug is discovered in the logic or an exchange announces a mandatory protocol change, an FPGA can be updated remotely with a new bitstream. This operational resilience is invaluable in a dynamic market environment.

An ASIC has no such recourse. A flaw in the silicon logic is permanent, potentially requiring a complete and costly re-spin of the chip, rendering the initial investment a total loss. This inflexibility makes ASICs suitable only for protocols and functions that are standardized and have a very low probability of future modification.

Execution

The Engineering Reality of Nanosecond Performance

The execution of a hardware-accelerated quote dissemination system is a discipline of extreme precision. The transition from strategic decision to operational reality involves a rigorous engineering process where every design choice is measured in nanoseconds and gates of logic. The implementation paths for FPGA and ASIC share a common foundation in Hardware Description Languages (HDL) but diverge dramatically in process, complexity, and consequence.

The Implementation Lifecycle a Tale of Two Paths

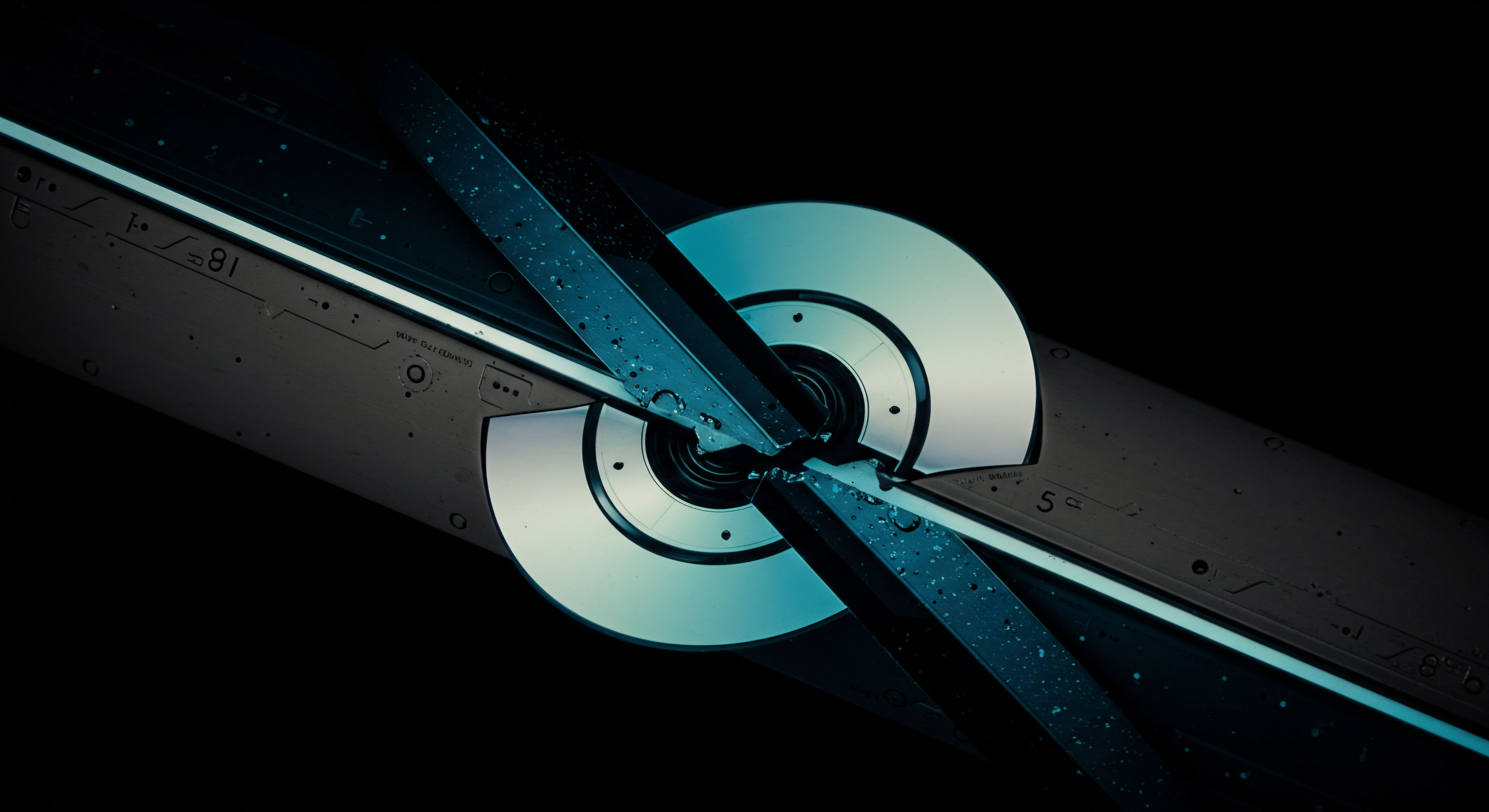

The journey from algorithm to silicon follows a structured, multi-stage process. While both technologies require meticulous design and verification, the ASIC path incorporates a point of no return ▴ the tape-out ▴ which fundamentally alters the nature of the preceding stages.

- System Specification ▴ The process begins with a precise definition of the task. For quote dissemination, this includes specifying the data feed protocol, the filtering criteria for securities of interest, and the output format for the downstream trading logic. For an ASIC, this specification must be flawless and final.

- HDL Development ▴ Engineers write the logic in a language like Verilog or VHDL. This code describes the circuit’s behavior at the register-transfer level (RTL), defining how data flows and is transformed within the chip.

- Functional Verification ▴ This is the most critical and time-consuming phase. The HDL code is subjected to exhaustive simulation. Engineers create complex testbenches that generate millions of possible inputs to uncover any logical flaws. A bug missed at this stage for an ASIC could invalidate the entire project.

- Synthesis ▴ A software tool translates the abstract HDL code into a gate-level netlist, a specific mapping of the logic onto the fundamental building blocks available on the target hardware (logic cells for an FPGA, standard cells for an ASIC).

- Divergence Point ▴

- For FPGAs ▴ The netlist goes through a “place and route” process where software maps the logic onto the FPGA’s physical resources and determines the wiring paths. The output is a bitstream file that is loaded onto the device. This entire process can be completed in a matter of hours.

- For ASICs ▴ The process becomes far more complex, involving physical design, floorplanning, clock tree synthesis, and routing. This stage requires specialized expertise and EDA tools. The final output is a set of design files (GDSII) sent to a semiconductor foundry for fabrication. This is the “tape-out.”

- Deployment ▴ The FPGA is programmed on-site. The fabricated ASIC wafers are returned from the foundry, tested, packaged, and then integrated into the system.

Quantitative Modeling Performance and Cost

The performance difference between the two technologies is not abstract; it is quantifiable in latency and power. An ASIC’s custom design allows for optimizations impossible in the more generalized structure of an FPGA. Signal paths are shorter, clock speeds can be higher, and every transistor serves the primary function.

The following table provides a hypothetical, yet realistic, latency breakdown for a market data feed handler processing a single message, illustrating the performance differential.

| Processing Stage | High-Performance FPGA | Custom ASIC | Performance Delta |

|---|---|---|---|

| Packet Reception (PHY to MAC) | 35 ns | 20 ns | -15 ns |

| Protocol Parsing & Header Decode | 50 ns | 30 ns | -20 ns |

| Message Filtering & Symbol Match | 25 ns | 15 ns | -10 ns |

| Order Book Logic Update | 40 ns | 25 ns | -15 ns |

| Total Message-In to Signal-Out | 150 ns | 90 ns | -60 ns |

This 60-nanosecond advantage, while seemingly infinitesimal, is a significant competitive edge in many high-frequency trading strategies. The execution decision thus becomes a quantitative exercise ▴ a firm must model the potential alpha generation from this latency improvement against the immense NRE and inflexibility risk of the ASIC development path. The choice is a direct reflection of the firm’s confidence in its predictive models regarding both market behavior and technological stability.

References

- Guo, K. et al. “A Survey of FPGA-Based Neural Network Accelerators.” ACM Transactions on Reconfigurable Technology and Systems (TRETS), vol. 12, no. 1, 2019, pp. 1-29.

- Kuon, I. and Rose, J. “Measuring the Gap Between FPGAs and ASICs.” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 26, no. 2, 2007, pp. 203-215.

- Hauck, S. and DeHon, A. “Reconfigurable Computing ▴ The Theory and Practice of FPGA-Based Computation.” Morgan Kaufmann, 2008.

- Lettau, M. and Uhlig, S. “Market Microstructure ▴ The Econometrics of Financial Markets.” Cambridge University Press, 2009.

- Compton, K. and Hauck, S. “Reconfigurable Computing ▴ A Survey of Systems and Software.” ACM Computing Surveys (CSUR), vol. 34, no. 2, 2002, pp. 171-210.

Reflection

The Architecture of Advantage

The decision between programmable and application-specific silicon is ultimately an inquiry into the nature of a firm’s competitive edge. It compels an organization to define its core competencies and its vision for the future of market interaction. Is advantage found in the ability to rapidly adapt to an ever-changing landscape, deploying novel logic with unmatched agility? Or does it lie in the relentless pursuit of perfection for a single, well-understood function, shaving the final nanoseconds of latency to achieve an immutable state of peak performance?

The choice of hardware is a physical manifestation of this strategic identity. The optimal system is not merely the fastest or the most flexible, but the one that creates the most coherent alignment between a firm’s trading philosophy and the silicon that executes it.

Glossary

Asic

Fpga

Quote Dissemination

Time-To-Market

Hdl

Verilog