Concept

The Physical Substrate of Speed

In the domain of ultra-low-latency trading, the contest for alpha is won or lost on the physical plane. The system is a direct reflection of the physical laws governing the transmission of information, where every inch of fiber and every clock cycle of a processor contributes to the temporal signature of a trade. The primary hardware components are consequently selected and engineered with a singular focus on minimizing the time elapsed between market data receipt and order dispatch.

This interval, the tick-to-trade latency, is the fundamental metric of performance. The architecture is therefore an exercise in applied physics, a meticulously constructed apparatus designed to operate at the very edge of what is technologically possible.

The core principle is the radical reduction of intermediation. Every layer of abstraction, be it in software or hardware, introduces a delay. An operating system kernel, a general-purpose CPU instruction set, or a standard network protocol stack ▴ each represents a temporal liability. The solution is to move critical functions from the mutable world of software into the deterministic realm of silicon.

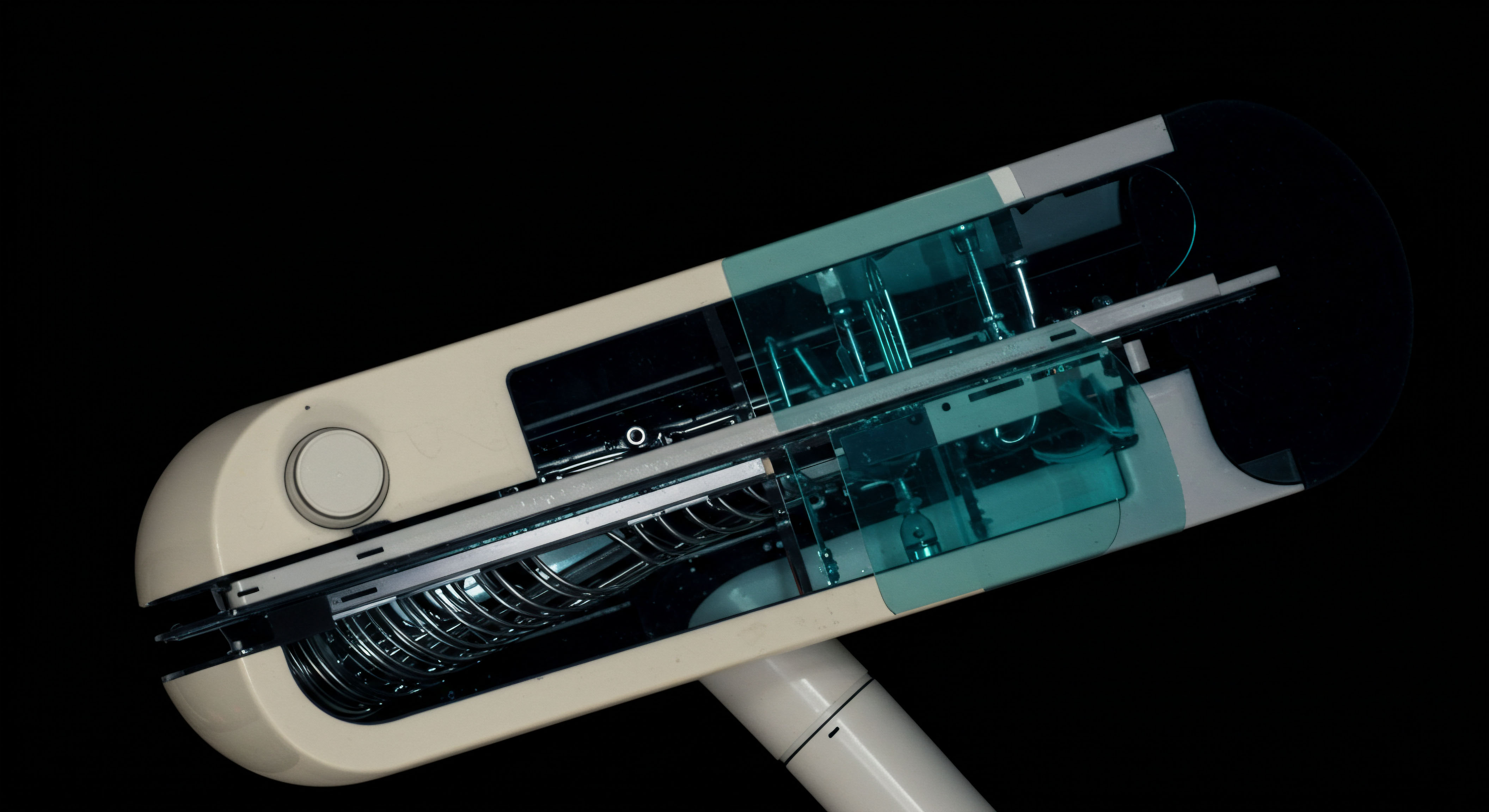

This migration is the defining characteristic of a low-latency system. Field-Programmable Gate Arrays (FPGAs), for instance, are not merely accelerators; they are the embodiment of trading logic fused directly into hardware circuits, bypassing the sequential, interrupt-driven nature of traditional computing. This allows for a parallel, instantaneous response to market stimuli that a CPU-based system cannot replicate. The result is a trading apparatus where the speed of light in fiber and the propagation delay in silicon are the primary constraints.

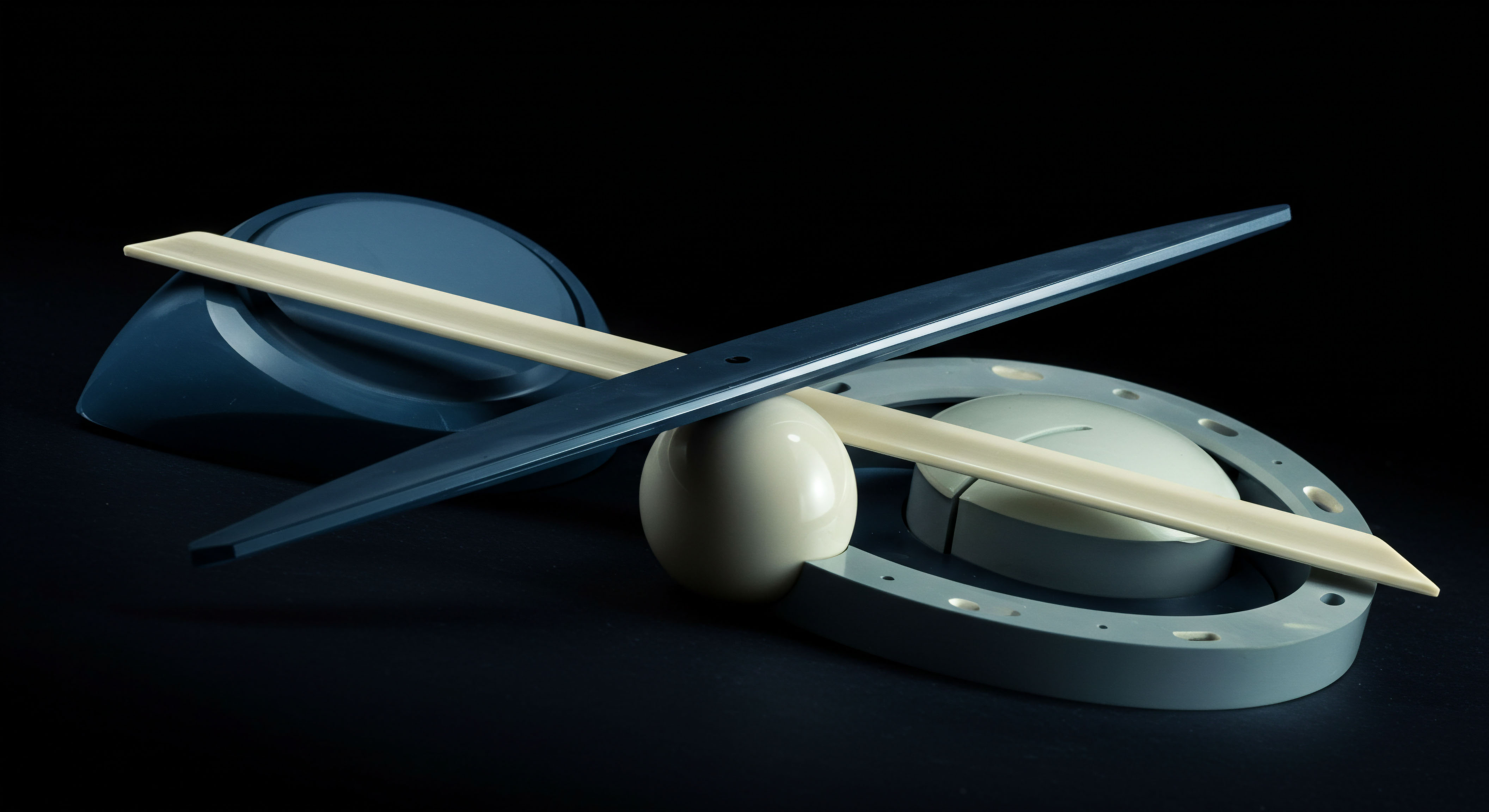

The entire hardware stack is engineered to function as a single, cohesive unit, where each component is a specialized instrument for minimizing time.

This pursuit extends beyond the server rack to the very fabric of the network. The network is not a passive conduit for data but an active component of the trading engine. Specialized network interface cards (NICs) with kernel bypass capabilities allow market data to be delivered directly to the application’s memory space, circumventing the latency-inducing journey through the operating system’s networking stack. Layer 1 switches, which operate at the physical layer of the network, direct traffic based on electrical signals rather than packet inspection, reducing switching latency to mere nanoseconds.

The system’s temporal integrity is maintained by a PTP Grandmaster clock, synchronized to a global time standard, ensuring that every component operates on a unified, nanosecond-precise timeline. This holistic approach, from the atomic clock to the FPGA logic gate, is the essence of a modern ultra-low-latency trading system.

Strategy

Component Selection as a Strategic Imperative

The assembly of an ultra-low-latency trading system is a strategic exercise in which component selection dictates the boundaries of achievable performance. Each piece of hardware is chosen not in isolation, but for its synergistic contribution to the end-to-end latency budget. The overarching strategy is to construct a deterministic data path from the exchange’s matching engine to the firm’s trading logic and back, with every component optimized for minimal, predictable delay. This requires a deep understanding of the trade-offs between processing power, network throughput, and raw speed.

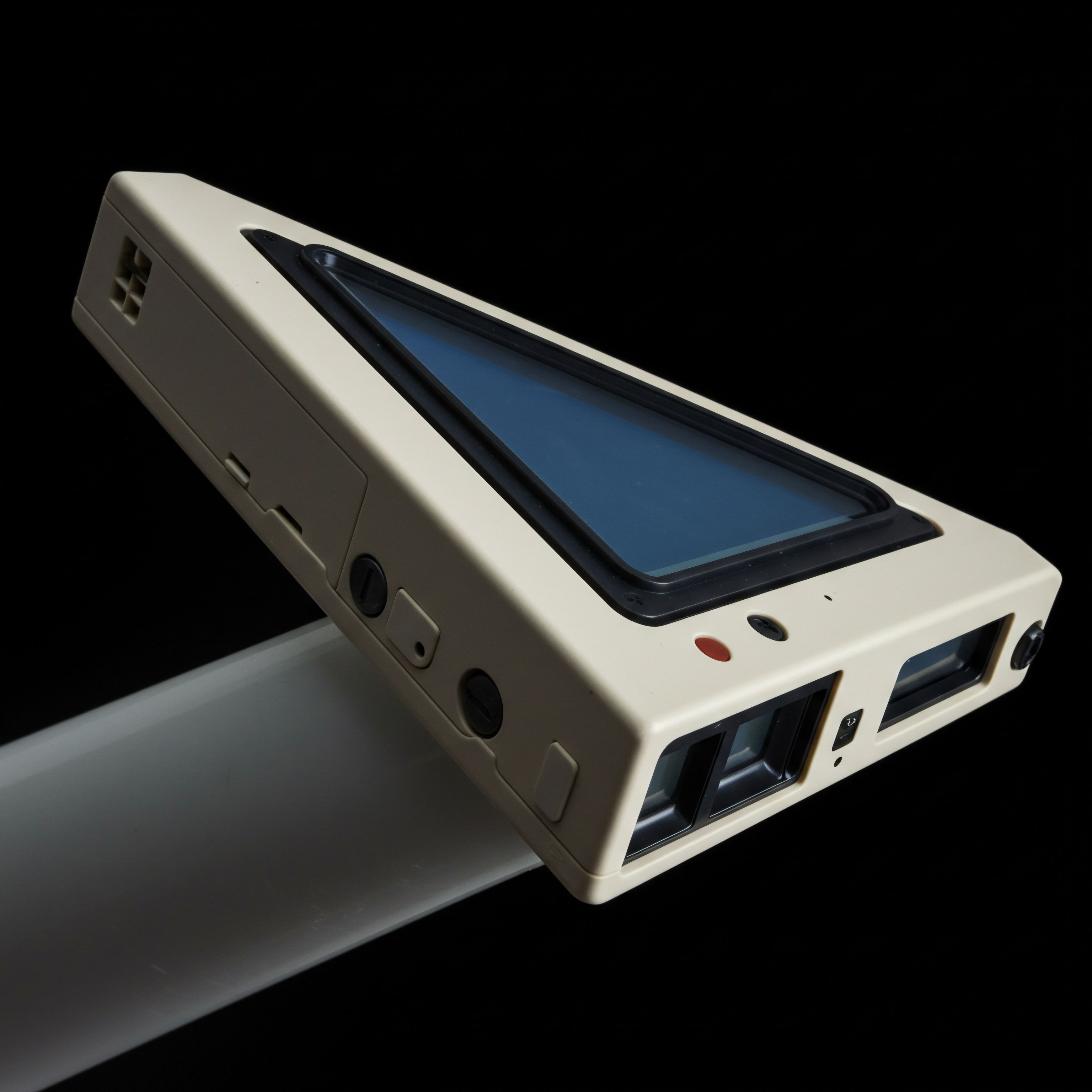

The Processing Core High-Clock-Speed CPUs and FPGAs

At the heart of the system lies the processing core, a hybrid environment where general-purpose CPUs and specialized FPGAs perform distinct, complementary roles. The choice of CPU prioritizes high clock frequency and large cache sizes over a high number of cores. This is because many trading algorithms are single-threaded, and their performance is dictated by the speed at which a single core can execute instructions. The CPU is tasked with higher-level strategy management, risk checks, and monitoring functions that are less latency-sensitive.

The most time-critical tasks, however, are offloaded to FPGAs. These devices are programmed to perform specific functions ▴ such as market data decoding, filtering, and order book building ▴ directly in hardware. This results in deterministic, nanosecond-level processing that is impossible to achieve with a CPU.

The strategic decision is which functions to implement on the FPGA. A common approach is a “tick-to-trade” loop where the FPGA handles the entire critical path from receiving a market data packet to sending an order, with the CPU only providing high-level parameters.

- High-Frequency CPUs ▴ Processors like the Intel Core i9 or AMD Ryzen series, often overclocked, are favored for their high single-core clock speeds, which are critical for the sequential parts of the trading logic.

- Field-Programmable Gate Arrays (FPGAs) ▴ These are the cornerstone of ultra-low latency, handling tasks like market data feed processing and risk checks directly in hardware circuits, bypassing the CPU and operating system entirely.

- High-Speed RAM ▴ DDR5 memory is utilized for its high bandwidth and low latency, ensuring the CPU is not bottlenecked when accessing data.

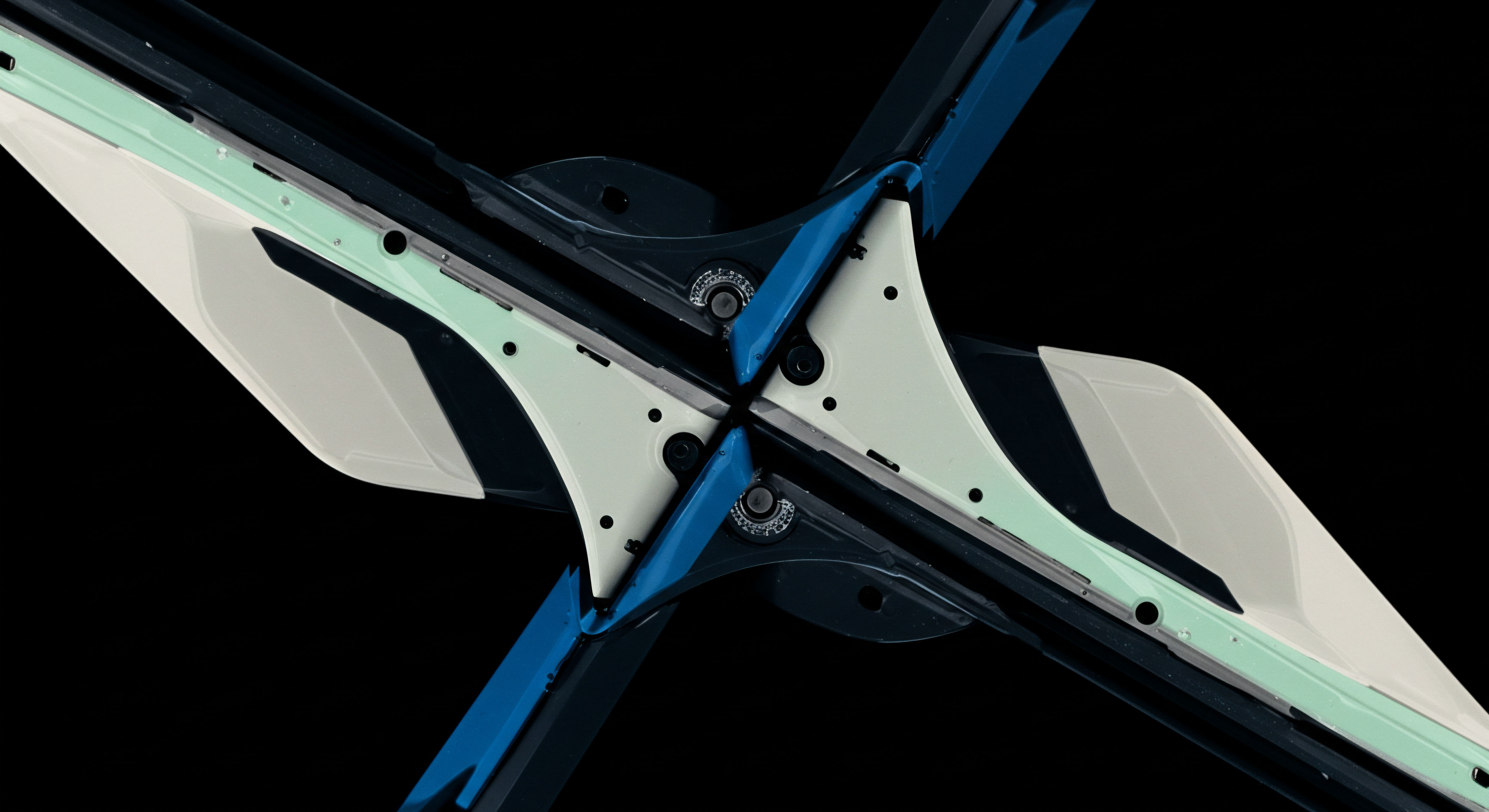

The Network Fabric Specialized NICs and Switches

The network fabric is designed to be an extension of the processing core, a transparent medium for data transfer. This is achieved through a combination of specialized Network Interface Cards (NICs) and ultra-low-latency switches.

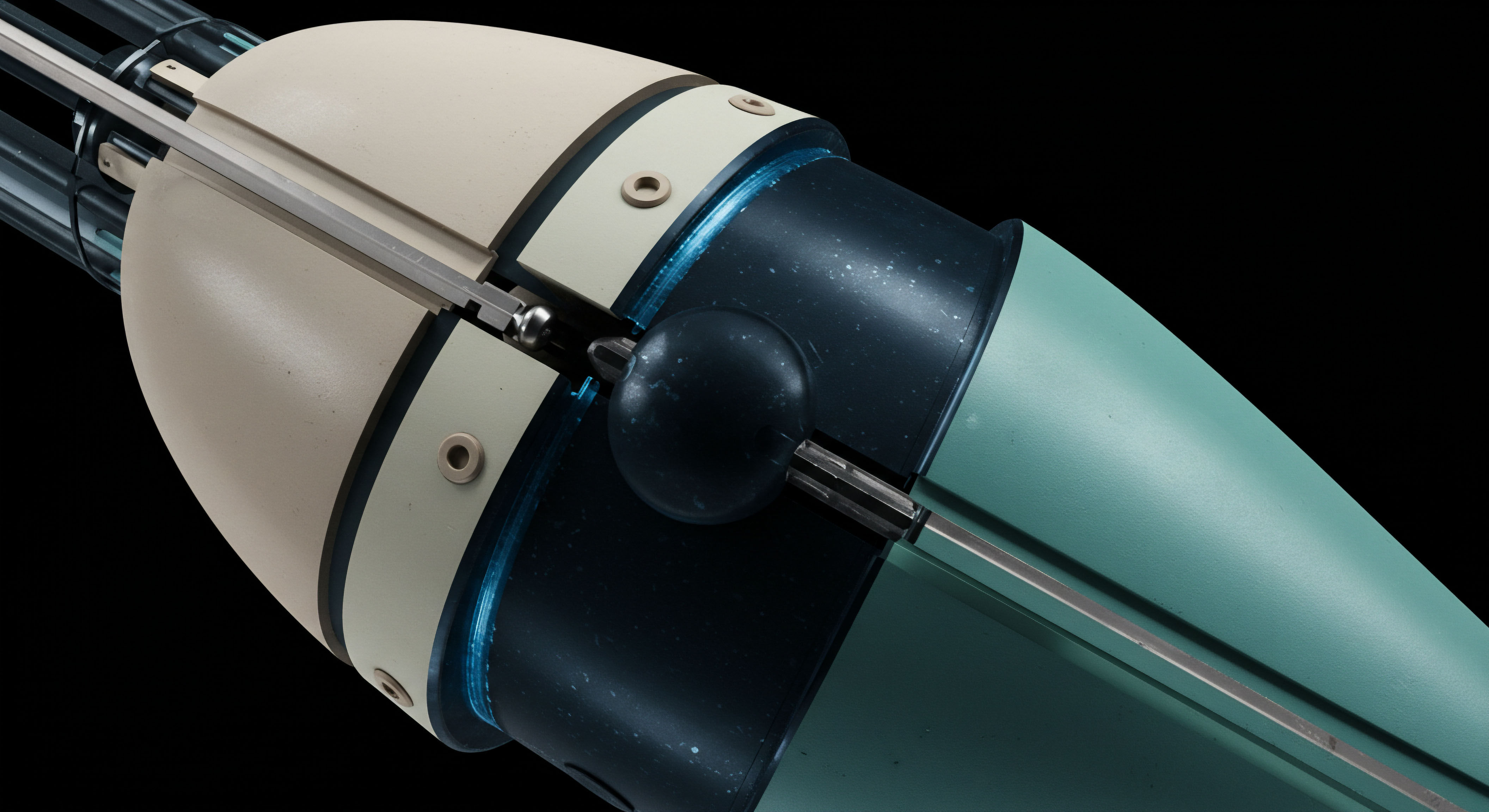

The NICs are the gateway to the network, and their primary function is to deliver data to the application with minimal delay. This is accomplished through kernel bypass technologies, which allow the application to communicate directly with the NIC’s hardware buffers, avoiding the overhead of the operating system’s network stack. This technique can reduce latency by orders of magnitude compared to standard networking.

The switches that connect the trading servers to the exchange must be selected for their port-to-port latency. Layer 1 switches are often used as they operate at the physical layer, essentially creating a direct electrical connection between ports. This can reduce latency to as little as a few nanoseconds per hop. For more complex routing, Layer 2/3 switches with cut-through forwarding are used, which begin forwarding a packet as soon as the destination address is read, without waiting for the entire packet to be received.

| Component | Typical Latency | Key Technology |

|---|---|---|

| Standard NIC with Kernel Stack | 10-100 microseconds | TCP/IP Stack in OS |

| Specialized NIC with Kernel Bypass | Sub-microsecond | Direct Memory Access (DMA), Userspace Networking |

| Layer 2/3 Store-and-Forward Switch | 5-20 microseconds | Packet Buffering |

| Layer 2/3 Cut-Through Switch | Sub-microsecond | Immediate Forwarding |

| Layer 1 Switch | 4-100 nanoseconds | Physical Layer Signal Regeneration |

Execution

The Operational Playbook for Nanosecond Precision

Executing a strategy for ultra-low-latency trading requires a granular, disciplined approach to hardware deployment and configuration. The theoretical advantages of specialized components are only realized through meticulous integration and optimization within the data center environment. This operational playbook outlines the critical steps and considerations for building a hardware infrastructure capable of competing at the nanosecond level.

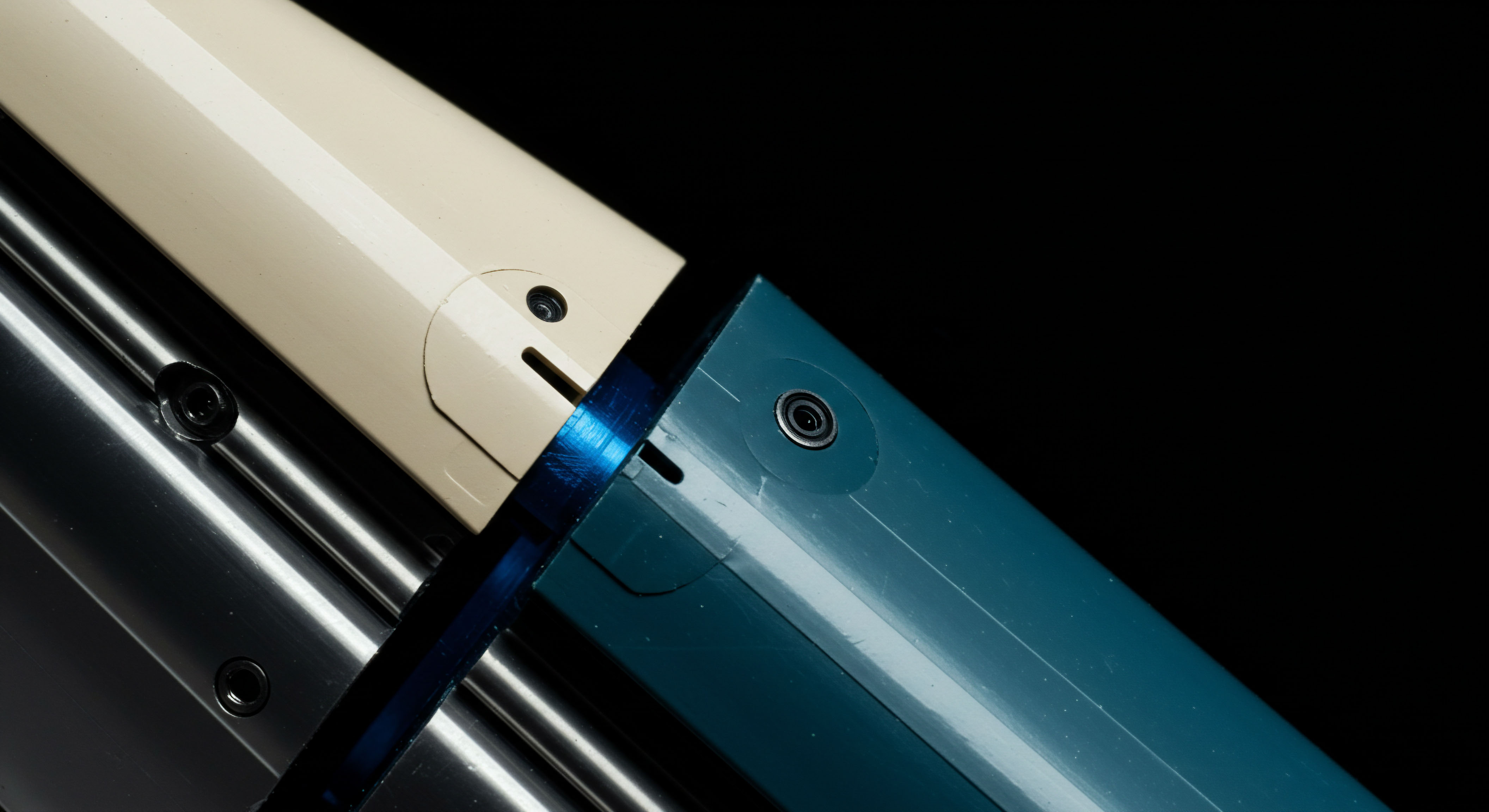

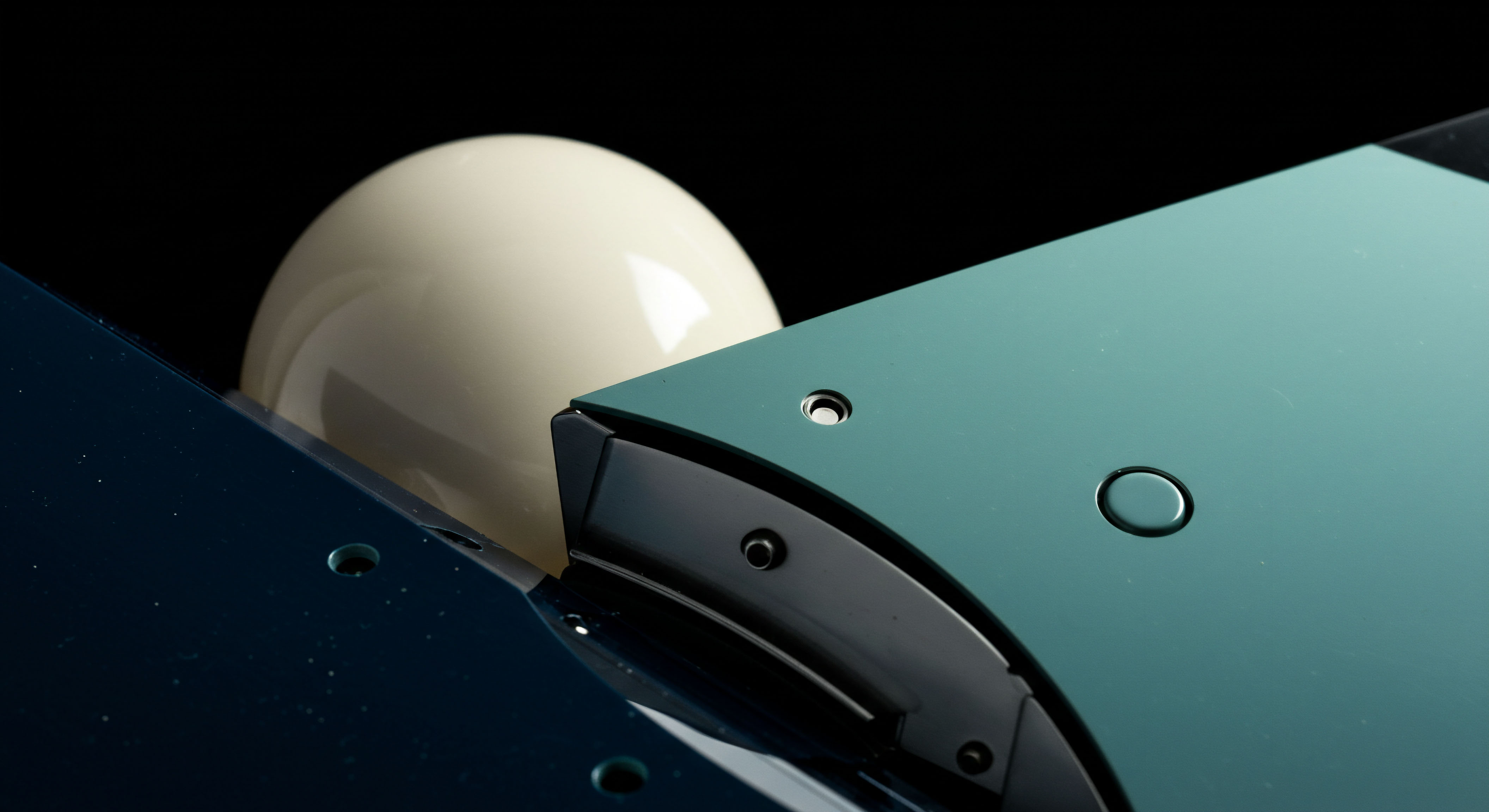

Physical Proximity and Interconnection

The foundational element of any low-latency strategy is co-location. The trading servers must be physically housed in the same data center as the exchange’s matching engine. This minimizes the physical distance data must travel, which, governed by the speed of light in fiber optic cable, is an immutable source of latency.

The goal is to secure the shortest possible fiber path from the firm’s server rack to the exchange’s. Within the rack, components are interconnected with the shortest possible, high-quality cables to minimize signal degradation and delay.

- Co-location ▴ Secure rack space in the primary data center of the target exchange. This is the single most important step in reducing network latency.

- Direct Market Access (DMA) ▴ Establish the fastest possible connectivity to the exchange’s data feeds and order entry gateways. This often involves using dedicated fiber cross-connects.

- Inter-Data Center Links ▴ For strategies that involve trading across multiple exchanges, microwave or millimeter-wave networks are often used for inter-data center communication, as signals travel faster through the air than through fiber.

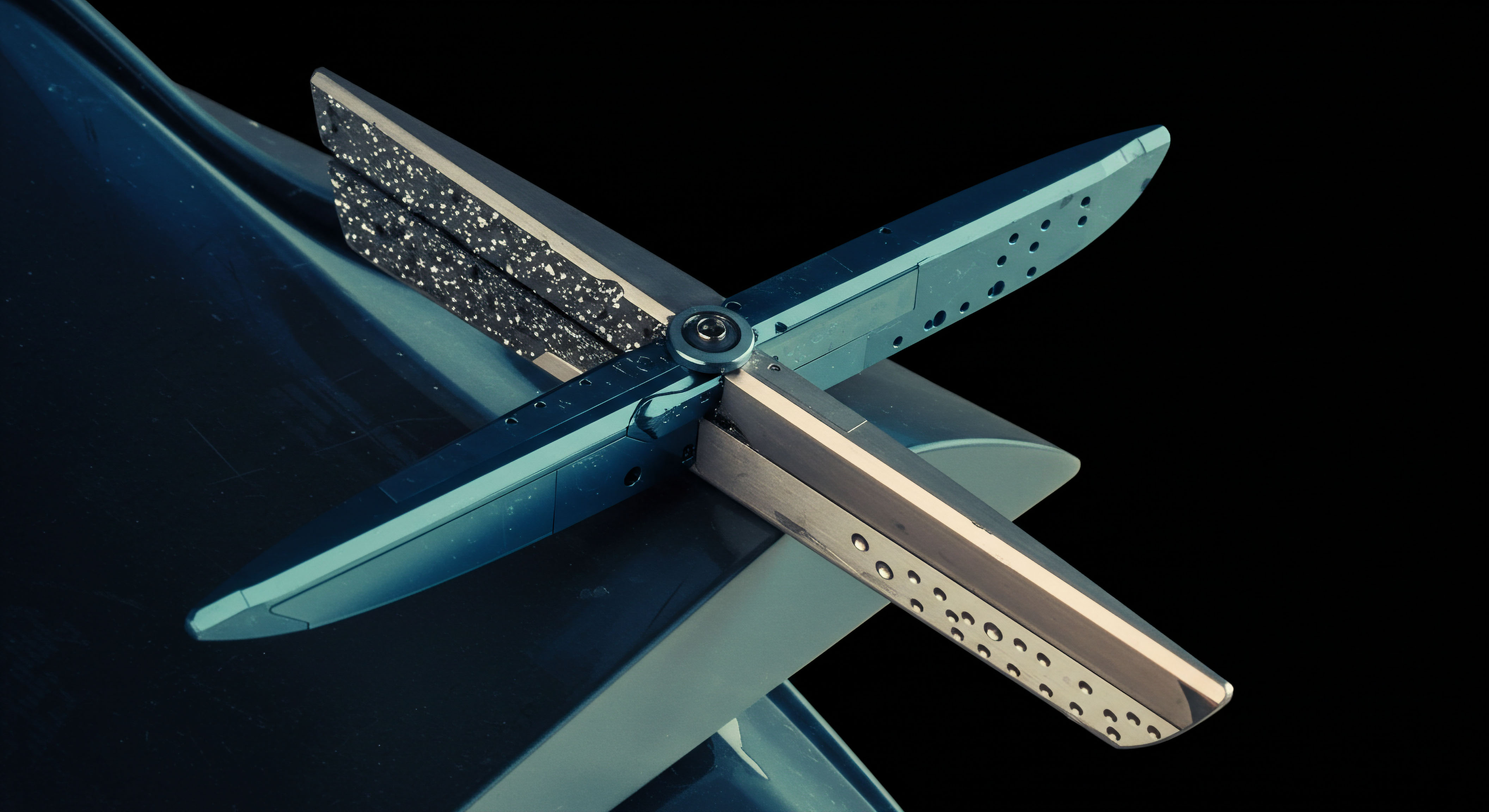

System-Level Optimization and Time Synchronization

Once the physical infrastructure is in place, the focus shifts to system-level optimization. This involves tuning the hardware and software to work in concert, eliminating any sources of non-deterministic latency. A critical aspect of this is time synchronization.

All components in the trading system must share a common, highly precise sense of time. This is essential for accurately timestamping market data and orders, as required by regulations like MiFID II, and for ensuring the correct sequence of operations within the trading logic.

The Precision Time Protocol (PTP) is the standard for achieving this level of synchronization. A PTP Grandmaster clock, often synchronized to GPS satellites, serves as the authoritative time source for the entire network. Specialized network switches and NICs with PTP support ensure that this time is distributed with nanosecond accuracy.

Without a unified, high-precision time source, the sequential integrity of market events and trading actions is lost.

| Component Category | Specific Hardware | Primary Function | Latency Impact |

|---|---|---|---|

| Processing | High-Clock-Speed CPU (e.g. overclocked Intel i9) | Runs main trading application, risk management | Reduces single-thread execution time |

| FPGA (e.g. Xilinx Alveo) | Market data parsing, order book building, tick-to-trade logic | Moves processing from software to hardware, enabling nanosecond execution | |

| Networking | Low-Latency NIC (e.g. Solarflare/Xilinx X2 series) | Provides network connectivity with kernel bypass | Eliminates OS network stack latency (microseconds to nanoseconds) |

| Layer 1 Switch (e.g. Arista 7130 Series) | Directs network traffic at the physical layer | Reduces hop latency to a few nanoseconds | |

| Timing | PTP Grandmaster Clock | Provides a network-wide, high-precision time reference | Enables accurate timestamping and event sequencing to nanosecond precision |

| Storage | NVMe SSD (e.g. Samsung 990 Pro) | Stores operating system, trading logs, and market data for analysis | Minimizes I/O latency for system boot and data logging |

The final stage of execution involves the continuous monitoring and optimization of the system. Performance is measured in nanoseconds, and any change in the system, no matter how small, can have a significant impact on latency. This requires a dedicated team of engineers who can analyze performance data, identify bottlenecks, and fine-tune the system to maintain a competitive edge.

References

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- Lehalle, Charles-Albert, and Sophie Laruelle. Market Microstructure in Practice. World Scientific Publishing, 2013.

- Chaboud, Alain P. et al. “Rise of the Machines ▴ Algorithmic Trading in the Foreign Exchange Market.” The Journal of Finance, vol. 69, no. 5, 2014, pp. 2045-2084.

- Budish, Eric, et al. “The High-Frequency Trading Arms Race ▴ Frequent Batch Auctions as a Market Design Response.” The Quarterly Journal of Economics, vol. 130, no. 4, 2015, pp. 1547-1621.

- “MiFID II ▴ Markets in Financial Instruments Directive II.” European Securities and Markets Authority, 2014.

Reflection

The Continuous Pursuit of Instantaneity

The assembly of these hardware components represents the current state of the art in the relentless pursuit of lower latency. Yet, this is not a static endpoint. It is a continuous process of refinement and innovation, where today’s competitive advantage becomes tomorrow’s baseline. The knowledge of these components is foundational, but the true strategic insight lies in understanding their interplay as a cohesive system.

As you evaluate your own operational framework, consider how each element contributes to the whole. Where are the sources of non-determinism? How can the path from data to decision be further shortened? The answers to these questions will define the next generation of trading systems, pushing ever closer to the absolute limit of instantaneous execution.

Glossary

Ultra-Low-Latency Trading

Market Data

Tick-To-Trade

Trading Logic

Specialized Network Interface Cards

Physical Layer

Ptp Grandmaster

Fpga

Kernel Bypass

Co-Location

Direct Market Access