Concept

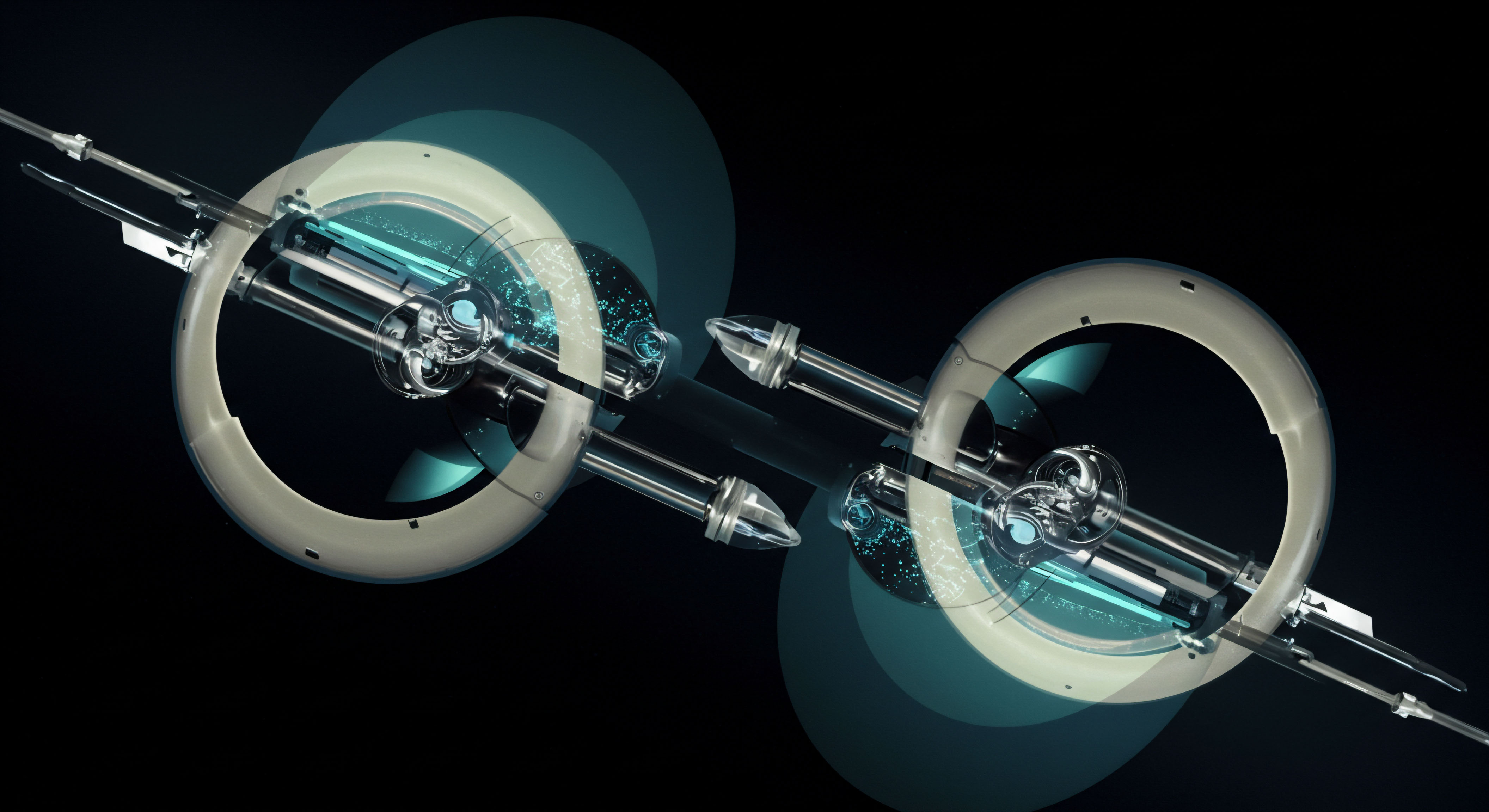

The operational velocity of a High-Frequency Trading (HFT) system is the primary determinant of its viability. The core challenge is one of physics and information theory, applied within the unforgiving domain of modern capital markets. When an order is conceived, it begins a journey measured in microseconds and nanoseconds, a race against a thousand identical competitors where the difference between profit and loss is often determined by who arrives at the exchange’s matching engine first. Understanding the primary sources of latency in a Financial Information Exchange (FIX) based HFT system requires a systemic perspective, viewing the entire trading apparatus as a single, integrated machine designed for one purpose ▴ the timely execution of a trading decision.

Latency is the temporal cost of traversing this system. It is the aggregate of delays encountered at every stage of the order lifecycle, from the initial processing of market data to the final confirmation of an executed trade. We must dissect this journey with the precision of a clockmaker, identifying every gear, every circuit, and every line of code that contributes to this temporal cost. The FIX protocol itself, while a global standard for electronic trading communication, represents a specific set of trade-offs in this high-stakes environment.

Its text-based, tag-value pair structure offers interoperability and human readability, yet it introduces a computational overhead that is a direct source of latency. The system must parse these messages, a process that consumes critical CPU cycles. Therefore, an analysis of latency begins with the protocol but extends far beyond it, into the very architecture of the network, the silicon of the processors, and the logic of the trading algorithms themselves.

Deconstructing the Latency Chain

To architect a system for minimal latency, one must first map the entire path of information flow. This path can be segmented into three fundamental domains where latency is introduced. Each domain presents its own set of challenges and requires a distinct set of solutions.

The total latency of a trade is the sum of the time spent in each of these domains. A successful HFT firm is one that has systematically identified and optimized every single component within this chain.

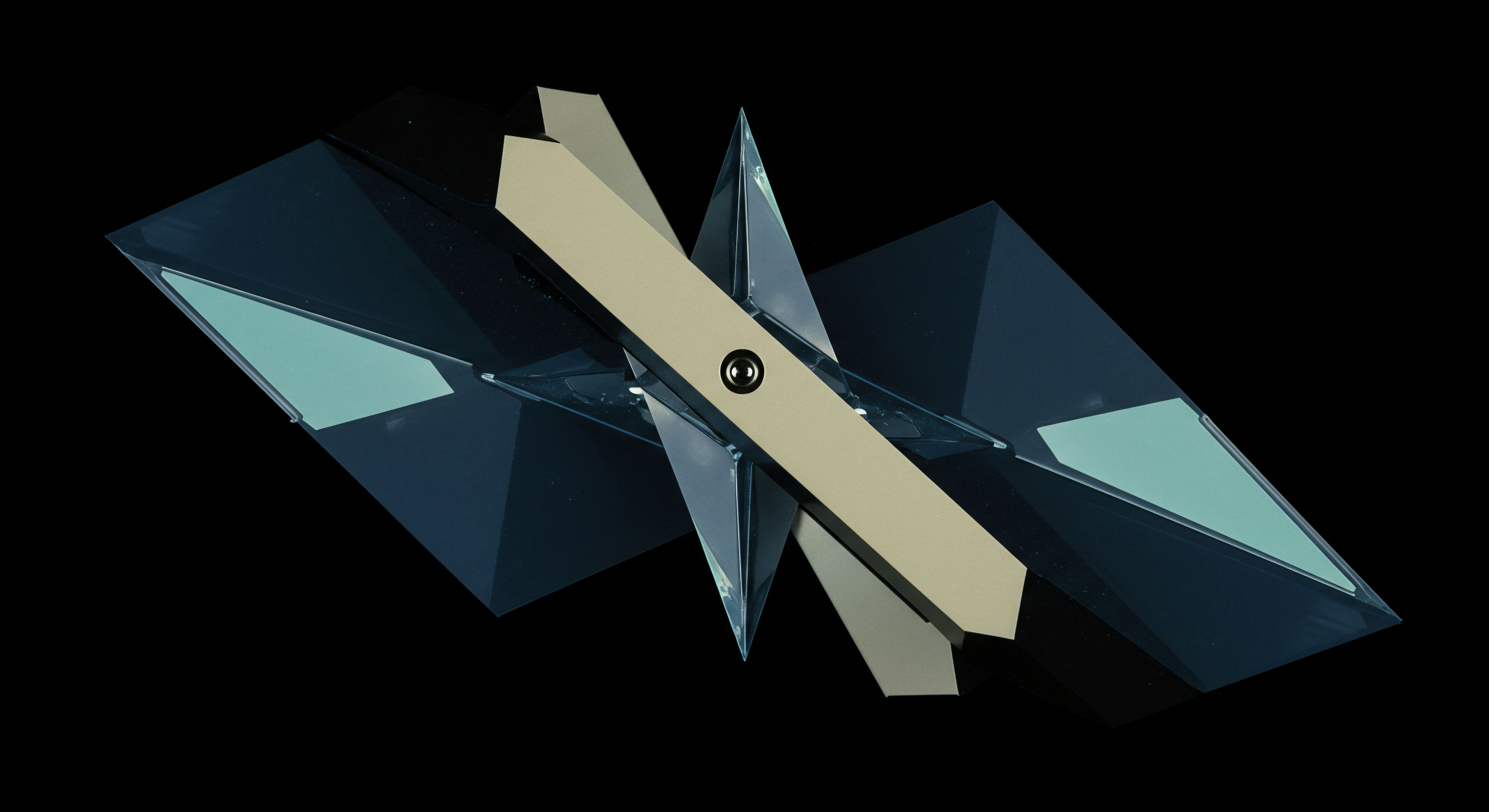

The Three Pillars of Latency

The sources of delay can be categorized into a clear hierarchy. This framework allows for a structured approach to analysis and optimization, ensuring that resources are allocated to the components with the greatest impact on overall system speed.

- Network Latency This is the time it takes for data to travel from one point to another. It is governed by the physical distance between the trading firm’s servers and the exchange’s data center, the speed of light through the transmission medium (fiber optic cable or microwave), and the time taken by network devices like switches and routers to process and forward data packets.

- Hardware Latency This encompasses the delays introduced by the physical components of the trading system itself. It includes the time taken by the server’s CPU to execute instructions, the latency of accessing data from RAM, the performance of the network interface card (NIC) in placing data onto the network, and the contribution of specialized hardware like FPGAs.

- Software and Application Latency This is the delay caused by the operating system and the trading application. It includes the time spent processing incoming market data, executing the trading strategy’s logic, constructing an order, and serializing that order into the FIX protocol format for transmission. Factors such as programming language, code efficiency, data structures, and the overhead of the operating system’s network stack all contribute to this category of latency.

A trading system’s latency is the cumulative delay across its network, hardware, and software components, each representing a distinct battleground in the war for speed.

The FIX protocol is a central component of the software and application latency puzzle. While its standardization is a significant advantage for connectivity across different venues, its design characteristics present a challenge for ultra-low latency applications. A binary protocol, in contrast, uses a more compact and machine-friendly data representation, reducing the time required for serialization and deserialization.

The choice between FIX and a proprietary binary protocol is a strategic one, balancing the benefits of a universal standard against the performance gains of a specialized, optimized communication format. The decision hinges on the specific requirements of the trading strategy and the technological capabilities of the firm.

Strategy

A strategic approach to latency management in HFT systems moves beyond simple identification of delay sources. It involves creating a comprehensive framework for measuring, analyzing, and systematically reducing latency across the entire trading architecture. This strategy is predicated on the understanding that latency is a dynamic variable, influenced by market conditions, technological advancements, and the actions of competitors.

The goal is to build a system that is not only fast but also resilient, consistent, and adaptable. The core of this strategy lies in a granular, component-level analysis of the three pillars of latency ▴ network, hardware, and software.

Architecting the Network for Speed

Network latency is often the largest and most challenging component of the total latency budget. The strategy for mitigating it revolves around minimizing physical distance and optimizing the path data travels.

What Is the Impact of Geographic Distance?

The absolute lower bound of network latency is determined by the speed of light. The most effective strategy to combat this physical limitation is colocation. By placing the firm’s trading servers in the same data center as the exchange’s matching engine, the physical distance data must travel is reduced to a few meters. This single action can eliminate milliseconds of round-trip time compared to a server located in a different city or state.

For firms that cannot or choose not to colocate, the strategy shifts to selecting the lowest latency network routes available, often through specialized telecom providers who offer direct fiber paths or even microwave transmission networks between major financial hubs. Microwave networks, being line-of-sight and traveling through the air, can offer a speed advantage over fiber optic cables, which must follow the contours of the land.

Colocation is the foundational strategy for conquering the latency imposed by physical distance, placing a firm’s systems in the same data center as the exchange itself.

Optimizing the Network Path

Once the geographic distance is minimized, the focus shifts to the latency introduced by the network hardware itself. Every switch, router, and firewall in the data path adds a small delay as it processes and forwards packets. The strategy here is to create the shortest, most direct path possible from the server’s network interface card (NIC) to the exchange’s entry point. This involves:

- Direct Market Access (DMA) Utilizing DMA allows a firm’s orders to be sent directly to the exchange’s network, bypassing the infrastructure of a broker-dealer. This removes an entire layer of potential latency.

- Low-Latency Switches Modern network switches designed for HFT environments can forward packets in a few hundred nanoseconds or less. A strategic hardware refresh to the latest generation of switches is a common tactic for shaving critical nanoseconds off the network path.

- Kernel Bypass This is a software technique that allows the trading application to communicate directly with the NIC, bypassing the operating system’s network stack. The standard network stack, while robust and feature-rich, is designed for general-purpose computing and introduces significant latency. Kernel bypass technologies like Solarflare’s Onload or Mellanox’s VMA can reduce latency by several microseconds.

Hardware as a Performance Variable

The hardware on which the trading system runs is a critical determinant of its performance. The strategy for hardware optimization is to select and configure components for the lowest possible processing delay.

The table below compares different hardware components and their typical contribution to latency, illustrating the strategic choices a firm must make.

| Component | Standard Implementation | Low-Latency Alternative | Typical Latency Reduction |

|---|---|---|---|

| CPU | General-purpose server CPU | High clock speed CPU, overclocked | 1-5 microseconds per operation |

| Memory | Standard DDR4 RAM | Low-latency DDR4 RAM with tighter timings | 10-50 nanoseconds per access |

| Network Interface Card (NIC) | Standard 10GbE NIC | Kernel-bypass enabled NIC | 5-10 microseconds per message |

| Specialized Hardware | CPU-only processing | Field-Programmable Gate Array (FPGA) | Orders of magnitude (microseconds to nanoseconds) |

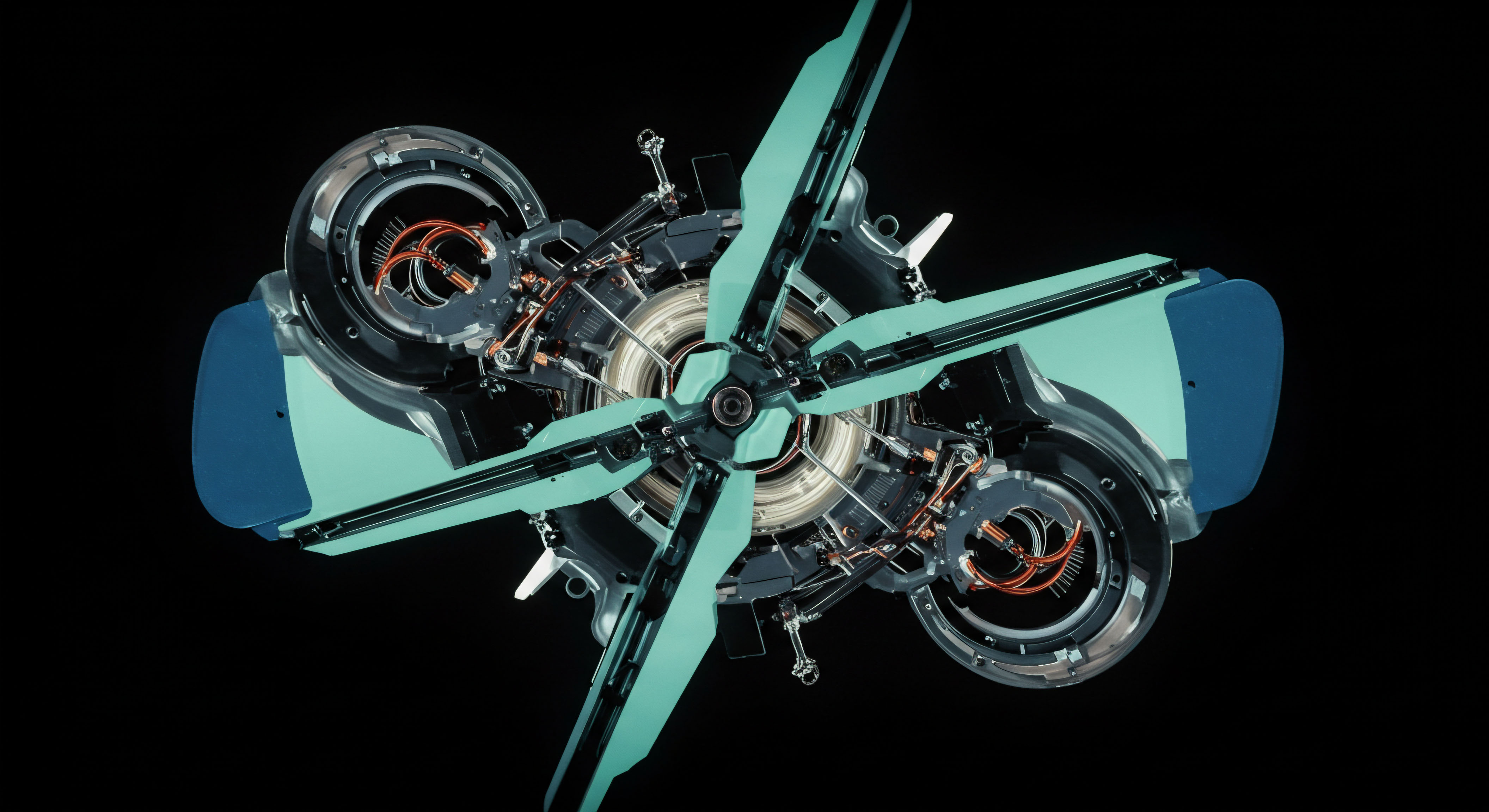

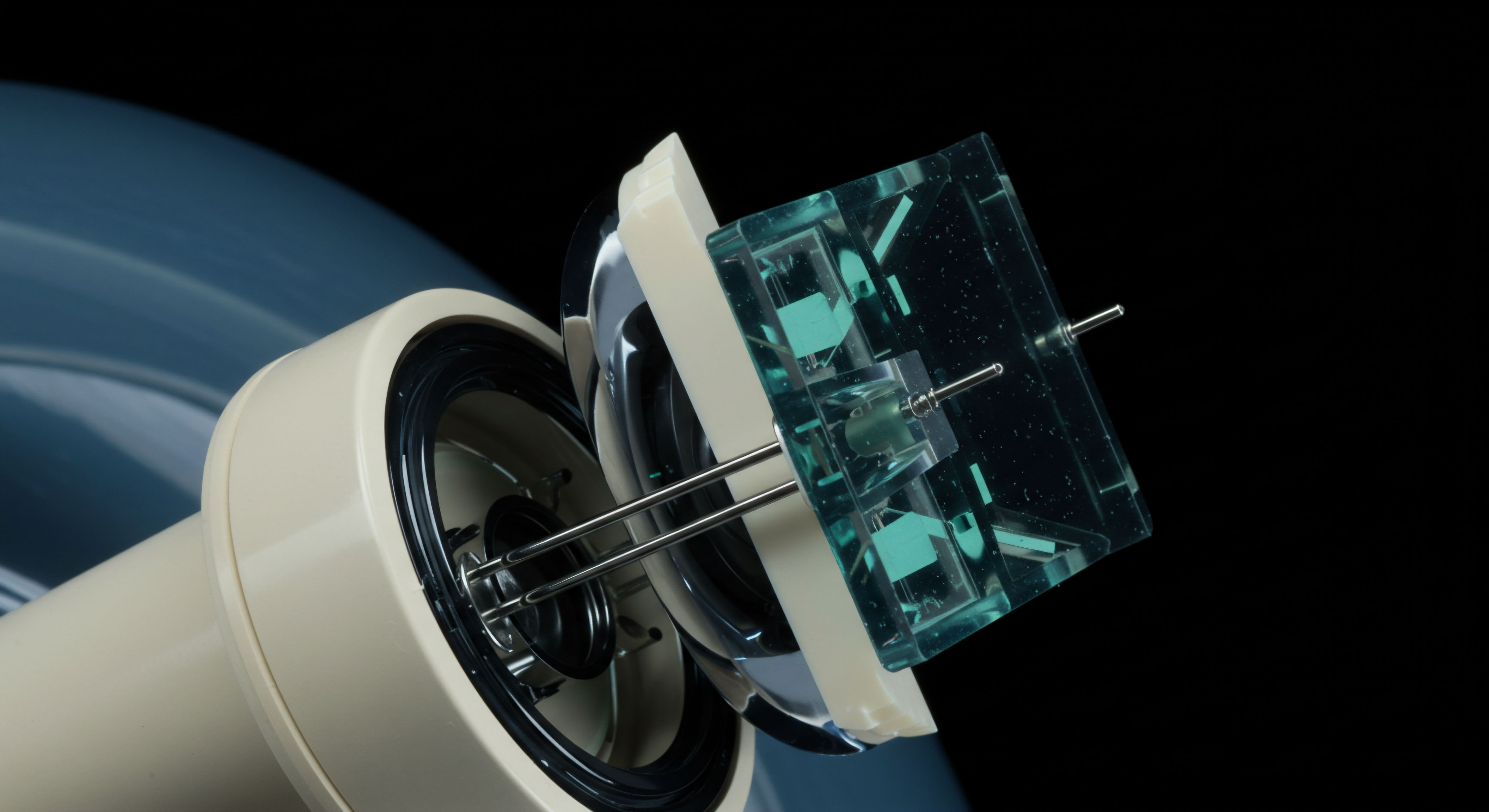

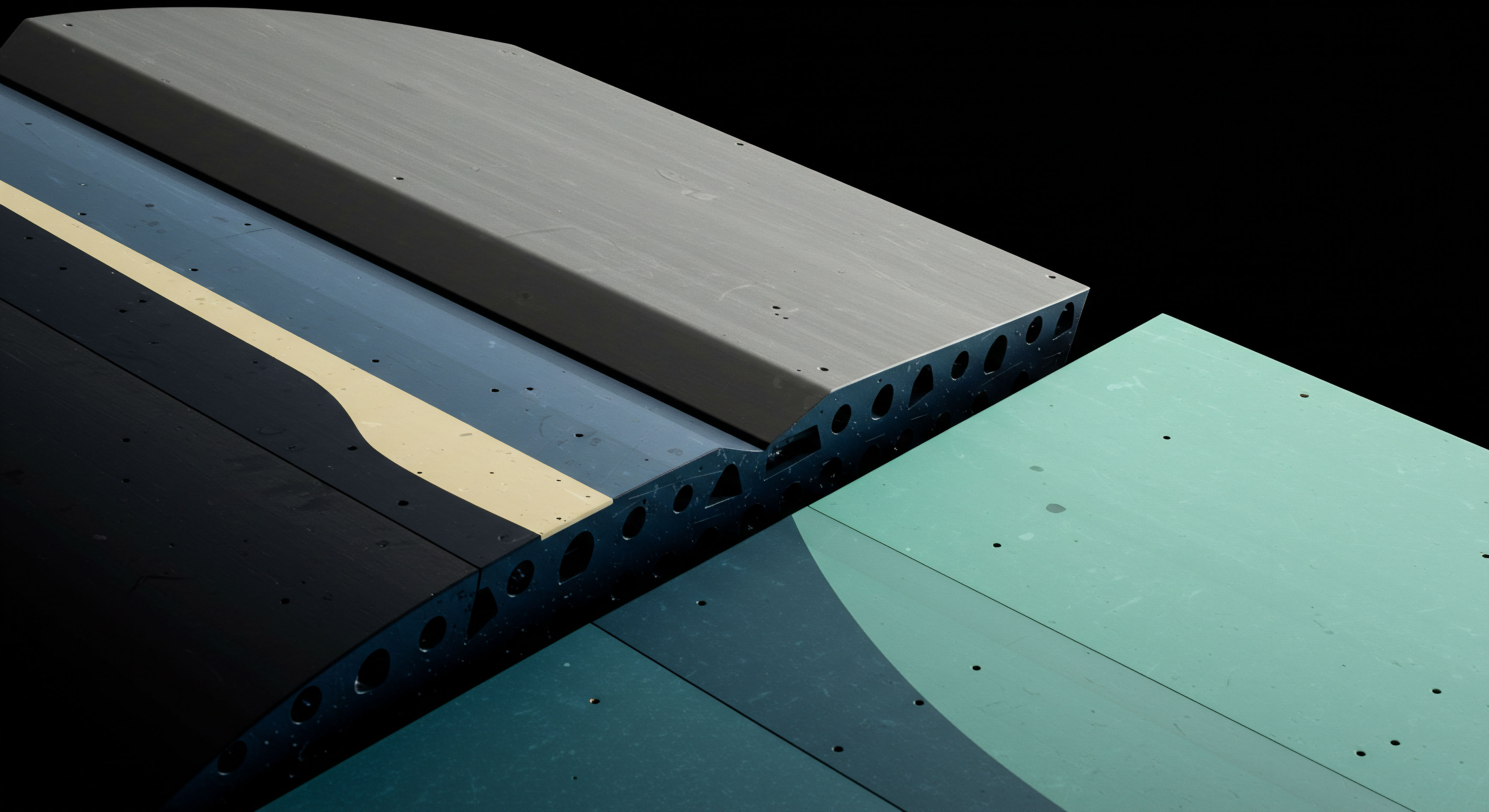

The Role of Specialized Hardware FPGAs

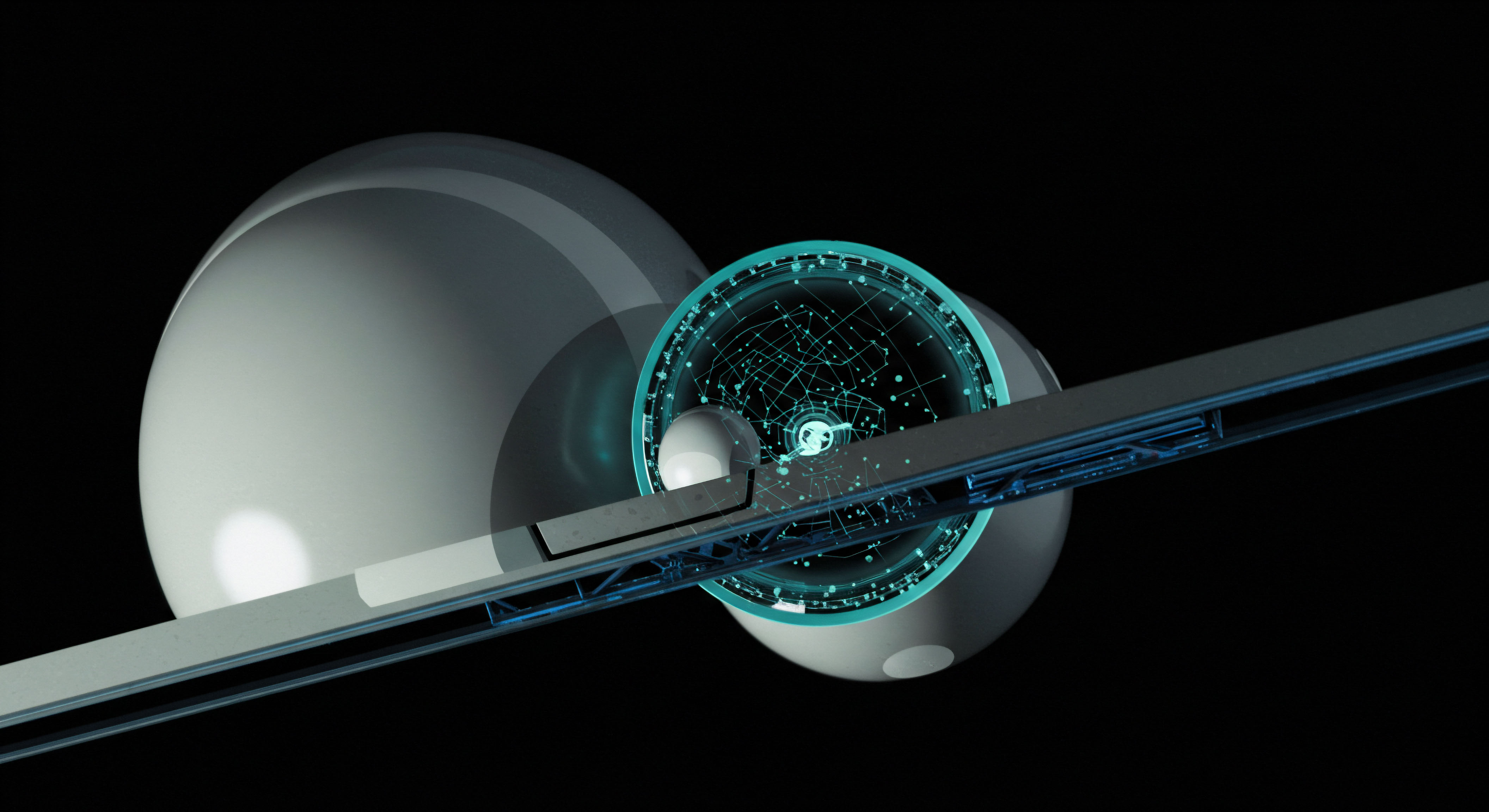

For the most latency-sensitive tasks, a purely software-based approach may not be sufficient. Field-Programmable Gate Arrays (FPGAs) are integrated circuits that can be programmed to perform specific tasks in hardware. This allows for a level of parallelism and determinism that is impossible to achieve with a general-purpose CPU. A common strategy is to offload specific functions, such as FIX message parsing, market data processing, or risk checks, to an FPGA.

An FPGA can perform these tasks in a few hundred nanoseconds, compared to the several microseconds it might take on a CPU. The strategic decision to use FPGAs involves a trade-off between their significant performance benefits and their higher cost and development complexity.

Tuning the Software Engine

Software and application latency is the most complex and multifaceted source of delay. It is also the area where a firm can create the most significant proprietary advantage through superior design and engineering. The strategy for software optimization is a continuous process of profiling, analysis, and refinement.

How Does the FIX Protocol Contribute to Latency?

The FIX protocol, being text-based, requires parsing. A FIX message like 8=FIX.4.29=7535=D49=SENDERCOMPID56=TARGETCOMPID11=ORDER138=10040=254=155=AAPL10=168 must be read, validated, and converted into a data structure the application can use. This process, while seemingly simple, can consume thousands of CPU cycles. A key strategy for mitigating FIX latency is to use a highly optimized FIX engine.

These engines are specifically designed for low-latency environments and employ techniques like pre-allocating memory and using efficient parsing algorithms. For the absolute lowest latency, firms may use a proprietary binary protocol for communication with exchanges that support it. The table below compares FIX with a typical binary protocol.

| Attribute | FIX Protocol | Binary Protocol |

|---|---|---|

| Format | ASCII Text, Tag=Value | Pre-defined binary structure |

| Message Size | Larger, verbose | Smaller, compact |

| Parsing Overhead | High (string manipulation) | Low (direct memory mapping) |

| Flexibility | High (easy to add custom tags) | Low (rigid structure) |

| Interoperability | Universal standard | Proprietary, exchange-specific |

Code-Level Optimization Techniques

The trading application itself is a major source of latency. A disciplined, performance-oriented approach to software development is essential. Key strategies include:

- Language Choice Languages like C++ and Rust, which offer low-level memory management and control, are favored for HFT development. Languages with automatic garbage collection, like Java or C#, can introduce unpredictable pauses, which are unacceptable in a low-latency system. While it is possible to write low-latency applications in these languages, it requires deep expertise in tuning the garbage collector.

- Data Structures Using cache-friendly data structures is critical. The time it takes for a CPU to access data from its L1 cache is orders of magnitude faster than accessing it from main memory. Algorithms and data structures should be designed to maximize cache hits.

- CPU Pinning Pinning a critical thread to a specific CPU core ensures that it is not moved between cores by the operating system’s scheduler. This avoids cache misses and context-switching overhead, leading to more deterministic performance.

Ultimately, a successful latency reduction strategy is holistic. It requires a deep understanding of how network, hardware, and software components interact. It is an iterative process of measurement, analysis, and optimization, driven by a relentless focus on improving the end-to-end performance of the trading system.

Execution

The execution of a low-latency strategy transitions from theoretical understanding to the tangible, rigorous engineering of a high-performance trading system. This phase is about the precise implementation of the chosen strategies, involving detailed operational procedures, quantitative measurement, and the creation of a robust technological architecture. It is where the conceptual becomes concrete, and the pursuit of nanoseconds becomes a matter of disciplined, methodical work.

The Operational Playbook for Latency Reduction

Building and maintaining a low-latency HFT system requires a structured, repeatable process. This playbook outlines the key steps an organization must take to execute its latency reduction strategy effectively. It is a continuous cycle of improvement, as the market and technology landscape are in constant flux.

- Establish a Baseline The first step is to accurately measure the current latency of the system. This involves instrumenting the code to capture timestamps at critical points in the order lifecycle ▴ market data ingress, decision logic execution, order creation, and order egress. Network-level measurements using packet capture appliances are also essential to get a complete picture. This baseline provides the starting point against which all future improvements will be measured.

- Component-Level Profiling With a baseline established, the next step is to break down the total latency into its constituent parts. This involves a deep dive into the performance of each component in the network, hardware, and software stacks. Tools like CPU profilers, network analyzers, and custom logging frameworks are used to identify the specific functions, network hops, or hardware components that are the largest contributors to the overall delay.

- Prioritize Optimization Targets The profiling data will reveal the “low-hanging fruit” ▴ the areas where the most significant latency reductions can be achieved with the least effort. The organization must prioritize these targets based on a cost-benefit analysis. For example, optimizing a single line of code in a critical path might yield a greater performance improvement than a costly hardware upgrade.

- Implement and Test Once a target has been selected, the proposed optimization is implemented. This could be a software change, a hardware upgrade, or a network reconfiguration. The change is then rigorously tested in a controlled environment to ensure that it delivers the expected performance improvement without introducing any unintended side effects or instability.

- Measure and Validate After testing, the change is deployed to the production environment, and the system’s latency is measured again. The new measurements are compared against the baseline to validate the effectiveness of the optimization. This data-driven approach ensures that decisions are based on empirical evidence, not assumptions.

- Iterate and Refine The process then repeats, with the organization continuously seeking out new opportunities for optimization. The pursuit of lower latency is an ongoing arms race, and a commitment to continuous improvement is essential for maintaining a competitive edge.

Quantitative Modeling and Data Analysis

A quantitative approach is essential for understanding and managing latency. This involves creating detailed models of the trading system’s performance and using data analysis to identify and diagnose issues. The table below provides a hypothetical latency budget for a single order in a colocated HFT system, illustrating the level of granularity required for effective analysis.

| Stage | Component | Latency (Nanoseconds) | Cumulative Latency (Nanoseconds) |

|---|---|---|---|

| Market Data Ingress | Exchange Switch to Server NIC | 300 | 300 |

| NIC to Application (Kernel Bypass) | 800 | 1,100 | |

| FIX/Binary Deserialization (FPGA) | 200 | 1,300 | |

| Decision Logic | Trading Algorithm Execution (CPU) | 1,500 | 2,800 |

| Risk Check (FPGA) | 150 | 2,950 | |

| Order Egress | FIX/Binary Serialization (FPGA) | 200 | 3,150 |

| Application to NIC (Kernel Bypass) | 800 | 3,950 | |

| Server NIC to Exchange Switch | 300 | 4,250 | |

| Total End-to-End Latency | 4,250 ns (4.25 µs) | ||

This level of detailed analysis allows a firm to pinpoint exact sources of delay. For instance, if the trading algorithm execution time suddenly increases, it points to a potential issue in the software. If the network transit time increases, it could indicate a problem with a switch or a cable. This quantitative approach transforms latency management from guesswork into a data-driven science.

System Integration and Technological Architecture

The technological architecture of an HFT system is the foundation upon which its performance is built. The integration of various hardware and software components must be seamless to avoid introducing unnecessary latency. A well-architected system is designed from the ground up for speed and determinism.

How Should One Design the Software Architecture?

The design of the trading application is a critical factor in its performance. A common architectural pattern is a single-threaded, event-driven model. In this design, a single thread is responsible for processing all incoming market data and executing the trading logic. This avoids the overhead and non-determinism associated with multi-threaded programming, such as context switching and lock contention.

The application is built around an event loop that continuously polls for new market data, processes it, and sends out orders. To handle the high volume of data, non-blocking I/O is used, ensuring that the main thread is never idle waiting for data to be read or written.

The Role of the Operating System

The choice and configuration of the operating system can have a significant impact on latency. Most HFT firms use a customized version of Linux, stripped down to its bare essentials to reduce jitter and overhead. Key optimizations include:

- Real-Time Kernel Using a real-time kernel patch can provide more deterministic scheduling and reduce the likelihood of preemption of critical threads.

- Interrupt Affinity Assigning network card interrupts to a specific CPU core, separate from the one running the trading logic, can improve cache performance and reduce jitter.

- Disabling Unnecessary Services Any service or process that is not absolutely essential for the operation of the trading system is disabled to free up CPU resources and eliminate potential sources of interference.

The execution of a low-latency strategy is a testament to a firm’s engineering discipline and commitment to excellence. It is a continuous, iterative process that demands a deep understanding of the entire technology stack, from the physical layer of the network to the highest levels of the application software. In the world of HFT, where success is measured in nanoseconds, this level of execution is not just an advantage; it is a necessity for survival.

References

- Harris, Larry. “Trading and exchanges ▴ Market microstructure for practitioners.” Oxford University Press, 2003.

- Lehalle, Charles-Albert, and Sophie Laruelle. “Market microstructure in practice.” World Scientific, 2013.

- Narayan, Pankaj, et al. “Low latency trading.” Capital Markets CRC, 2011.

- O’Hara, Maureen. “Market microstructure theory.” Blackwell, 1995.

- Gomber, Peter, et al. “High-frequency trading.” Working paper, Goethe University Frankfurt, 2011.

- Hasbrouck, Joel. “Empirical market microstructure ▴ The institutions, economics, and econometrics of securities trading.” Oxford University Press, 2007.

- Aldridge, Irene. “High-frequency trading ▴ a practical guide to algorithmic strategies and trading systems.” John Wiley & Sons, 2013.

- Lockwood, John, et al. “A Low-Latency Library in FPGA Hardware for High-Frequency Trading (HFT).” Hot Interconnects (HOTI), 2012 IEEE 20th Annual Symposium on. IEEE, 2012.

Reflection

The architectural pursuit of minimal latency in a trading system is a microcosm of the larger competitive dynamics in financial markets. The knowledge gained in dissecting the sources of delay ▴ from the physical constraints of light speed to the abstract logic of a software algorithm ▴ provides more than just a temporal advantage. It cultivates a systemic understanding of the market itself. Each nanosecond reclaimed is a testament to a deeper insight into the intricate machinery of price discovery and liquidity provision.

Consider your own operational framework. Where are the hidden sources of friction? Are decisions data-driven, or are they based on convention and assumption? The process of latency optimization forces a level of introspection and rigor that can benefit all aspects of a trading operation.

It compels an organization to question every component, every process, and every line of code, fostering a culture of continuous improvement and empirical validation. The ultimate goal is to construct a system of intelligence where technology, strategy, and execution are so seamlessly integrated that the entire operation functions as a single, highly adapted organism, capable of responding to market stimuli with speed and precision. The strategic potential lies in this holistic, system-level mastery.

Glossary

High-Frequency Trading

Fix Protocol

Market Data

Physical Distance

Network Latency

Network Interface Card

Trading System

Trading Application

Binary Protocol

Colocation

Network Hardware

Direct Market Access

Kernel Bypass

Fpga

Fix Engine