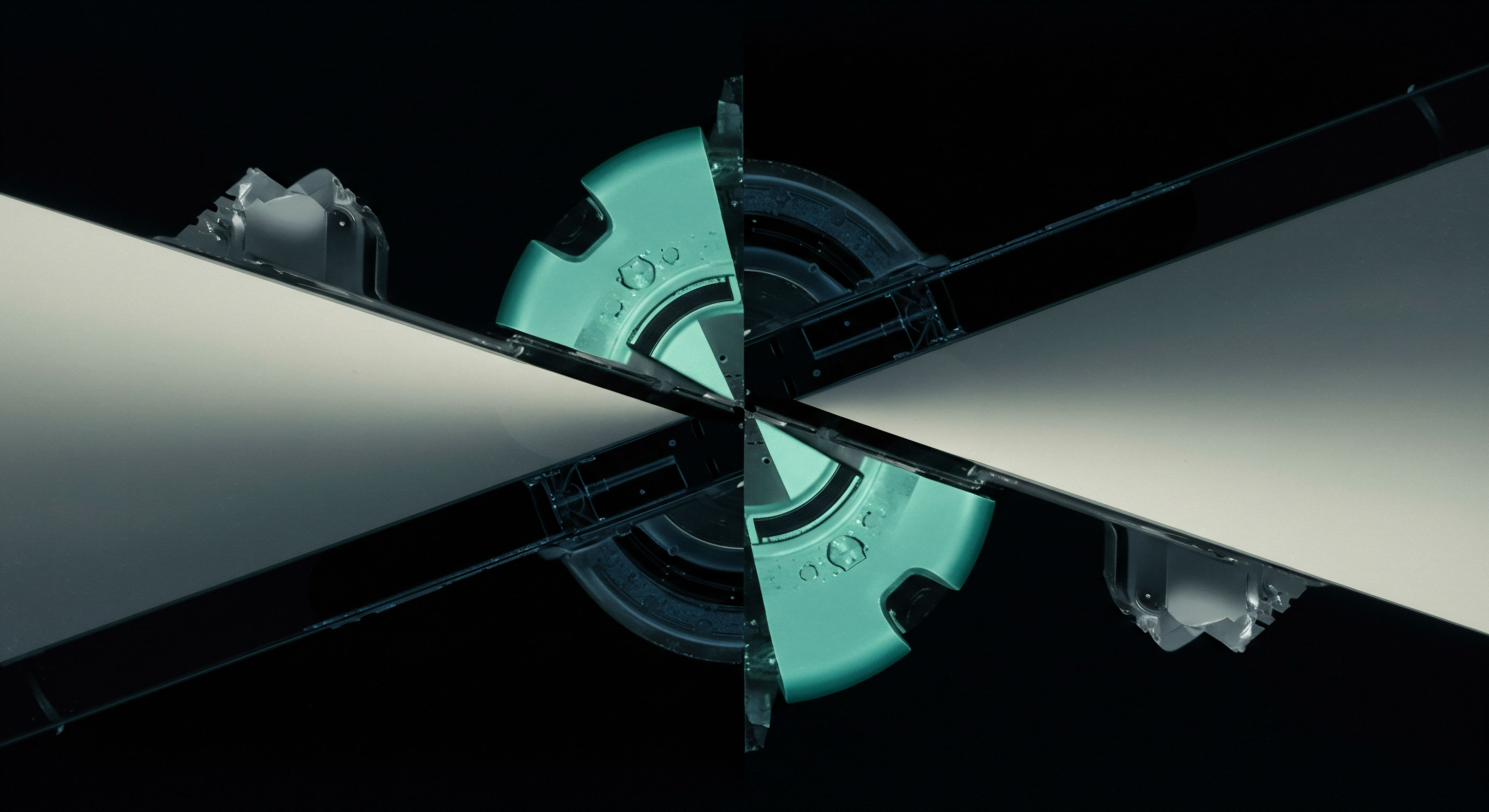

Concept

The decision between hardware acceleration and software-based data processing is a defining moment in the construction of any institutional trading system. This choice dictates the fundamental operational posture of a firm, establishing its relationship with speed, adaptability, and ultimately, its competitive identity in the marketplace. The core of the matter lies in understanding how each approach engages with data at a physical and logical level. One method manipulates data directly within silicon, achieving velocity through dedicated, immutable pathways.

The other directs data through layers of abstraction, gaining flexibility at the cost of time. For a trading institution, this is not an abstract technological preference; it is the central engineering problem that shapes every subsequent strategic and tactical capability.

Hardware acceleration, most prominently realized through Field-Programmable Gate Arrays (FPGAs), represents a paradigm of processing where algorithms are etched into the physical circuitry of a chip. An FPGA is a collection of configurable logic blocks that can be wired in a specific arrangement to perform a dedicated task, such as decoding a market data feed or executing a pre-trade risk check. This design allows for true parallelism, where multiple operations occur simultaneously, independent of one another. The result is processing measured in nanoseconds and, equally important, deterministic latency.

Determinism means that a given operation will take the same amount of time to execute every single time, eliminating the “jitter” or performance variability that plagues software systems. This predictability is a profound operational advantage in environments where consistency is as valuable as raw speed.

The foundational trade-off is a direct exchange of immutable, nanosecond-level speed in hardware for the dynamic, microsecond-level adaptability of software.

Conversely, software-based processing relies on Central Processing Units (CPUs) or Graphics Processing Units (GPUs) to execute a sequence of instructions. A CPU is a general-purpose processor, designed to handle a vast array of tasks by loading and running different programs. This inherent flexibility is its greatest strength. A trading algorithm running in software can be modified and redeployed rapidly, allowing a firm to adapt its strategies to changing market conditions with minimal friction.

Development cycles are shorter, and the talent pool for languages like C++ or Java is far larger than for hardware description languages like Verilog or VHDL. However, this adaptability comes with a performance overhead. The CPU must fetch instructions from memory, contend with operating system interruptions, and manage shared resources, all of which introduce latency and variability into the execution path.

The table below outlines the primary distinctions between these two processing philosophies from a systemic viewpoint.

| Attribute | Hardware Acceleration (FPGA) | Software-Based Processing (CPU/GPU) |

|---|---|---|

| Core Processing Unit | Configurable logic blocks implementing a specific algorithm in silicon. | General-purpose cores executing a sequential set of instructions. |

| Typical Latency | Nanoseconds (billionths of a second). | Microseconds to milliseconds (millionths to thousandths of a second). |

| Performance Consistency | Deterministic; execution time is highly predictable and consistent. | Non-deterministic; subject to jitter from OS, cache misses, and resource contention. |

| Development Paradigm | Hardware description languages (e.g. Verilog, VHDL); longer development cycles. | High-level programming languages (e.g. C++, Java, Python); rapid development. |

| Flexibility & Adaptability | Low; changes require reconfiguring the hardware logic, a complex process. | High; algorithms can be modified and recompiled quickly. |

| Primary Use Case in Finance | Ultra-low latency tasks ▴ market data feed handling, risk checks, simple order execution. | Complex strategy logic, post-trade analysis, modeling, and user interfaces. |

Understanding this fundamental dichotomy is the first step in designing an effective trading apparatus. It is a choice between building a system optimized for a specific, well-defined function that operates at the physical limits of speed, and constructing a system that can evolve and respond to new information and strategies. The most sophisticated institutions recognize that this is not an “either/or” proposition but a question of intelligent integration. The challenge lies in architecting a hybrid system where each component is deployed precisely where its unique strengths provide the greatest strategic value.

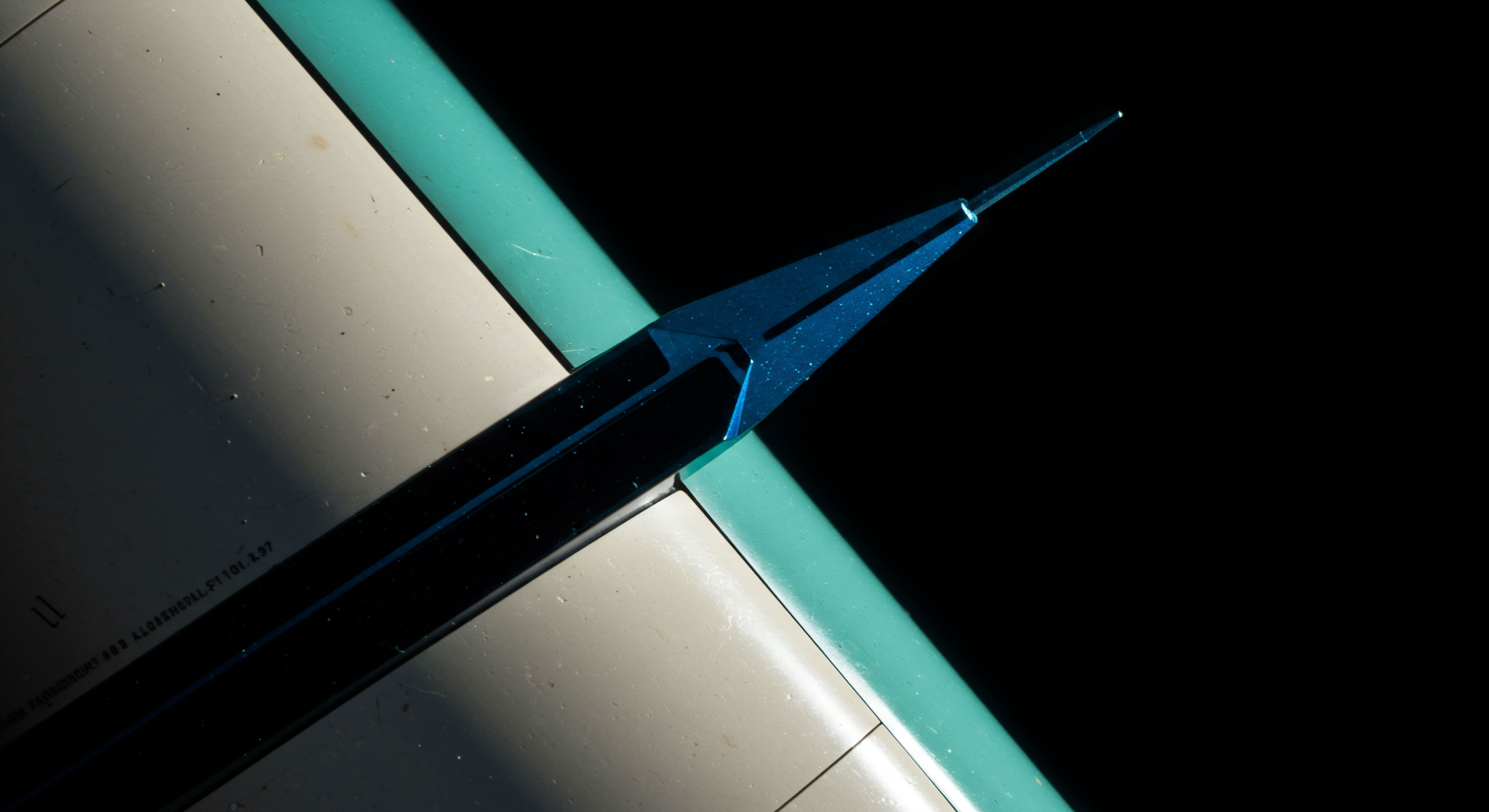

Strategy

A firm’s strategic approach to data processing architecture is a direct reflection of its trading philosophy. The allocation of tasks between hardware and software defines the operational boundaries within which all trading strategies must exist. A coherent strategy does not simply choose the fastest component for every task; it maps the firm’s sources of competitive advantage to the appropriate processing domain.

This involves a granular analysis of the entire trading lifecycle, from the moment market data enters the firm’s systems to the final settlement of a trade. The goal is to create a symbiotic relationship between hardware and software, where the determinism of silicon underpins the creative adaptability of code.

The Triumvirate of Latency

The trading process can be segmented into three distinct latency domains, each with its own strategic imperatives and corresponding technology choices. The optimal system architecture recognizes these divisions and deploys resources accordingly, creating a tiered structure that aligns processing power with functional requirements.

- The Nanosecond Frontier (Hardware Domain) This is the realm of pure speed, where the primary objective is to react to external market events faster than any competitor. Tasks residing here are simple, repetitive, and must be executed with minimal and predictable delay. This is the exclusive territory of hardware acceleration.

- Market Data Ingress and Decoding ▴ Parsing binary exchange feeds (like FAST or ITCH) directly in hardware bypasses the entire software network stack, saving critical microseconds.

- Order Book Management ▴ Maintaining the state of the limit order book within the FPGA’s on-chip memory allows for instantaneous access and updates.

- Pre-Trade Risk Controls ▴ Implementing simple, universal risk checks (e.g. fat-finger checks, maximum order size) in hardware provides a non-negotiable safety layer with virtually zero performance penalty.

- The Microsecond Core (Hybrid Domain) This domain houses the firm’s proprietary logic and more complex decision-making processes. Latency is still a vital concern, but the need for algorithmic complexity and adaptability becomes more prominent. This is where the strategic hand-off between hardware and software often occurs.

- Signal Generation ▴ A hardware component might identify a basic market condition (a signal), which is then passed to a software application for more nuanced evaluation.

- Complex Strategy Execution ▴ The software component receives the hardware-generated signal and applies a richer set of rules, considering factors like existing inventory, broader market trends, or correlated asset movements.

- Smart Order Routing (SOR) ▴ While the initial data processing may be in hardware, the logic for routing an order across multiple venues often resides in software to accommodate the complexity of different fee structures and liquidity profiles.

- The Millisecond Backplane (Software Domain) This area supports the trading operation but is not on the critical execution path. Here, flexibility, analytical power, and ease of use take precedence over raw speed.

- Post-Trade Analytics ▴ Analyzing execution quality (TCA), calculating P&L, and generating reports are tasks well-suited for the power and flexibility of software.

- Quantitative Model Development ▴ Training machine learning models, backtesting strategies against historical data, and performing large-scale simulations are computationally intensive tasks that rely on the vast libraries and development environments available in software.

- System Monitoring and Control ▴ The dashboards and interfaces used by human traders and support personnel to oversee the automated systems are exclusively software applications.

A winning strategy is not about universal hardware acceleration, but about the surgical application of speed at points where it creates a nonlinear advantage.

A Framework for Architectural Decisions

Choosing where to draw the line between hardware and software requires a multi-dimensional analysis. A firm must weigh the performance gains against the operational costs and constraints. The following table provides a strategic framework for this evaluation, moving beyond simple latency to consider the broader business implications.

| Strategic Dimension | Hardware Acceleration (FPGA) | Software-Based Processing (CPU/GPU) |

|---|---|---|

| Time-to-Market | Long. Development, testing, and deployment cycles can span months or even years. | Short. New strategies and modifications can be deployed in days or weeks. |

| Development Cost | High. Requires specialized hardware engineers with expertise in niche languages and tools, commanding premium salaries. | Moderate. Access to a large, global talent pool of software developers. |

| Operational Agility | Low. Adapting to new exchange protocols or market structures is a significant engineering effort. | High. The system can be rapidly updated to capitalize on new opportunities or respond to rule changes. |

| System Brittleness | High. An error in the hardware design can be catastrophic and difficult to patch. The system is optimized for a specific function and performs poorly outside of it. | Low. Software bugs can be patched and deployed quickly. General-purpose nature allows for graceful handling of unexpected inputs. |

| Scalability Profile | Scales by adding more physical hardware. Power and space can become constraints. | Scales by leveraging multi-core processors, distributed computing, and cloud infrastructure. |

| Competitive Moat | Deep and durable. A highly optimized hardware solution is difficult and expensive for competitors to replicate. | Shallow and transient. Software-based strategies can be reverse-engineered and copied more easily. |

Ultimately, the strategic deployment of hardware and software is a balancing act. A system composed entirely of FPGAs would be incredibly fast but also rigid and astronomically expensive to maintain. A system built only on CPUs would be flexible but would be perpetually outpaced in any latency-sensitive strategy. The art of modern trading system design is in creating a hybrid architecture that leverages each technology for its inherent strengths, building a resilient and powerful whole that is greater than the sum of its parts.

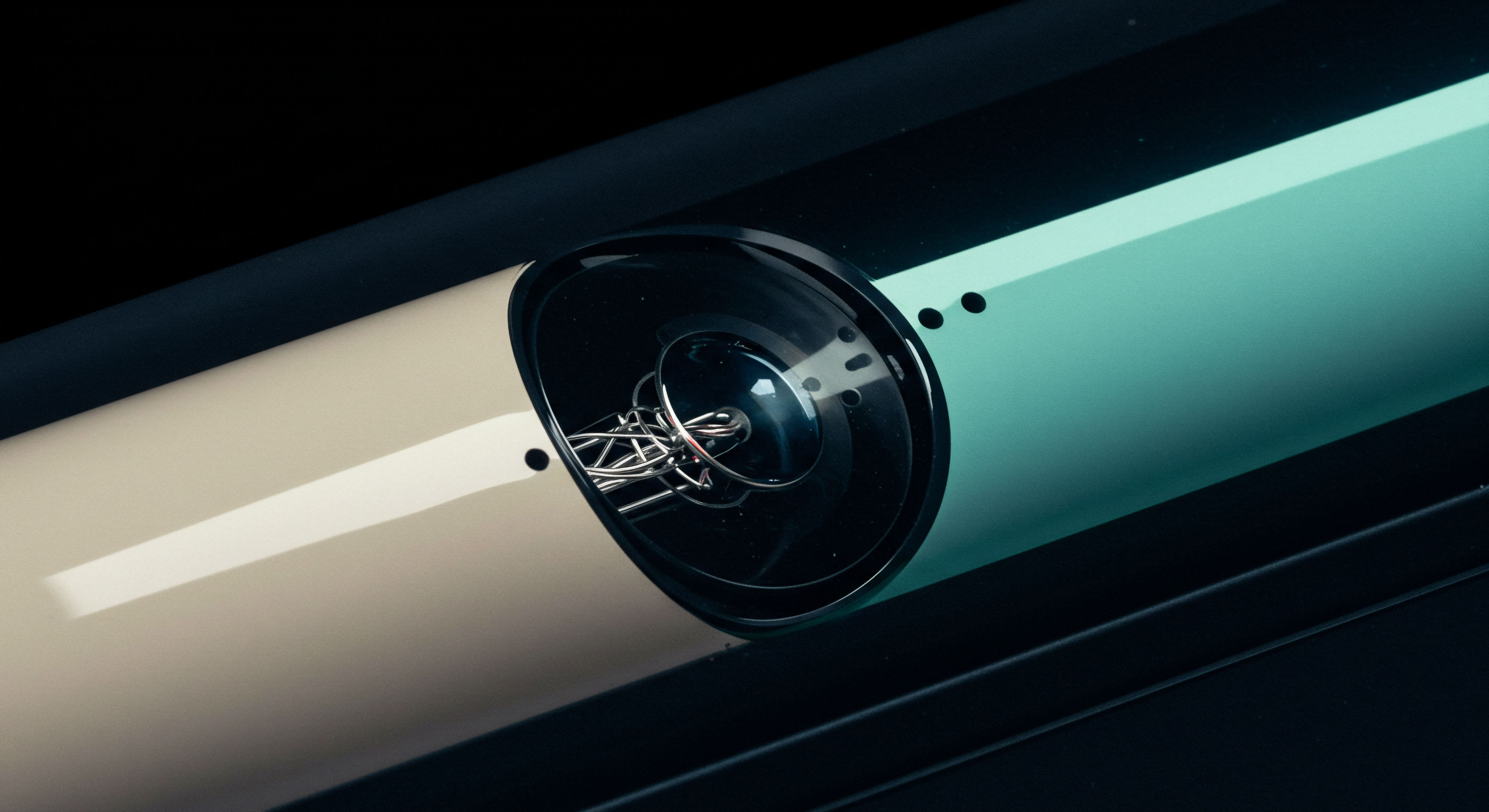

Execution

The theoretical trade-offs between hardware and software crystallize into tangible engineering challenges during execution. Building a high-performance trading system requires a meticulous approach to architecture, where every component is selected and integrated to serve a precise function within the latency budget. The execution phase is about translating strategic intent into a functioning, resilient, and profitable system. This involves designing a data pipeline that seamlessly transitions between the deterministic world of hardware and the dynamic environment of software, all while maintaining the integrity and speed of the entire operation.

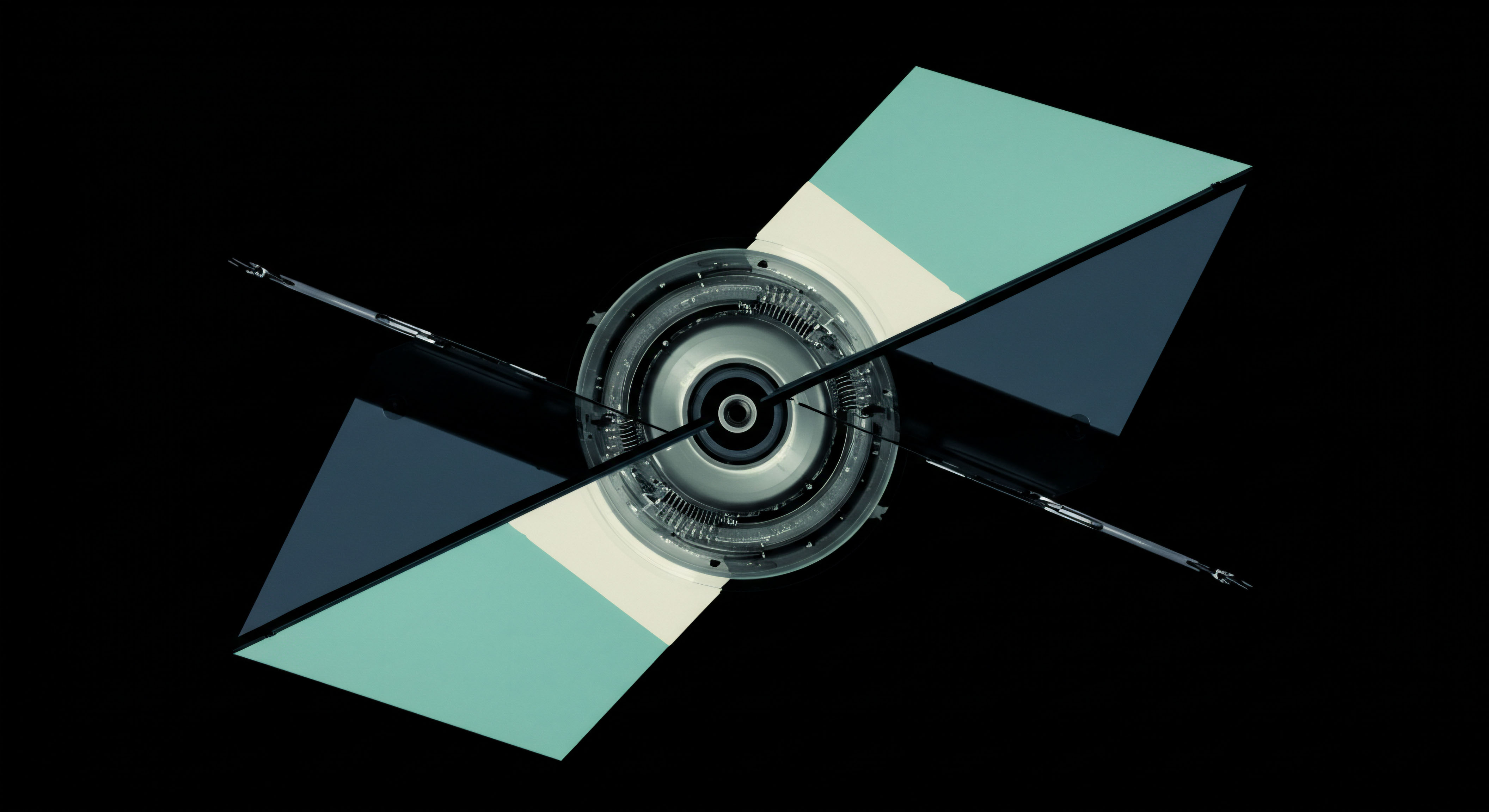

Anatomy of a Hybrid Execution Pipeline

Let us consider the practical implementation of a system designed for a latency-sensitive market-making strategy. The objective is to process incoming market data, identify a trading opportunity, and place an order in the market with the lowest possible round-trip time. The following ordered list details the flow of data through a well-architected hybrid system.

- Physical Ingress and Clock Synchronization The process begins at the physical layer. A fiber optic cable from the exchange terminates directly into a network interface card (NIC) equipped with an FPGA. The first task of the FPGA is to achieve picosecond-level clock synchronization with the exchange’s systems using protocols like Precision Time Protocol (PTP), establishing a true and accurate timestamp for all subsequent events.

- Hardware-Based Protocol Termination The FPGA immediately begins processing the raw stream of Ethernet packets. It performs the functions of a TCP/IP stack directly in its logic gates, decoding the network and transport layers without involving the host server’s operating system. This step alone can save tens of microseconds compared to a software-based network stack.

- Feed Handling and Order Book Construction Once the application-level data is exposed (e.g. a FIX/FAST protocol message), the FPGA parses the message. It is programmed to understand the specific message templates of the exchange. As it processes messages related to orders being added, cancelled, or executed, it builds and maintains a complete, real-time image of the limit order book in its own ultra-fast on-chip memory.

- Signal Generation in Silicon The core of the hardware’s “intelligence” resides here. A simple, predefined trading logic is implemented in the FPGA. For instance, the logic might be to identify when the best bid-offer spread widens beyond a certain threshold while the order book depth remains thick. Upon detecting this specific set of conditions, the FPGA generates a “trade signal.” This signal is a highly compressed piece of information containing only the essential data ▴ instrument ID, price, and side (buy/sell).

- The PCIe Hand-off The FPGA passes this trade signal to the host server’s CPU. This is a critical transition point. The communication occurs over a high-speed bus like PCI Express (PCIe), which allows for direct memory access (DMA) between the FPGA and the CPU’s memory space. This avoids any slow, intermediate copying and ensures the data transfer happens with minimal delay.

- Complex Logic and Risk Overlay in Software Now in the software domain, a highly optimized C++ application takes over. It receives the signal and applies a much richer and more complex set of rules that would be too cumbersome or slow to implement in hardware. This logic might consider the firm’s current inventory risk, the behavior of correlated instruments, or signals from slower, non-structured data sources. The software performs a final, more comprehensive set of risk checks.

- Order Execution and Hardware Egress If the software confirms the trade, it constructs an order message. This message is then passed back down to the FPGA via the same PCIe bus. The FPGA takes the software-generated order, packages it into the appropriate exchange protocol format, and sends it out through its dedicated network port. This ensures the final, critical step of placing the order benefits from the same low-latency egress path used for data ingress.

A system’s performance is defined not by its fastest component, but by the efficiency of the hand-offs between its constituent parts.

Quantifying the Latency Budget

The success of such a system depends on a rigorous accounting of time. The following table presents a hypothetical, yet realistic, latency budget for our hybrid pipeline, illustrating where every nanosecond is spent. This quantitative analysis is the foundation of performance engineering in institutional trading.

| Pipeline Stage | Processing Domain | Typical Latency | Cumulative Time |

|---|---|---|---|

| 1. Network Packet Ingress to FPGA | Hardware | ~50 ns | 50 ns |

| 2. Hardware Network Stack & Feed Decode | Hardware | ~150 ns | 200 ns |

| 3. Hardware Order Book Update & Signal Logic | Hardware | ~100 ns | 300 ns |

| 4. PCIe Transfer (FPGA to CPU) | Hardware/Software Interface | ~500 ns | 800 ns (0.8 µs) |

| 5. Software Strategy Logic & Risk Check | Software | ~2,000 ns (2.0 µs) | 2,800 ns (2.8 µs) |

| 6. PCIe Transfer (CPU to FPGA) | Software/Hardware Interface | ~500 ns | 3,300 ns (3.3 µs) |

| 7. Hardware Order Formatting & Egress | Hardware | ~150 ns | 3,450 ns (3.45 µs) |

This detailed breakdown demonstrates the power of the hybrid model. The entire “tick-to-trade” loop is completed in under 3.5 microseconds. A purely software-based system would struggle to even process the initial network packet in that time.

The hardware performs the heavy lifting on the speed-critical portions of the workflow, while the software provides the complex intelligence that turns a simple signal into a risk-managed trade. This division of labor is the essence of modern, high-performance execution.

References

- Locke, D. (2010). The end of the soft-core processor. White Paper, Altera Corporation.

- Behnam, B. et al. (2012). High Frequency Trading Acceleration using FPGAs. Proceedings of the 20th IEEE Annual International Symposium on Field-Programmable Custom Computing Machines.

- Harris, L. (2003). Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press.

- Werner, I. M. (2011). The Economics of FPGAs in Financial Trading. The Journal of Trading, 6(3), 45-56.

- O’Hara, M. (1995). Market Microstructure Theory. Blackwell Publishers.

- Gomber, P. & Gsell, M. (2006). Catching up with technology ▴ The impact of electronic trading on German stock market liquidity. In Proceedings of the 39th Annual Hawaii International Conference on System Sciences.

- Hendershott, T. Jones, C. M. & Menkveld, A. J. (2011). Does algorithmic trading improve liquidity?. The Journal of Finance, 66(1), 1-33.

- Chaboud, A. P. Chiquoine, B. Hjalmarsson, E. & Vega, C. (2014). Rise of the machines ▴ Algorithmic trading in the foreign exchange market. The Journal of Finance, 69(5), 2045-2084.

Reflection

The Architecture of Identity

The technical schematics of a firm’s data processing pipeline ultimately reveal more than just latency metrics; they map the institution’s core philosophy. The points at which data transitions from hardware to software are not merely engineering junctions, they are the precise locations where the firm has decided to trade raw, deterministic speed for cognitive, adaptive intelligence. Viewing the system in this light transforms the conversation from a simple technical audit into a profound strategic inquiry. Where has the decision been made to rely on reflexes etched in silicon, and where is there a reliance on logic that can learn and evolve?

This architecture becomes a durable expression of the firm’s identity in the market. An infrastructure heavily weighted towards hardware acceleration declares a belief in an advantage derived from pure velocity and an operational posture that is aggressive, specialized, and focused on exploiting fleeting, microscopic inefficiencies. Conversely, a system that prioritizes software flexibility indicates a philosophy centered on sophisticated modeling, complex alpha signals, and an ability to dynamically adapt to shifting market regimes.

There is no universally superior model. There is only alignment or misalignment.

Therefore, the continuous evaluation of this hybrid system is a critical function of institutional leadership. The question is not static. As technology evolves, the line between what is feasible in hardware and what is necessary in software shifts.

The truly resilient institution is one that understands its processing architecture as a living system, a direct reflection of its strategic mind. It constantly re-evaluates the balance, ensuring that its technological backbone is always in perfect concert with its intellectual core, creating a unified engine for capturing opportunity.

Glossary

Hardware Acceleration

Market Data

Latency

Determinism

Cpu

Between Hardware

Order Book Management

Order Book

Latency Budget

Fpga