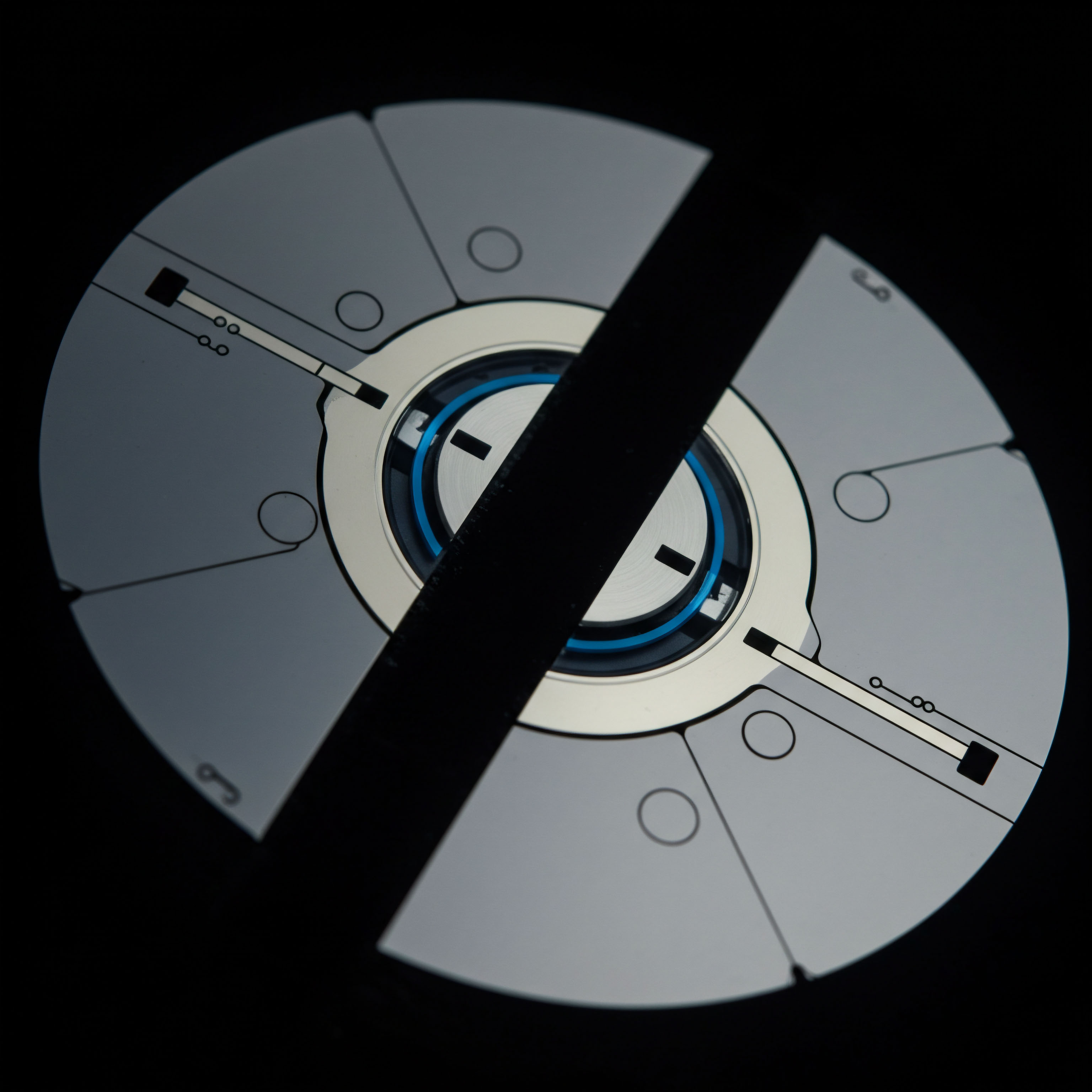

Concept

The operational calculus of modern financial markets is denominated in speed. At the most fundamental level, latency ▴ the delay between a market event and a trading system’s reaction ▴ is not merely a technical metric but a primary determinant of profitability and strategic viability. This delay is governed by the laws of physics and the architectural choices made deep within a trading system’s core.

The decision between sculpting logic directly into silicon with hardware-based solutions and optimizing instructional pathways through software defines the boundary of what is possible. Understanding this trade-off is the foundational prerequisite for constructing a system capable of competing in an environment where advantages are measured in nanoseconds.

Hardware-based latency reduction involves offloading time-critical functions from a server’s general-purpose Central Processing Unit (CPU) onto specialized processors. The most common of these are Field-Programmable Gate Arrays (FPGAs) and, in the most extreme cases, Application-Specific Integrated Circuits (ASICs). An FPGA is a configurable chip that can be programmed to perform a specific set of logical operations in parallel, directly in its circuitry.

This approach bypasses the overhead associated with a traditional operating system, where processes must wait for CPU time, contend with interrupts, and navigate multiple software layers. An ASIC represents the apex of this philosophy, a chip custom-designed and permanently fabricated to execute one function with maximum efficiency.

Conversely, software-based latency reduction focuses on refining the efficiency of code and its interaction with the operating system and network hardware. This is a world of meticulous optimization, from rewriting algorithms for computational efficiency to employing advanced techniques like kernel bypass. Kernel bypass allows an application to communicate directly with the network interface card (NIC), avoiding the time-consuming journey through the operating system’s standard networking stack.

It is a sophisticated method that pushes software to its absolute performance limits on commodity hardware, seeking to minimize the inherent delays of a system designed for general-purpose computing rather than singular, high-speed tasks. The choice is not simply between fast and faster; it is a complex, multi-variable equation involving speed, cost, flexibility, and the strategic intent of the trading entity itself.

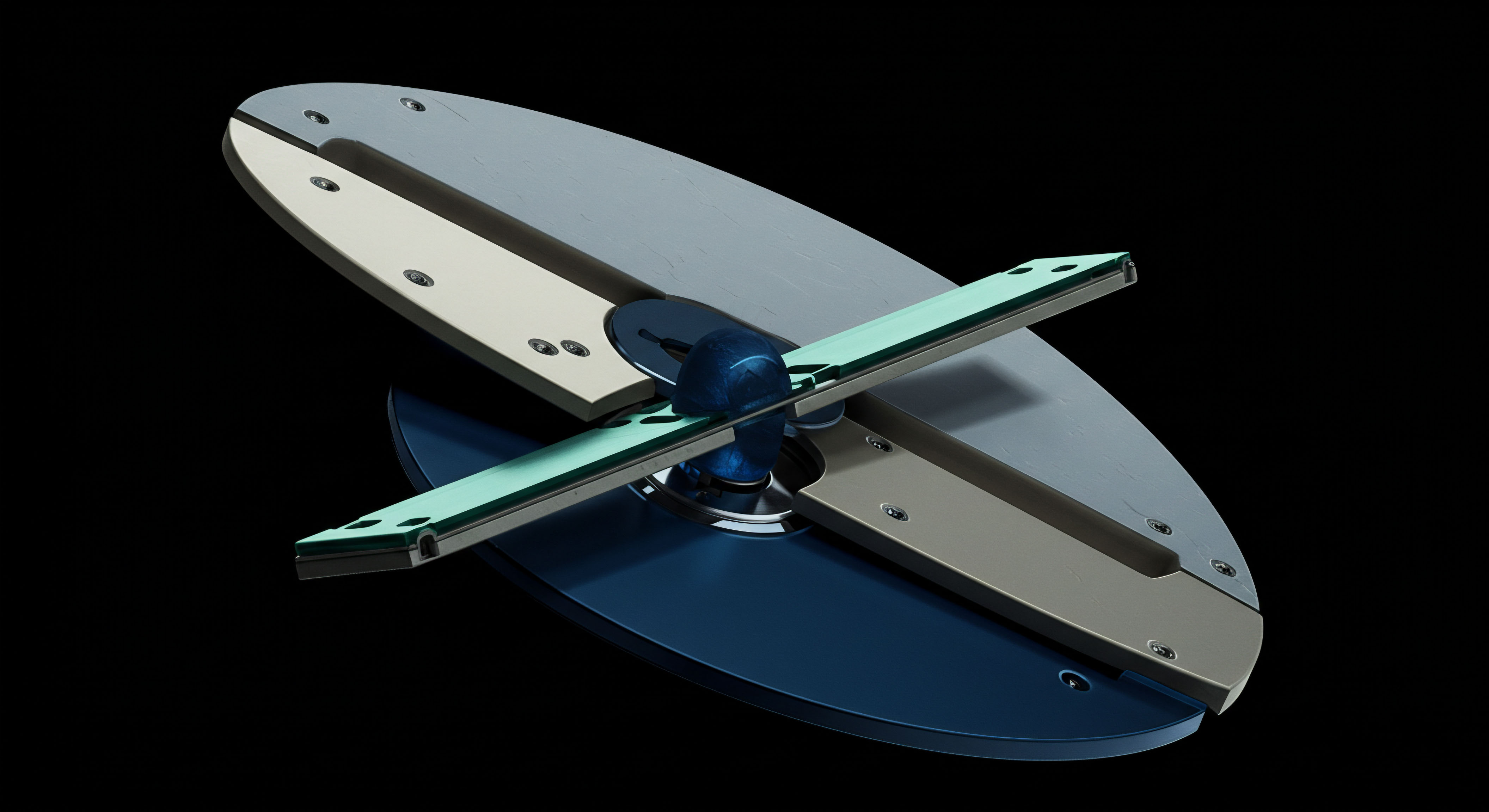

Strategy

Selecting a latency reduction strategy is an exercise in aligning technological capabilities with a firm’s specific operational goals and economic realities. The decision matrix extends far beyond a simple comparison of nanoseconds. It encompasses the entire lifecycle of a trading strategy, from development and deployment to maintenance and evolution. The primary vectors of this strategic trade-off are performance determinism, developmental agility, and total cost of ownership.

A firm’s latency reduction strategy is a direct reflection of its market-facing posture and its philosophy on the balance between raw speed and operational flexibility.

Performance and Determinism

The principal advantage of a hardware-based approach, particularly with FPGAs and ASICs, is deterministic latency. Because the logic is etched into the silicon, the time taken to process a market data packet or formulate an order is highly consistent, with minimal variance, often called “jitter.” This predictability is invaluable for strategies that rely on consistent, repeatable performance, especially during periods of high market volatility. A software system, even one using kernel bypass, is subject to the inherent non-determinism of a general-purpose operating system, including context switches and process scheduling, which can introduce unpredictable delays.

Hardware excels at parallel processing. An FPGA can be designed to perform multiple tasks simultaneously ▴ such as parsing data from different markets, running risk checks, and preparing orders ▴ whereas a CPU-based software system must often execute these tasks sequentially. This parallelism provides a significant speed advantage for complex, multi-leg strategies.

Developmental Agility and Flexibility

The strategic advantage shifts toward software when considering flexibility and time-to-market. Developing and modifying trading logic in a high-level programming language like C++ or Java is significantly faster and requires a more readily available skillset than designing for hardware. A software-based system allows for rapid iteration, enabling a firm to adapt its strategies to changing market conditions or new exchange protocols in a matter of days or even hours.

In contrast, FPGA development is a more protracted and specialized process. It involves writing code in a Hardware Description Language (HDL), followed by a lengthy compilation and testing cycle that can take weeks. Any change to the trading logic requires this entire process to be repeated.

ASICs represent the most extreme point on this spectrum; once fabricated, they are immutable. This rigidity makes hardware solutions less suitable for strategies that are experimental or require frequent adjustments.

Total Cost of Ownership and Scalability

The economic considerations of the hardware versus software trade-off are multifaceted. Initially, software-based systems present a lower barrier to entry. They run on commodity servers, and the primary cost is in developer talent. Hardware solutions, conversely, require significant upfront investment in specialized FPGA cards or the astronomical non-recurring engineering (NRE) costs associated with designing and manufacturing an ASIC.

The analysis of total cost of ownership (TCO) reveals a more complex picture. While the initial outlay for hardware is high, it can lead to lower operational costs in terms of power consumption and physical footprint for a given level of performance. Furthermore, the maintenance of FPGAs requires specialized hardware engineers, which can be a recurring and significant expense. Scalability also differs.

A software system can often be scaled by adding more servers, a relatively straightforward process. Scaling a hardware-based system may involve a more complex redesign of the FPGA architecture or even a new ASIC, representing a substantial long-term investment.

The following table provides a strategic comparison of these approaches across key decision-making criteria:

| Criterion | Software-Based Approach | FPGA-Based Approach | ASIC-Based Approach |

|---|---|---|---|

| Ultimate Latency | Good (microseconds) | Excellent (sub-microsecond) | Exceptional (nanoseconds) |

| Latency Jitter | Higher / Less predictable | Low / Highly predictable | Lowest / Deterministic |

| Development Time | Fast (days/weeks) | Moderate (weeks/months) | Very Slow (months/years) |

| Flexibility to Change | High | Moderate | None (immutable) |

| Initial Cost | Low | High | Extremely High |

| Required Expertise | Software Engineering | Hardware Engineering (HDL) | IC Design, Verification |

Execution

The execution of a latency reduction strategy requires a granular understanding of the specific technical steps and resource commitments involved. Moving from a theoretical choice to a functional system involves navigating a complex landscape of specialized technologies, development methodologies, and operational protocols. The path taken, whether through silicon or software, dictates the composition of the technical team, the project timeline, and the ultimate performance ceiling of the trading system.

The Operational Playbook for Implementation

Deploying a low-latency solution is a multi-stage process that differs significantly between hardware and software paradigms. Each path has a distinct operational playbook.

Software-Centric Implementation

A software-based approach prioritizes the optimization of the entire application and operating system stack. The execution plan typically follows these steps:

- Hardware Selection ▴ Procure high-performance commodity servers with the latest multi-core CPUs, maximum cache, and high-speed memory.

- NIC Selection and Configuration ▴ Choose a Network Interface Card known for low-latency performance and robust driver support, such as those from Solarflare (now AMD) or Mellanox (now NVIDIA).

- Kernel Bypass Integration ▴ Implement a kernel bypass library like OpenOnload or DPDK. This is a critical step that allows the trading application to poll the NIC directly for incoming packets, avoiding the OS kernel’s interrupt-driven, higher-latency path.

- CPU Pinning and Isolation ▴ Configure the operating system to dedicate specific CPU cores to the trading application and its critical threads. This practice, known as CPU pinning, prevents the operating system from moving the process to another core, which would invalidate the CPU’s cache and introduce latency. Other non-essential OS tasks are isolated to separate cores.

- Code and Algorithm Optimization ▴ Profile the trading application code to identify and eliminate bottlenecks. This involves optimizing data structures for cache efficiency, writing “lock-free” algorithms to prevent threads from blocking each other, and meticulously managing memory to avoid delays.

- System Tuning ▴ Perform deep tuning of the server’s BIOS and OS settings. This includes disabling power-saving states, adjusting interrupt handling, and optimizing memory access parameters to favor speed over all other considerations.

Hardware-Centric Implementation (FPGA)

An FPGA-based project requires a fusion of hardware and software engineering disciplines from the outset.

- FPGA Platform Selection ▴ Choose an FPGA development board that meets the project’s requirements for logic capacity, on-board memory, and network connectivity. The AMD Alveo series is a common choice in the financial sector.

- Logic Design and HDL Coding ▴ The core trading logic is designed and written in a Hardware Description Language such as Verilog or VHDL. This code describes the electronic circuits that will perform the tasks of market data parsing, order book building, and strategy execution.

- High-Level Synthesis (HLS) ▴ Increasingly, firms use High-Level Synthesis tools that allow engineers to write algorithms in a higher-level language like C++ which is then compiled into HDL. This can accelerate development time, though often at the cost of some performance compared to hand-tuned HDL.

- Simulation and Verification ▴ Before programming the FPGA, the design is exhaustively tested in a software simulator. This verification stage is critical, as debugging on live hardware is significantly more difficult.

- Synthesis, Place, and Route ▴ The verified HDL code is run through a toolchain that synthesizes it into a low-level netlist, then “places” the logic gates onto the FPGA’s fabric and “routes” the connections between them. This process is computationally intensive and can take many hours or even days.

- Hardware Deployment and Integration ▴ The final binary file is loaded onto the FPGA. The device is installed in a server, often alongside a software component running on the host CPU that manages higher-level strategy decisions and communicates with the FPGA.

Quantitative Modeling and Data Analysis

The decision to invest in a particular latency reduction path must be supported by rigorous quantitative analysis. A key model is the Total Cost of Ownership (TCO) versus Performance Gain. This analysis projects costs over a multi-year horizon, factoring in initial development, hardware acquisition, specialized talent, and ongoing maintenance against the expected financial return from the latency improvement.

In the domain of low-latency trading, capital allocation decisions are guided by quantitative models that weigh the cost of nanoseconds against their potential revenue generation.

The following table presents a simplified TCO model for a hypothetical trading system deployment over three years. It illustrates the different cost structures inherent in each approach.

| Cost Component | Optimized Software | FPGA Solution | ASIC Solution |

|---|---|---|---|

| Initial Development (Year 1) | $500,000 | $1,500,000 | $15,000,000 |

| Hardware/Licensing (Year 1) | $100,000 | $750,000 | $5,000,000 (Mask Sets) |

| Annual Maintenance/Talent (Y2-3) | $400,000 | $800,000 | $1,000,000 |

| 3-Year Total Cost of Ownership | $1,400,000 | $3,850,000 | $22,000,000 |

| Typical Tick-to-Trade Latency | ~5 microseconds | ~500 nanoseconds | ~50 nanoseconds |

This model demonstrates the exponential increase in cost required to cross successive latency thresholds. The business case for an FPGA or ASIC solution depends on whether the revenue generated by the sub-microsecond performance advantage justifies the multimillion-dollar investment. For a small number of high-frequency trading firms operating latency arbitrage strategies, the answer is yes. For the majority of firms, a highly optimized software solution provides the most balanced return on investment.

References

- Krishnan, S. & El-Aawar, M. (2012). Using Solarflare OpenOnload to Achieve Extreme Low Latency on Red Hat Enterprise Linux 6. Red Hat, Inc.

- Herlihy, M. & Shavit, N. (2012). The Art of Multiprocessor Programming. Morgan Kaufmann.

- Harris, L. (2003). Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press.

- Béal, S. & Lehalle, C. A. (2021). Market Microstructure in Practice. World Scientific Publishing.

- Gommans, L. & Athanasopoulos, S. (2014). High Frequency Trading Acceleration using FPGAs. Proceedings of the 2014 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays.

- Michelogiannakis, G. & Papamichael, M. (2017). The Case for FPGAs in High-Frequency Trading. ACM SIGARCH Computer Architecture News.

- Lockhart, J. C. (2019). ASIC Design for High-Speed Trading ▴ A Cost-Benefit Analysis. Journal of Financial Technology.

- Podobas, A. & Själander, M. (2016). On the Use of FPGAs to Accelerate High-Frequency Trading. 2016 IEEE 18th International Conference on High Performance Computing and Communications.

Reflection

Calibrating the Engine of Execution

The exploration of hardware and software latency reduction reveals a fundamental principle of system design ▴ every architectural choice is a commitment to a specific operational philosophy. The decision is not a one-time technical selection but the establishment of a trajectory that will shape a firm’s capacity for adaptation, its cost structure, and its ultimate competitive posture. The constructed system, whether forged in the deterministic pathways of silicon or the dynamic adaptability of software, becomes a direct reflection of the organization’s strategic intent.

Considering these trade-offs compels a deeper introspection into a firm’s own operational DNA. What is the half-life of our trading strategies? Is our primary advantage derived from raw speed in stable, well-understood patterns, or from the intellectual agility to devise and deploy novel logic in evolving markets?

The answer to these questions provides the necessary lens through which to evaluate the metrics of latency, cost, and flexibility. The optimal system is not the one with the lowest possible latency in absolute terms, but the one that achieves a state of equilibrium, where its performance profile is precisely calibrated to the financial objectives it is designed to achieve.

Glossary

Latency Reduction

Operating System

Asic

Kernel Bypass

Latency Reduction Strategy

Total Cost of Ownership

Deterministic Latency

Total Cost