Concept

The decision between deploying Field-Programmable Gate Arrays (FPGAs) and optimized Central Processing Units (CPUs) for latency-sensitive computations is a fundamental architectural choice. It dictates the operational physics of a trading system. The core of this decision lies in understanding how each technology processes information. A CPU, a general-purpose processor, operates on a set of predefined instructions.

It executes tasks sequentially, albeit at very high clock speeds and with sophisticated techniques like out-of-order execution to create a semblance of parallelism. Its strength is its versatility; it can run a complex operating system, manage user interfaces, and execute a trading model written in a high-level language. This versatility, however, comes at the cost of indeterminacy. The path a task takes through a modern CPU is subject to the whims of the operating system scheduler, cache misses, and resource contention from other processes. For latency-critical applications, this introduces jitter ▴ unpredictable variations in processing time ▴ which can be the difference between capturing an alpha and a missed opportunity.

FPGAs, in contrast, are not processors in the conventional sense. They are integrated circuits containing a matrix of configurable logic blocks and programmable interconnects. Instead of executing a sequence of instructions, an FPGA is configured to become the circuit that performs a specific task. This is a crucial distinction.

A developer using a Hardware Description Language (HDL) is not writing software; they are designing a digital circuit. This circuit can be massively parallel, with different sections of the chip performing different parts of a calculation simultaneously, all synchronized to a single clock. The result is a system where the latency of an operation is deterministic down to the nanosecond. There is no operating system, no instruction fetching, and no resource contention in the traditional sense.

The data flows through a custom-built pipeline, and the time it takes to traverse that pipeline is fixed and predictable. This deterministic low latency is the primary allure of FPGAs in domains like high-frequency trading (HFT), real-time signal processing, and network infrastructure.

Strategy

Choosing between FPGAs and optimized CPUs is a strategic decision that extends beyond raw performance metrics. It involves a careful evaluation of time-to-market, development costs, operational flexibility, and the nature of the competitive edge being sought. A CPU-based approach offers the most rapid path to deployment. The vast ecosystem of high-level programming languages like C++ and Python, coupled with extensive libraries and development tools, allows for quick iteration and implementation of trading logic.

This is particularly advantageous in strategies that are frequently modified or in markets where the sources of alpha are transient. The ability to quickly adapt a model to changing market conditions is a significant strategic advantage that CPUs facilitate.

The strategic choice between FPGAs and CPUs hinges on a trade-off between the raw, deterministic speed of custom hardware and the adaptive agility of software.

An FPGA strategy, on the other hand, is a long-term investment in creating a durable competitive advantage through superior latency. The development process is substantially more complex and resource-intensive. It requires a specialized skillset in hardware design and verification, and the development cycles are measured in months or even years, rather than weeks. The high initial cost of FPGA development, both in terms of hardware and engineering talent, presents a significant barrier to entry.

However, for strategies that are stable and where a few microseconds of latency advantage can be consistently monetized, the return on this investment can be substantial. The decision to pursue an FPGA-based solution is a declaration that the core of a firm’s strategy is based on speed, and that the firm is willing to bear the high fixed costs to establish a technological moat around its operations.

Comparative Analysis of Strategic Factors

The strategic calculus for selecting between FPGAs and CPUs can be systematically evaluated across several key dimensions. Each choice presents a distinct profile of advantages and disadvantages that must be aligned with a firm’s overarching business objectives and technological capabilities.

Development and Operational Trade-Offs

The following table provides a comparative overview of the strategic factors influencing the choice between FPGAs and optimized CPUs for low-latency applications:

| Factor | Optimized CPU | FPGA |

|---|---|---|

| Processing Latency | Low, but subject to jitter from OS, cache misses, and resource contention. | Ultra-low and deterministic, measured in nanoseconds. |

| Development Time | Relatively short; rapid iteration is possible. | Long; requires extensive design, simulation, and verification. |

| Development Cost | Lower; leverages a large pool of software developers and mature tools. | High; requires specialized hardware engineers and expensive EDA software. |

| Flexibility / Adaptability | High; algorithms can be changed quickly by deploying new software. | Low; changes to the logic require a full hardware redesign and synthesis cycle. |

| Power Efficiency | Generally lower, as general-purpose architecture has overhead. | Higher for specific, parallelizable tasks as only necessary logic is implemented. |

| Time-to-Market | Fast; ideal for strategies that need to be deployed quickly. | Slow; a long-term investment for durable, latency-sensitive strategies. |

The Hybrid Approach a Synthesis of Agility and Speed

A growing number of sophisticated trading firms are adopting a hybrid approach, seeking to combine the strengths of both CPUs and FPGAs. In this model, the FPGA is used for tasks that are both latency-critical and computationally stable. This often includes:

- Market Data Processing ▴ Decoding and normalizing raw exchange data feeds at the network edge.

- Order Execution ▴ Managing the placement and cancellation of orders with the lowest possible latency.

- Risk Checks ▴ Implementing pre-trade risk controls directly in hardware to minimize their impact on latency.

The higher-level trading logic, which is more complex and subject to frequent change, remains on a CPU. This allows strategists and developers to continue to work in a familiar, high-level environment, while the most latency-sensitive parts of the trade lifecycle are accelerated in hardware. This hybrid architecture represents a sophisticated compromise, balancing the need for speed with the practical realities of strategy development and adaptation.

Execution

The execution of a low-latency strategy on either an FPGA or an optimized CPU requires a disciplined and systematic approach. The choice of platform has profound implications for the entire development lifecycle, from talent acquisition to testing and deployment. A CPU-centric execution path leverages a well-established ecosystem. The process typically begins with a model developed in a language like Python for its ease of use and extensive data analysis libraries.

This model is then translated into a high-performance language like C++ for production deployment. The focus of the optimization effort is on minimizing software-induced latency. This involves techniques such as kernel bypass networking, CPU pinning to avoid context switches, and careful memory management to ensure that critical data resides in the fastest levels of the CPU cache. The testing and verification process is relatively straightforward, relying on standard software development practices like unit testing, integration testing, and simulation against historical data.

Executing a low-latency strategy is an exercise in controlling variables, whether they are lines of code in a CPU or logic gates in an FPGA.

Executing on an FPGA is a fundamentally different discipline, more akin to designing a custom microchip than to writing software. The process begins with a detailed architectural specification of the trading logic. This specification is then implemented using an HDL like Verilog or VHDL. The development process is dominated by simulation and verification.

Given that a bug in an FPGA design can have catastrophic consequences, a significant portion of the development effort is dedicated to creating a comprehensive test bench that can simulate the behavior of the design under a wide range of conditions. High-Level Synthesis (HLS) tools, which allow developers to write C++ code that is then synthesized into an HDL, have made FPGA development more accessible, but they do not eliminate the need for a deep understanding of hardware design principles. Deployment involves synthesizing the HDL code into a bitstream that is then loaded onto the FPGA. Any subsequent change to the logic requires this entire process to be repeated.

A Comparative Look at Implementation

The practical steps involved in implementing a low-latency trading strategy differ significantly between CPUs and FPGAs. Understanding these differences is critical for project planning, resource allocation, and risk management.

The Development Lifecycle a Tale of Two Paradigms

The following table outlines the typical stages of a development project for both a CPU-based and an FPGA-based low-latency system:

| Development Stage | Optimized CPU Implementation | FPGA Implementation |

|---|---|---|

| 1. Requirements & Algorithm Design | Algorithm defined in a high-level language (e.g. Python, MATLAB), focusing on logic and mathematical correctness. | Architecture defined with a focus on parallelism, pipelining, and fixed-point arithmetic. Hardware constraints are a primary consideration. |

| 2. Implementation | Code written in C++ or Java. Focus on efficient use of data structures, algorithms, and system calls. | Code written in an HDL (Verilog/VHDL) or HLS (C++). Focus on designing a digital circuit. |

| 3. Optimization | Software profiling to identify bottlenecks. Techniques include CPU pinning, cache optimization, and kernel bypass. | Manual placement and routing of logic blocks. Pipelining to increase throughput. Clock frequency optimization. |

| 4. Verification & Testing | Unit tests, integration tests, and simulation. Standard software debugging tools are used. | Extensive simulation in a test bench. Formal verification methods may be used. Debugging is done through simulation and hardware logic analyzers. |

| 5. Deployment | Compilation and deployment of the executable file. Can be done in minutes. | Synthesis, place-and-route, and bitstream generation. This process can take hours or even days. |

The Human Element the Required Skillsets

The choice between CPUs and FPGAs also dictates the type of engineering talent required. A successful low-latency trading team is a multidisciplinary entity, but the core competencies shift depending on the chosen hardware platform.

- CPU-Based Teams ▴ These teams are typically composed of software engineers with deep expertise in low-level C++ programming, operating systems, and computer networks. They are skilled in identifying and eliminating sources of latency in a software stack. Quantitative analysts with strong programming skills are also a key component, responsible for developing and backtesting the trading models.

- FPGA-Based Teams ▴ In addition to quantitative analysts, these teams require hardware engineers with a background in digital design and experience with HDLs and FPGA development tools. These engineers are a rare and expensive resource. The collaboration between the hardware engineers who implement the logic and the quants who design it is critical to the success of an FPGA project.

Ultimately, the decision to use FPGAs, CPUs, or a hybrid approach is a reflection of a firm’s strategic priorities. There is no single correct answer. The optimal choice depends on a careful and honest assessment of the firm’s trading strategy, its tolerance for risk, its access to capital, and its ability to attract and retain the specialized talent required to compete at the highest levels of the market.

References

- Harris, S. L. & Harris, D. M. (2016). Digital Design and Computer Architecture ▴ ARM Edition. Morgan Kaufmann.

- O’Hara, M. (1995). Market Microstructure Theory. Blackwell Publishing.

- Maxfield, C. (2004). The Design Warrior’s Guide to FPGAs ▴ Devices, Tools and Flows. Newnes.

- Lehalle, C. A. & Laruelle, S. (2013). Market Microstructure in Practice. World Scientific Publishing Company.

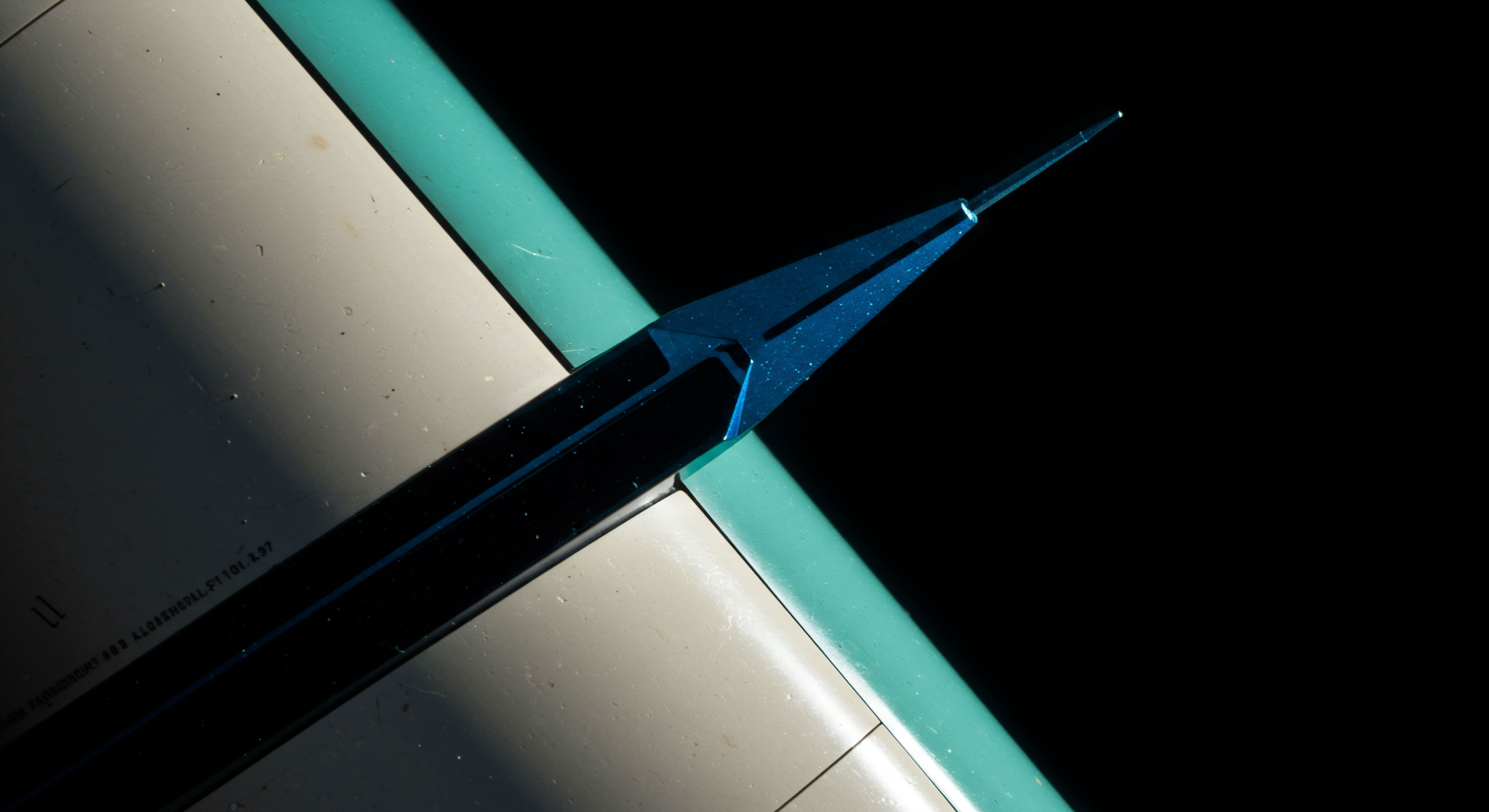

- Aldridge, I. (2013). High-Frequency Trading ▴ A Practical Guide to Algorithmic Strategies and Trading Systems. John Wiley & Sons.

- Patterson, D. A. & Hennessy, J. L. (2017). Computer Organization and Design ▴ The Hardware/Software Interface. Morgan Kaufmann.

- Cottle, P. (2005). FPGAs in Finance. ACM Queue, 3(7), 44-51.

- Cong, J. & Pan, P. (2001). Interconnect estimation and planning for deep submicron designs. ACM Transactions on Design Automation of Electronic Systems (TODAES), 6(3), 289-313.

- Trimberger, S. M. (2015). Three Ages of FPGAs ▴ A Retrospective on the First Thirty Years of FPGA Technology. Proceedings of the IEEE, 103(3), 318-331.

- Goeders, J. & Rutenbar, R. A. (2013). Zipline ▴ A high-level synthesis engine for high-performance data-parallel applications on FPGAs. 2013 International Conference on Field-Programmable Technology (FPT), 1-8.

Reflection

The examination of FPGAs versus optimized CPUs for latency processing moves beyond a simple technical comparison. It compels a deeper introspection into the foundational principles of an entire trading operation. The selection of a hardware platform is an expression of a firm’s core philosophy ▴ a tangible commitment to a particular theory of market interaction. Does the operational mandate prioritize the raw, immutable velocity of a custom-designed circuit, seeking an advantage in the very physics of the market?

Or does it favor the cerebral agility of software, allowing for rapid adaptation and strategic repositioning in a constantly shifting landscape? The knowledge of these trade-offs is a critical component in the construction of a superior operational framework. The true edge is found not in the silicon itself, but in the deliberate and informed alignment of technology, strategy, and human capital. This alignment transforms a collection of high-performance components into a coherent, intelligent system capable of achieving a sustained competitive advantage.

Glossary

Cpu

Fpga

Hardware Description Language

High-Frequency Trading

Low Latency

Time-To-Market

Between Fpgas

Hybrid Architecture

Kernel Bypass

Cpu Pinning