Concept

An institution’s decision to implement a high-frequency scoring protocol is a commitment to operate at the physical limits of information transmission and processing. This endeavor moves beyond the realm of software optimization into the domain of systems architecture, where every component choice is a declaration of strategic intent. The core challenge resides in the immutable nature of financial markets a high-velocity, fragmented data environment where the value of information decays in microseconds. A scoring protocol, in this context, is a sophisticated decision-making engine designed to evaluate and act upon market signals before they are universally recognized and priced into the asset.

The technological prerequisites for such a system are best understood as an integrated chassis built upon three foundational pillars ▴ compute, network fabric, and data architecture. These elements must function as a single, coherent unit, engineered to minimize latency and eliminate non-deterministic behavior. The system’s performance is measured by its end-to-end latency, the time elapsed from receiving a market data packet to transmitting an order.

Success is defined by the system’s ability to execute this cycle with predictable consistency, a quality known as deterministic latency. Fluctuations in processing time, or jitter, introduce uncertainty and risk, undermining the protocol’s strategic purpose.

A high-frequency scoring system is an engineered solution to the physical problem of information decay in financial markets.

The Physics of Market Interaction

Modern electronic markets are a collection of disparate liquidity venues, each generating its own stream of data. A high-frequency system must ingest these parallel streams, construct a coherent view of the market, and act upon it. This requires a technological framework capable of processing immense volumes of data with extreme prejudice. The primary adversary in this environment is latency, which exists in multiple forms.

- Network Latency ▴ The time required for light to travel through fiber optic cables from the exchange’s matching engine to the firm’s servers. This is governed by physical distance, making colocation a fundamental prerequisite.

- Processing Latency ▴ The time consumed by the system’s internal components to parse data, execute the scoring logic, and formulate an order. This is where architectural choices have the most significant impact.

- Serialization Latency ▴ The overhead associated with converting data structures into a format suitable for network transmission or inter-process communication. Inefficient serialization can introduce significant delays.

Each of these latency components must be rigorously measured, managed, and minimized. The objective is to build a processing pipeline where every stage is optimized for speed and predictability, creating a direct, unimpeded path from market signal to market action.

Strategy

Architecting a system for a high-frequency scoring protocol involves a series of strategic trade-offs between speed, flexibility, and development cost. The central strategic decision is where to place the computational logic. The choice determines the system’s fundamental performance characteristics and its capacity to evolve with changing market dynamics and strategic objectives. The spectrum of options ranges from purely software-based systems to hybrid models that offload critical functions onto specialized hardware.

Compute Strategy and Hardware Acceleration

The scoring logic, the core of the protocol, can be executed on different types of processors. This choice is the most critical strategic decision in the system’s design. A CPU-based software approach offers maximum flexibility and rapid development cycles. A hardware-based approach using Field-Programmable Gate Arrays (FPGAs) provides the lowest possible latency and the highest degree of determinism.

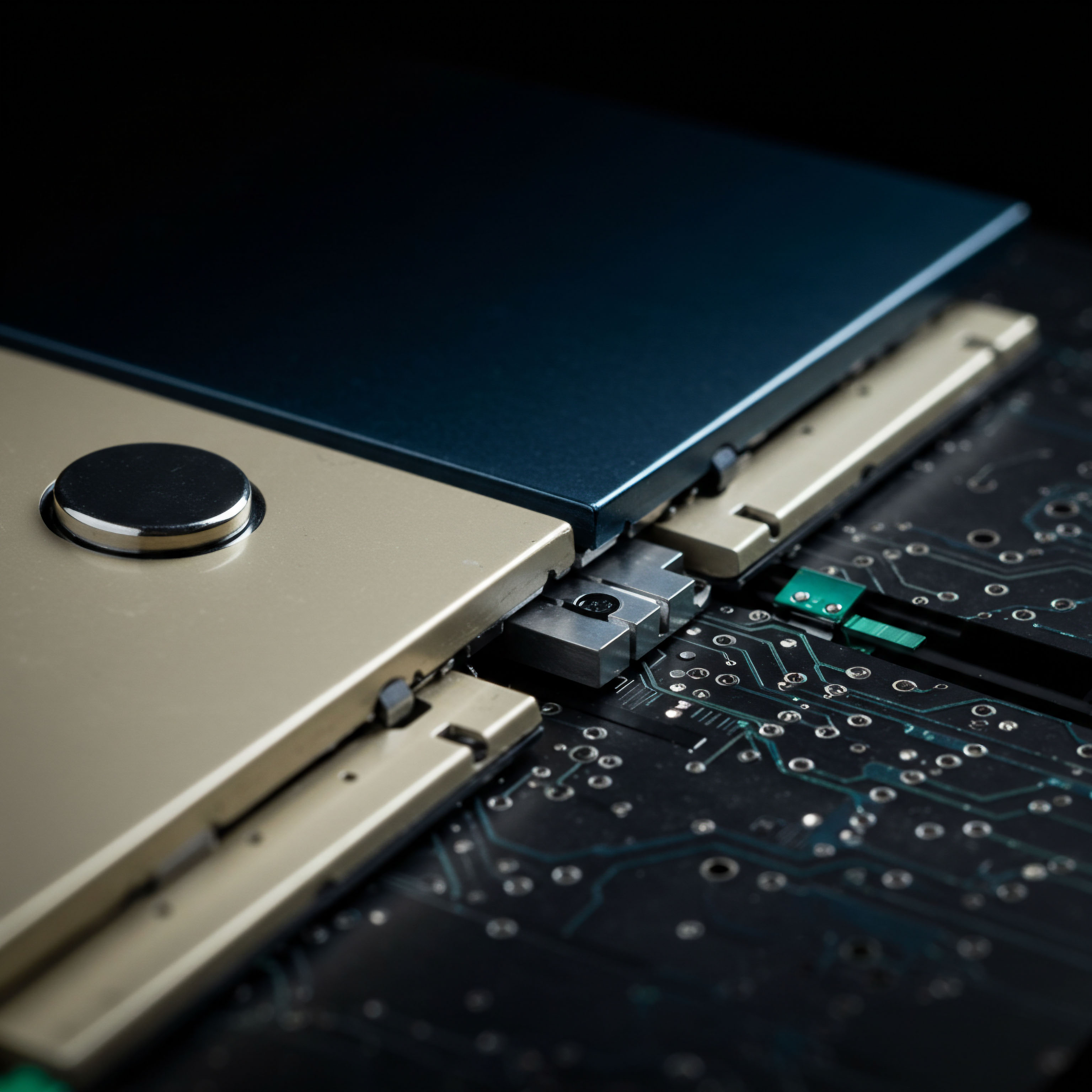

The strategy of hardware offloading involves moving specific, latency-sensitive tasks from the CPU to an FPGA. This could include network packet processing, market data parsing, and the execution of simple risk checks. By handling these tasks in dedicated silicon, the CPU is freed to focus on the more complex aspects of the scoring algorithm, reducing overall system jitter and lowering end-to-end latency.

| Architecture | Latency Profile | Determinism | Development Velocity | Operational Flexibility |

|---|---|---|---|---|

| CPU (Software) | Moderate to High (microseconds) | Low (subject to OS, cache misses) | High | High |

| GPU (Hybrid) | Low (for parallel tasks) | Moderate | Moderate | Moderate |

| FPGA (Hardware) | Ultra-Low (nanoseconds) | High (deterministic path) | Low | Low |

What Is the Optimal Network Architecture?

The network architecture is the system’s interface to the market. The strategy here centers on creating the shortest, most direct path to the exchange’s matching engine. Colocation, placing the firm’s servers within the same data center as the exchange, is the baseline requirement. The next layer of optimization involves the physical network and the software stack that controls it.

A sophisticated strategy employs kernel bypass networking. This technique allows the application to communicate directly with the network interface card (NIC), bypassing the operating system’s network stack. This eliminates a significant source of latency and jitter, providing a more direct and predictable data path for market information and outgoing orders. The choice of network protocol and its implementation also plays a critical role, with custom UDP-based protocols often favored over TCP for their lower overhead.

Execution

The execution phase translates architectural strategy into a functioning, high-performance system. This requires meticulous attention to detail at every level of the technological stack, from the physical hardware to the application software. The goal is to assemble a set of components that collectively achieve the latency and determinism targets defined by the strategy.

A system’s performance is ultimately defined by its slowest component; therefore, no part of the execution stack can be left unoptimized.

Core Infrastructure Prerequisites

The foundation of the system is the physical hardware and its connection to the market. This is the chassis upon which all other components are built.

- Server Hardware ▴ Servers must be specified with high-frequency performance in mind. This includes CPUs with the highest available clock speeds and large L3 caches, high-speed RAM, and a minimalist hardware configuration to reduce potential points of failure and latency.

- Network Interface Cards (NICs) ▴ Specialized NICs that support kernel bypass and hardware-level packet timestamping (PTP – Precision Time Protocol) are essential. These features are critical for reducing OS-induced latency and accurately measuring network transit times.

- FPGA Acceleration Cards ▴ Where the strategy calls for it, FPGA cards are integrated into the servers. These cards house the hardware-based logic for tasks like feed handling and order entry, offering processing latencies measured in nanoseconds.

- Direct Market Access (DMA) ▴ The system requires the lowest-latency connectivity provided by the exchange. This typically involves a 10Gbps or faster direct fiber connection to the exchange’s network switches.

Software and Application Logic

The software layer is where the scoring protocol’s intelligence resides. The execution of this logic must be as efficient as the underlying hardware.

Application code is often written in C++ for its proximity to the hardware and its predictable performance characteristics. The use of Java, while common in enterprise systems, introduces the risk of non-deterministic garbage collection pauses, which are unacceptable in a low-latency environment. The software design must emphasize mechanical sympathy, an approach where the code is structured to align with the way the underlying hardware operates. This includes practices like using lock-free data structures to avoid contention between threads and optimizing memory access patterns to maximize cache utilization.

| Process Stage | Technology | Typical Latency (μs) |

|---|---|---|

| Market Data Ingress (Wire to App) | Kernel Bypass NIC, FPGA Parser | 0.5 – 2.0 |

| Scoring Logic Execution | Optimized C++, High-Clock CPU | 1.0 – 5.0 |

| Risk Check & Order Formulation | FPGA or CPU | 0.2 – 1.5 |

| Order Egress (App to Wire) | Kernel Bypass NIC | 0.5 – 2.0 |

| Total End-to-End Latency | 2.2 – 10.5 |

How Is System Performance Verified?

Continuous performance monitoring is a prerequisite for maintaining a high-frequency scoring protocol. The system must be instrumented to provide high-resolution, real-time telemetry on every aspect of its operation. This includes nanosecond-precision timestamps at every stage of the order lifecycle, from packet arrival to order acknowledgment.

This data is used to verify that the system is operating within its latency budget and to identify any sources of unexpected jitter. The ability to measure is the ability to manage, and in the world of high-frequency trading, management is a continuous process of optimization.

References

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- Lixandru, Alexandru. “Efficient Architectures for Low Latency and High Throughput Trading Systems on the JVM.” Informatica Economică, vol. 17, no. 3, 2013, pp. 60-71.

- Moallemi, Ciamac. “High-Frequency Trading and Modern Market Microstructure.” Columbia University, 2012.

- Lockwood, John. “A Low-Latency Library in FPGA Hardware for High-Frequency Trading (HFT).” Presentation at Hot Interconnects 2012.

- Zalani, Aniruddha. “Low-Latency Machine Learning for Options Pricing ▴ High-Speed Models and Trading Performance.” Journal of Computer Science and Technology Studies, 2025.

Reflection

Assembling the technological prerequisites for a high-frequency scoring protocol establishes a formidable operational capability. It provides the institution with a structural advantage, an ability to act within timeframes inaccessible to most market participants. This system, however, is a foundation, an execution engine. Its existence prompts a more profound strategic question ▴ what intelligence will guide it?

With the physical constraints of latency and determinism addressed, the limiting factor shifts from engineering to strategy. The quality of the scoring models, the sophistication of the risk management framework, and the capacity to generate novel alpha signals become the new frontiers of competition. The technological architecture provides the means of execution; the intellectual capital of the firm provides the reason. The true prerequisite, therefore, is a vision for how this speed will be converted into sustained, risk-managed performance.

Glossary

High-Frequency Scoring Protocol

Systems Architecture

Colocation

High-Frequency Scoring

Kernel Bypass Networking

Kernel Bypass

Fpga Acceleration

Direct Market Access

Scoring Protocol

High-Frequency Trading