Concept

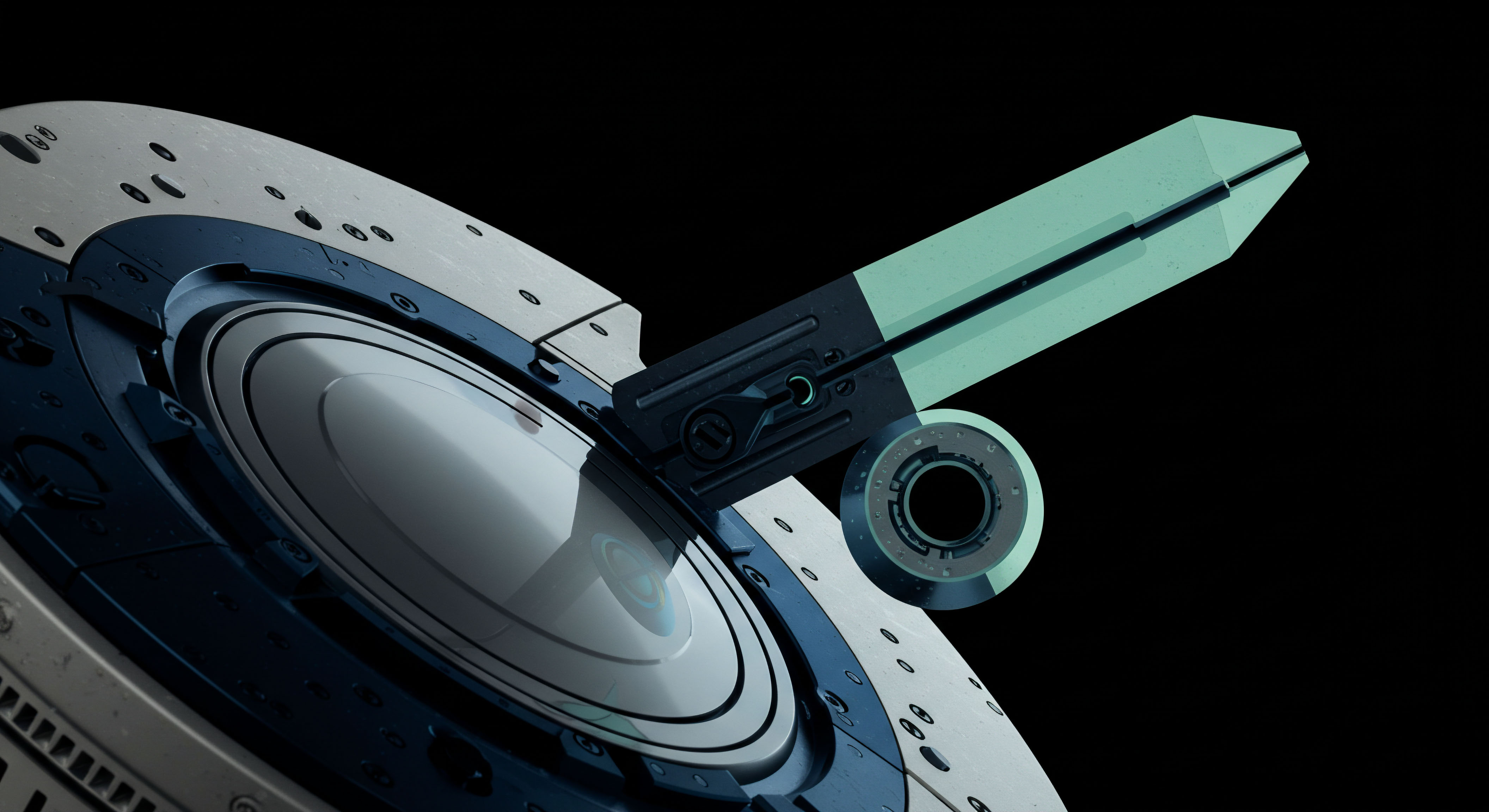

In the architecture of modern financial markets, latency is not an inconvenience; it is a fundamental dimension, as physical and consequential as price and volume. From a systems perspective, the flow of market data and orders is governed by the laws of physics, where the speed of light imposes a hard, non-negotiable limit on the velocity of information. High-Frequency Trading (HFT) is the practice of engineering systems to operate at the very edge of this physical boundary.

The entire discipline is predicated on a single, unyielding principle ▴ the participant who can receive information, process it, and act upon it with the lowest possible delay possesses a structural advantage. This advantage is not theoretical; it is a measurable, exploitable feature of the market landscape.

The operational challenge, therefore, becomes one of minimizing time by manipulating the two core components of delay ▴ distance and processing. Co-location directly addresses the variable of distance. By situating trading servers within the same data center as an exchange’s matching engine, firms effectively shorten the physical path that data must travel. This reduction, measured in miles, translates to a latency decrease measured in milliseconds, a vast expanse of time in the HFT domain.

It is the foundational step, a prerequisite for any competitive speed-based strategy. Placing equipment in these facilities is the process of entering the arena; without it, a firm is merely a spectator.

Co-location and FPGAs are engineering solutions designed to master the market’s physical dimensions of distance and processing time, thereby creating a structural advantage in trade execution.

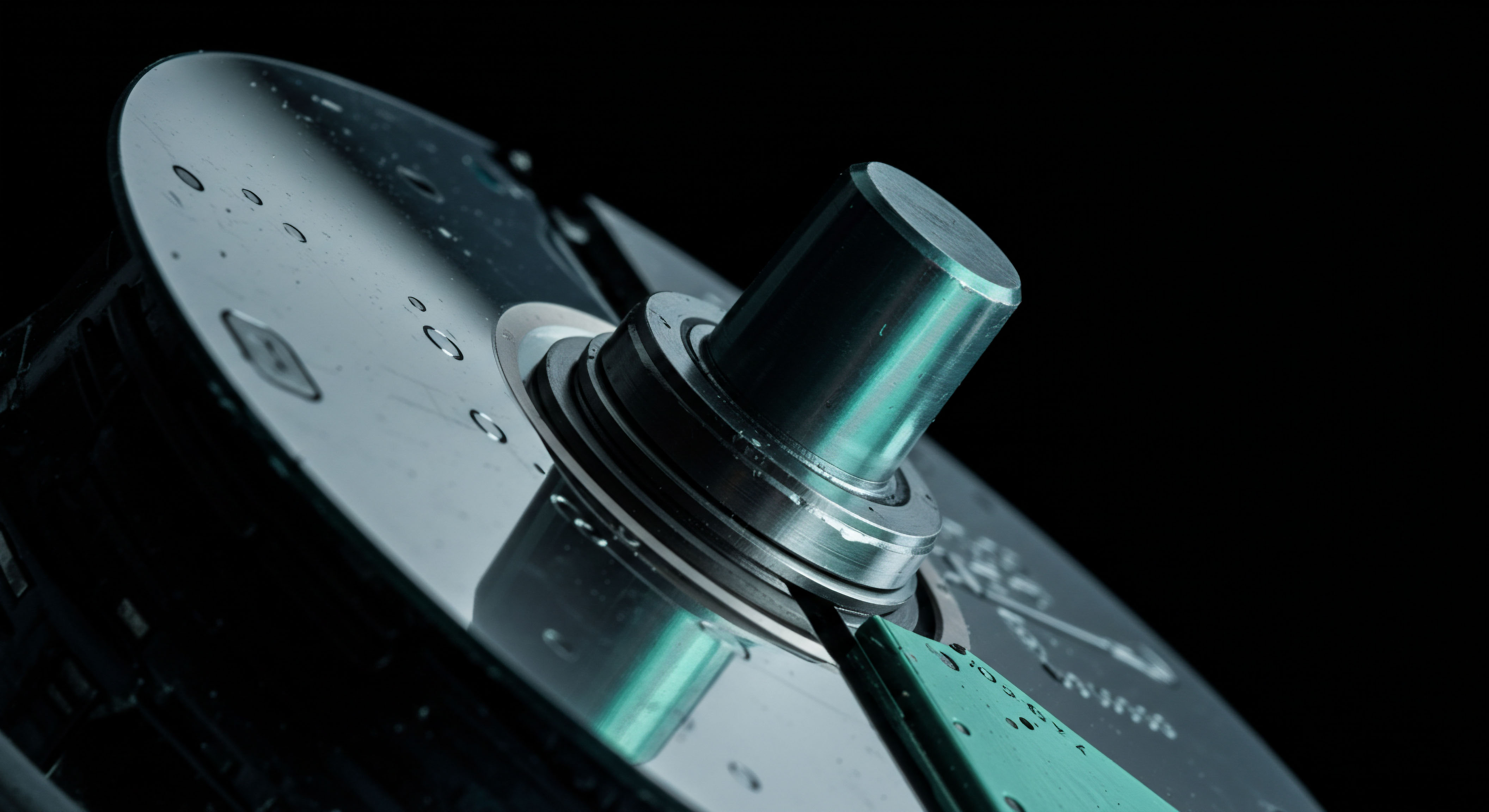

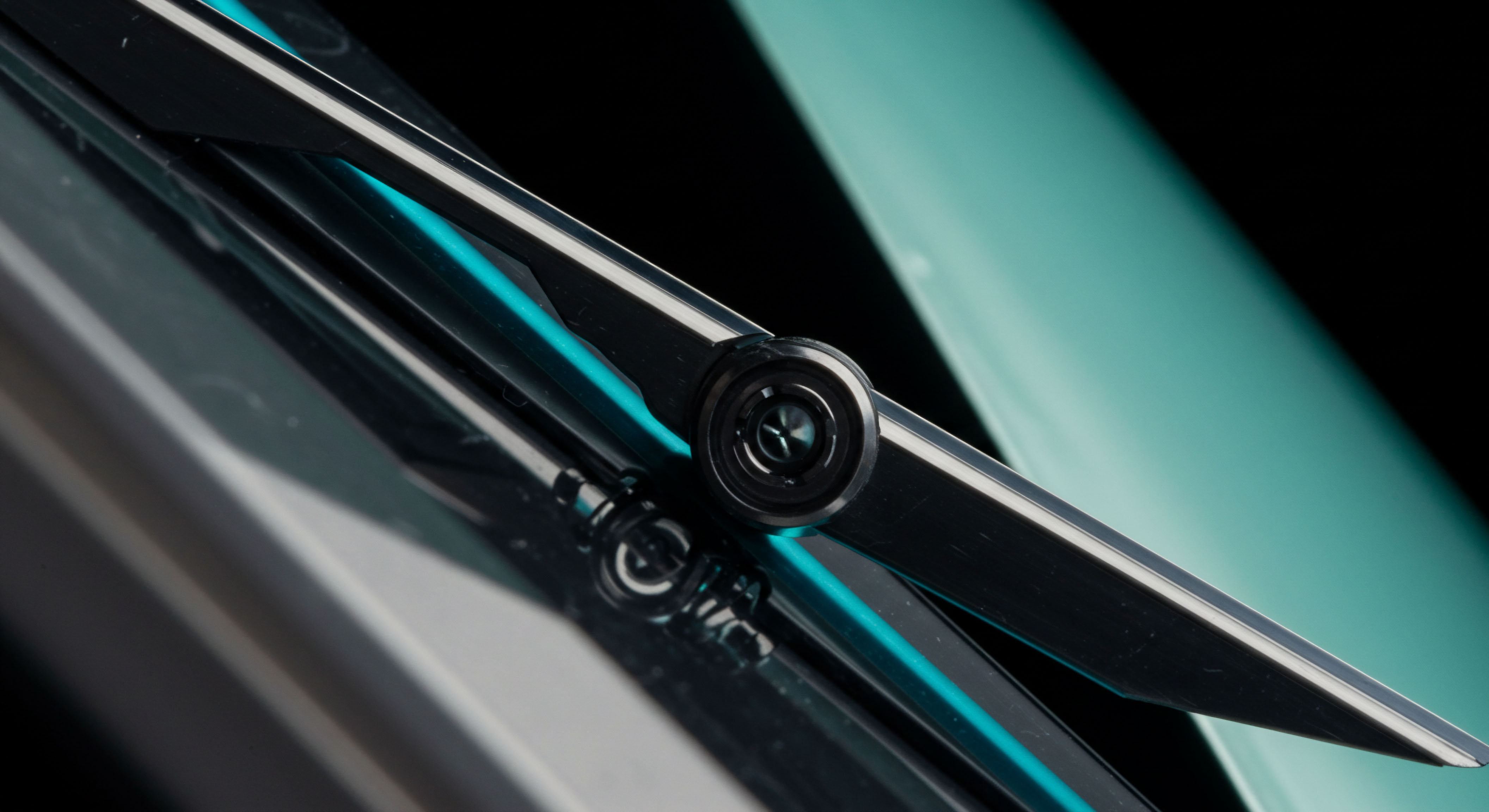

Field-Programmable Gate Arrays (FPGAs) address the second component of delay ▴ processing time. A standard Central Processing Unit (CPU) is a generalist, executing a sequence of instructions one after another. This sequential process, while flexible, introduces significant overhead and non-deterministic delays from the operating system and other software layers. An FPGA, in contrast, is a specialist forged in silicon.

It is a semiconductor device containing a matrix of configurable logic blocks connected through programmable interconnects. Instead of running software instructions, an FPGA is configured to be the algorithm. The trading logic is etched directly into the hardware circuits, allowing for the parallel processing of multiple tasks with deterministic, nanosecond-level response times. This transforms the act of computation from a sequential software process into a physical, parallel hardware function, eliminating layers of abstraction and their associated time costs.

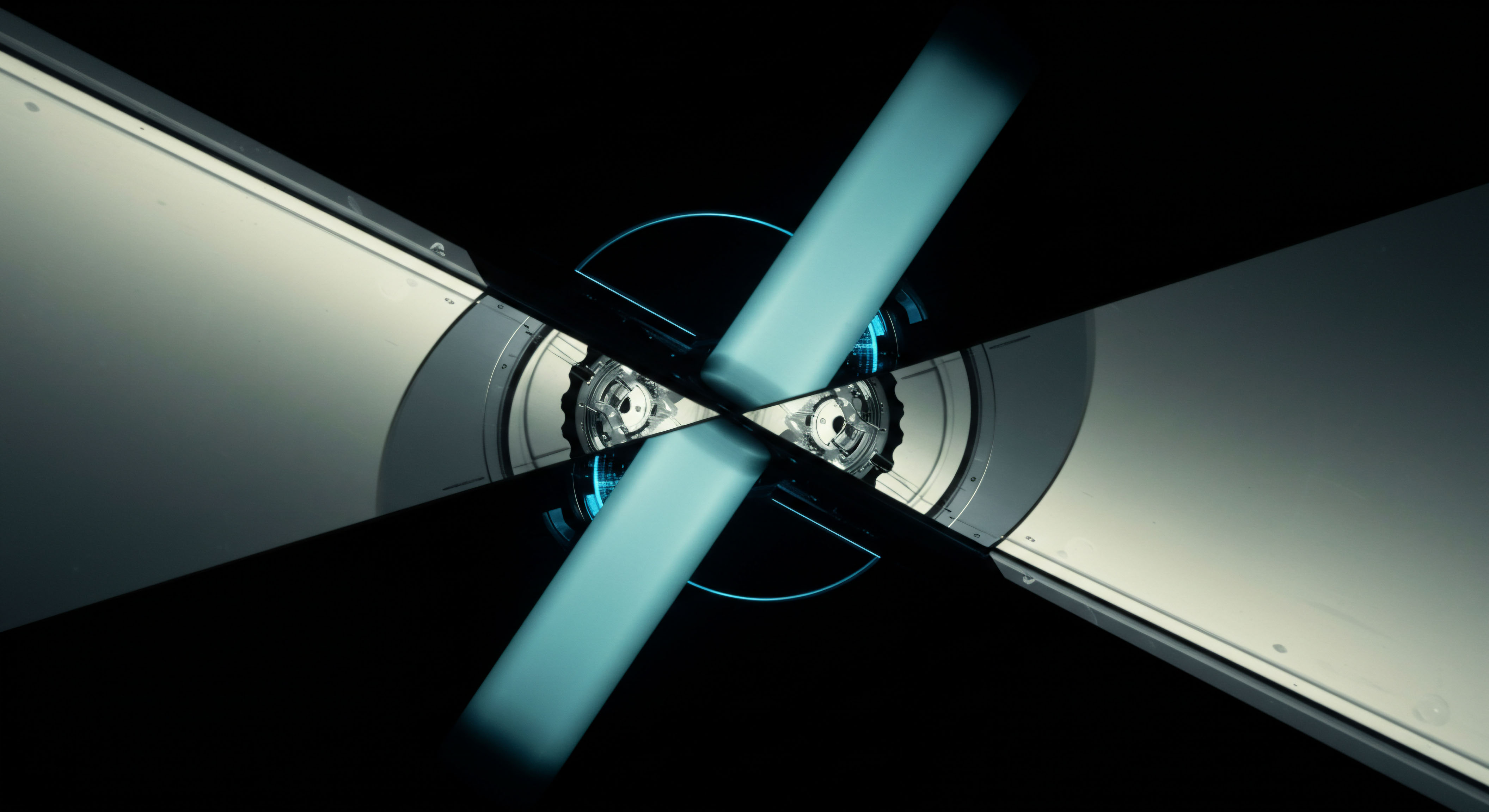

Viewing these two technologies through a unified lens reveals their symbiotic relationship. Co-location brings the trading firm’s hardware to the doorstep of the exchange. FPGAs ensure that once the market data crosses that doorstep, it is processed and acted upon with the absolute minimum of delay.

One technology conquers the physical space between the firm and the market, while the other conquers the processing time within the firm’s own server rack. Together, they form the primary axes of the low-latency framework, a system designed to operate at the forward boundary of what physics and technology permit.

Strategy

The strategic imperatives of High-Frequency Trading are born from the capabilities unlocked by its underlying technology. With latency engineered down to the nanosecond scale, a new set of market phenomena becomes visible and actionable. The most direct of these is Latency Arbitrage, a strategy that treats the financial market as a geographically distributed system where the law of one price is momentarily suspended due to the finite speed of information. It is a direct monetization of speed.

The Mechanics of Latency Arbitrage

Consider a security, such as an ETF, that is traded on two separate exchanges, A and B, located in different data centers. When a large institutional order to buy the ETF executes on Exchange A, the price on that venue ticks up. For a brief period, measured in microseconds, the price on Exchange B remains at the old, lower level. This discrepancy is a pure arbitrage opportunity.

An HFT firm co-located at both exchanges can detect the price change at Exchange A, race the public price feed that is traveling to Exchange B, and place an order to buy the ETF on Exchange B at the stale, lower price. The firm simultaneously sells the same amount on Exchange A at the new, higher price, capturing a risk-free profit. The success of this strategy is entirely dependent on the HFT firm’s ability to complete this sequence faster than any other market participant and faster than the exchanges’ own information dissemination systems can synchronize.

FPGAs are instrumental in this race. The process involves several distinct steps, each of which is accelerated by hardware implementation:

- Market Data Ingestion ▴ The FPGA’s dedicated hardware can listen directly to the raw market data feed from the exchange, bypassing the server’s network stack entirely. It can parse the exchange’s specific binary protocol at wire speed.

- Event Detection ▴ The logic programmed into the FPGA can identify the specific trade event on Exchange A that signals the arbitrage opportunity.

- Decision Logic ▴ A simplified version of the trading strategy, hardwired into the FPGA, makes the decision to execute the arbitrage.

- Order Generation ▴ The FPGA constructs the buy order for Exchange B and the sell order for Exchange A, formatting them according to the required FIX protocol or a more optimized, proprietary binary protocol.

- Pre-trade Risk Checks ▴ Critically, the FPGA performs mandatory risk checks (e.g. fat-finger checks, credit limit verification) in hardware, a process that would take orders of magnitude longer in software.

This entire tick-to-trade loop occurs in a deterministic time frame, often under a single microsecond. The strategy’s efficacy is a direct function of this engineered speed. Studies have shown that such arbitrage opportunities account for a substantial portion of trading costs for slower investors, representing a “latency arbitrage tax” on the market.

A Spectrum of Speed-Reliant Strategies

While latency arbitrage is the purest form of speed-based strategy, the technological framework of co-location and FPGAs enables a wider range of activities. Each strategy leverages the core benefits of low latency and determinism in a different way.

The strategic application of HFT technology extends beyond simple arbitrage to encompass sophisticated market making and statistical modeling, all unified by the core principle of minimizing execution delay.

The table below outlines several key HFT strategies and the specific roles that co-location and FPGAs play in their successful execution.

| HFT Strategy | Core Objective | Role of Co-Location | Role of FPGAs |

|---|---|---|---|

| Latency Arbitrage | Exploit temporary price discrepancies between correlated instruments or venues. | Minimizes the time to receive market data from one exchange and send orders to another. Essential for winning the race. | Provides the fastest possible processing of data and generation of orders, ensuring the entire trade logic executes before the arbitrage window closes. |

| Automated Market Making | Provide liquidity by simultaneously posting bid and ask orders, profiting from the spread. | Ensures the market maker’s quotes are always present at the top of the order book and can be updated instantly in response to market moves. | Allows for immediate reaction to trades that hit the market maker’s quotes (adverse selection protection) and rapid recalculation and placement of new quotes. Manages order book state with minimal delay. |

| Statistical Arbitrage | Use statistical models to identify short-term mispricings between securities with historical correlations. | Reduces the “slippage” between the model’s signal generation and the trade’s execution, ensuring the executed price is as close as possible to the price that generated the signal. | Can be used to pre-process and filter vast amounts of market data, feeding a cleaner, more relevant data stream to the software-based statistical model, thereby speeding up the signal generation process. |

| Liquidity Detection | Identify hidden liquidity (e.g. large iceberg orders) by sending small, probing orders (“pinging”). | Necessary for the probing orders to reach the exchange and return a response with the lowest possible round-trip time. | Manages the high volume of small orders and their responses, keeping track of the market’s microstructure with extreme precision. The deterministic nature is key for interpreting the timing of the responses. |

Execution

The execution of a high-frequency trading strategy is an exercise in applied physics and systems engineering. It involves the meticulous optimization of every component in the path from market event to trade execution. The theoretical advantage of a strategy is only realized through its flawless implementation in a physical and logical system designed for the single purpose of minimizing time.

The Operational Playbook of Physical Proximity

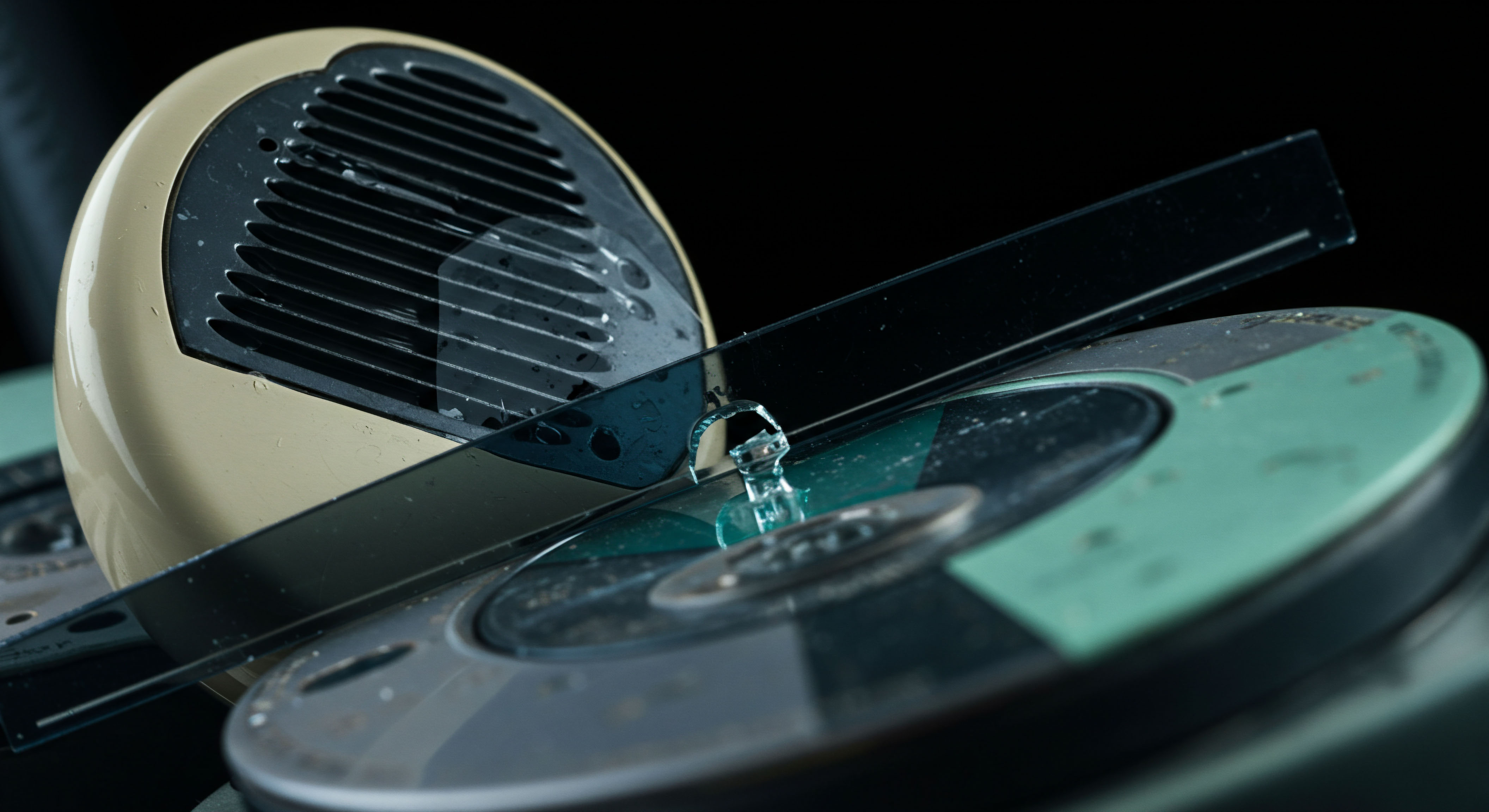

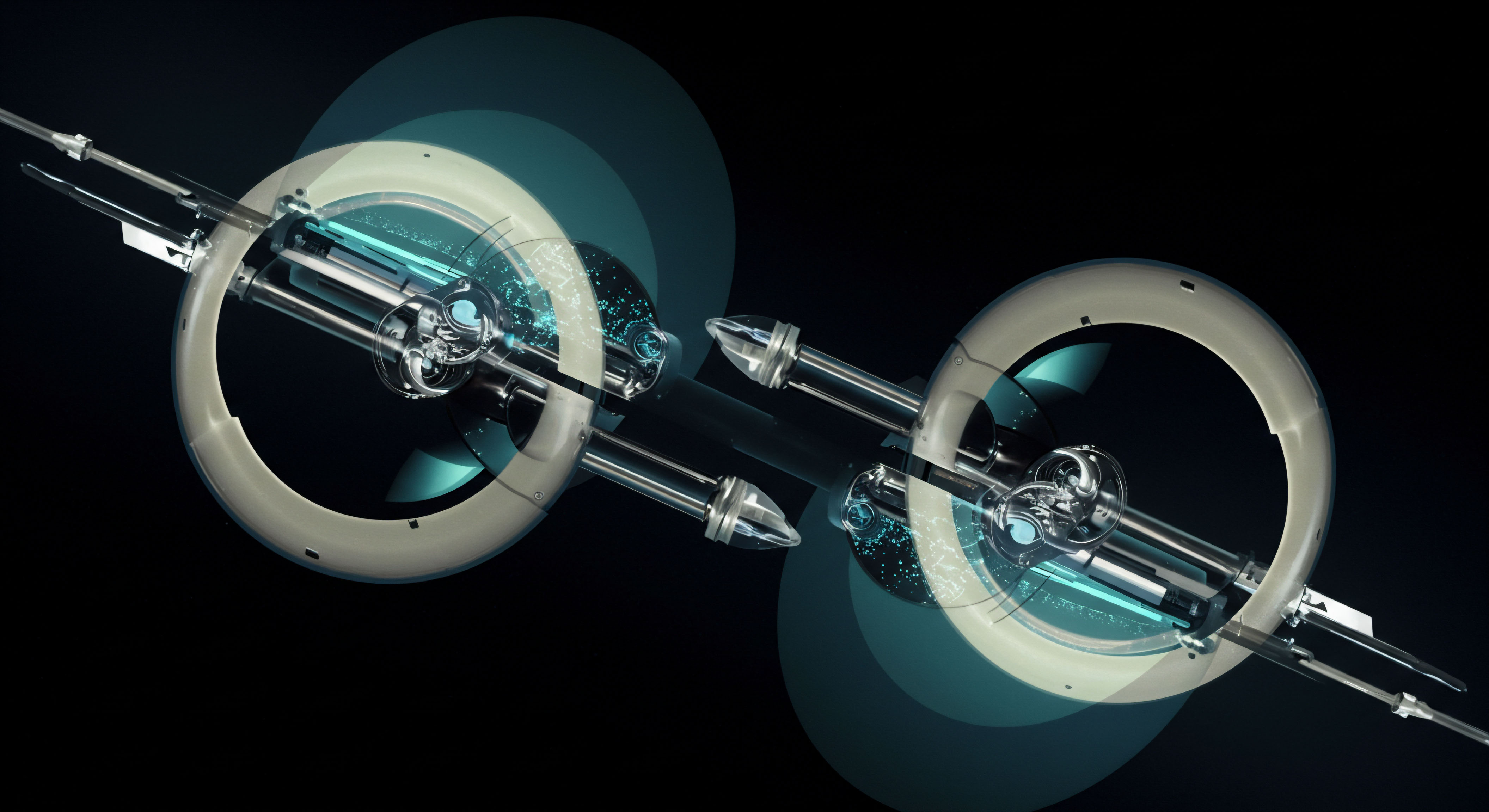

Co-location is the first and most fundamental layer of execution. It involves leasing rack space within a data center operated by a financial exchange, such as the NYSE facility in Mahwah, New Jersey, or the CME’s center in Aurora, Illinois. The primary goal is to reduce the physical distance signals must travel to the absolute minimum.

Inside these facilities, the unit of distance is not miles, but feet. The length of fiber optic cables connecting a firm’s server to the exchange’s matching engine is a critical variable.

The process follows a clear operational sequence:

- Facility Onboarding ▴ Gaining access to an exchange data center is a rigorous process involving contracts, security vetting, and significant financial investment.

- Hardware Deployment ▴ Servers, switches, and FPGA cards are physically installed in the leased rack space. These systems are often highly customized for power efficiency and thermal management in a dense environment.

- Cross-Connection ▴ A firm orders a “cross-connect,” a direct fiber optic link from its rack to the exchange’s network access point. The length and quality of this cable are specified and measured with precision.

- Market Data Feeds ▴ The firm subscribes to the exchange’s direct binary data feeds. These feeds provide raw, unprocessed market information at the highest possible speed, unlike consolidated feeds which introduce aggregation delays.

- System Synchronization ▴ All systems within the rack are synchronized to a central, high-precision clock, often using the Precision Time Protocol (PTP). This ensures that timestamps on all incoming and outgoing messages are accurate to the nanosecond level, which is vital for strategy analysis and regulatory compliance.

The impact of this physical placement is profound. A signal traveling through fiber optic cable is limited by the speed of light in glass, roughly two-thirds the speed of light in a vacuum. This results in a delay of approximately 5 microseconds for every kilometer of distance.

By moving from a Manhattan office (roughly 50km away from Mahwah) into the co-location facility, a firm eliminates hundreds of microseconds of round-trip latency. This is an advantage that no amount of software optimization can overcome.

Quantitative Modeling for Hardware Acceleration

The core of HFT execution lies in offloading latency-critical tasks from software to hardware. FPGAs are the primary tool for this. The process begins with a quantitative breakdown of the trading workflow, identifying every source of delay. The goal is to move any task that is simple, repetitive, and time-sensitive onto the FPGA, leaving more complex, less frequent tasks for the CPU.

The following table presents a hypothetical but realistic latency budget for a tick-to-trade loop, comparing a pure software implementation on a CPU with an FPGA-accelerated system. The times are measured in nanoseconds (ns).

| Processing Stage | Standard CPU System (ns) | FPGA-Accelerated System (ns) | Rationale for Improvement |

|---|---|---|---|

| Network Packet Ingress | ~5,000 – 15,000 | ~100 – 200 | FPGA bypasses the kernel’s network stack (e.g. TCP/IP processing), interacting directly with the network interface controller (NIC). |

| Market Data Parsing | ~1,000 – 5,000 | ~50 – 150 | Parallel hardware decoders on the FPGA process the binary feed message as it streams in, without waiting for the full packet. |

| Order Book Update | ~500 – 2,000 | ~20 – 80 | The order book is maintained in the FPGA’s on-chip Block RAM (BRAM), allowing for parallel updates to multiple price levels simultaneously. |

| Strategy Logic Execution | ~1,000 – 10,000+ | ~10 – 100 | Simple, reactive logic is implemented as a state machine in hardware circuits, executing in a few clock cycles. |

| Pre-Trade Risk Check | ~2,000 – 8,000 | ~15 – 50 | Risk limits and checks are hardwired into the FPGA logic, running in parallel with the final order generation step. |

| Order Formatting & Egress | ~3,000 – 10,000 | ~100 – 250 | The FPGA constructs the outgoing binary order and pushes it directly to the NIC, again bypassing the software stack. |

| Total Tick-to-Trade | ~12,500 – 50,000+ ns (12.5 – 50+ µs) | ~295 – 830 ns (0.3 – 0.8 µs) | An improvement of over two orders of magnitude. |

This quantitative analysis demonstrates the systemic advantage conferred by FPGAs. The reduction in latency is not incremental; it is a step-change in performance that makes previously impossible strategies viable. The determinism of the FPGA is equally important; the latency values for the FPGA system have very low variance, whereas the CPU system’s latency can fluctuate wildly depending on operating system load and other factors. This predictability is paramount for the systematic execution of HFT strategies.

System Integration and Technological Architecture

The FPGA does not operate in isolation. It is a component within a larger, highly specialized technological architecture. A typical HFT server consists of a high-performance motherboard with one or more multi-core CPUs, significant RAM, and several PCIe slots. An FPGA acceleration card, such as an AMD Alveo or one from a specialized vendor like BittWare, is installed in one of these PCIe slots.

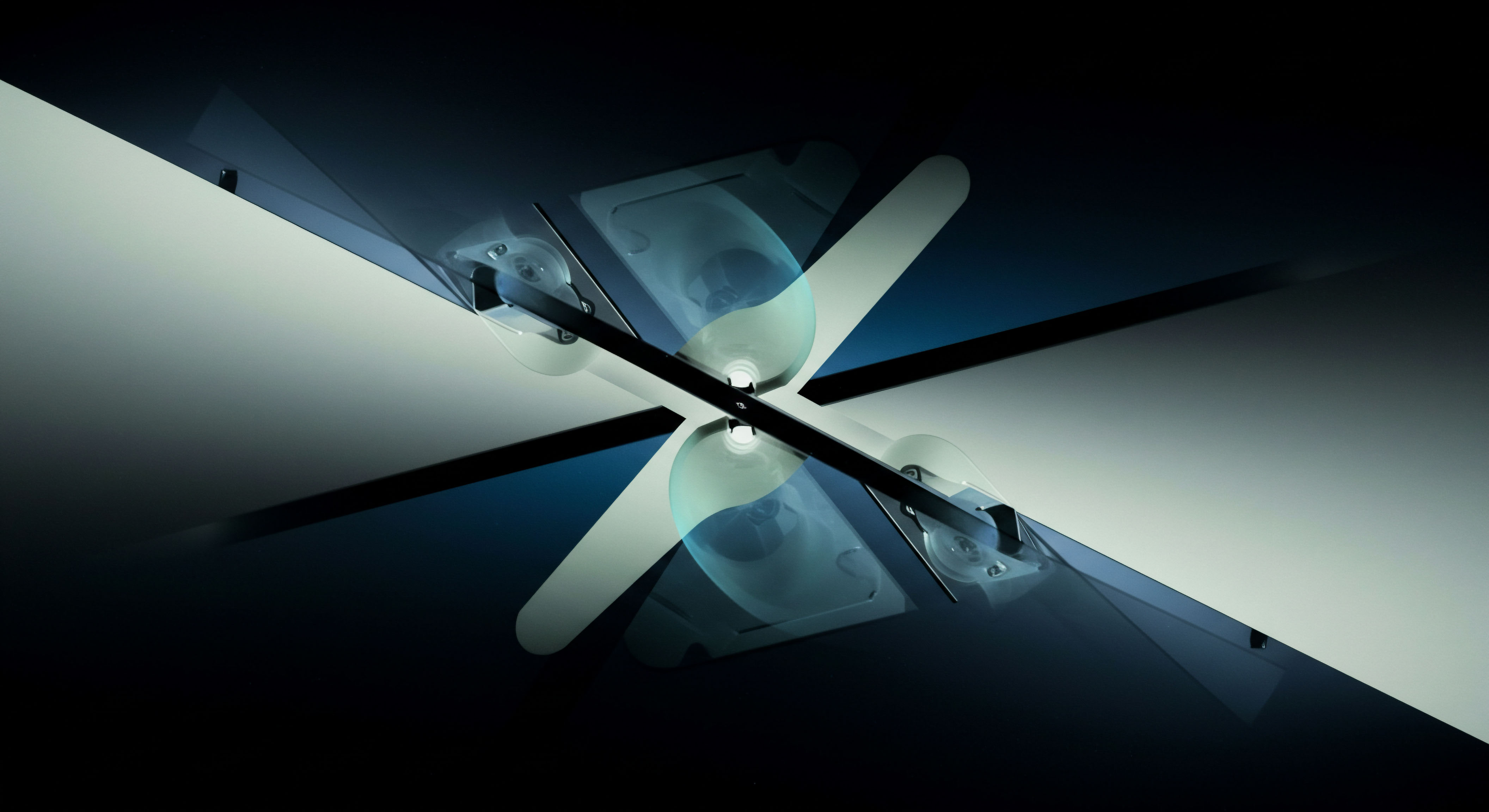

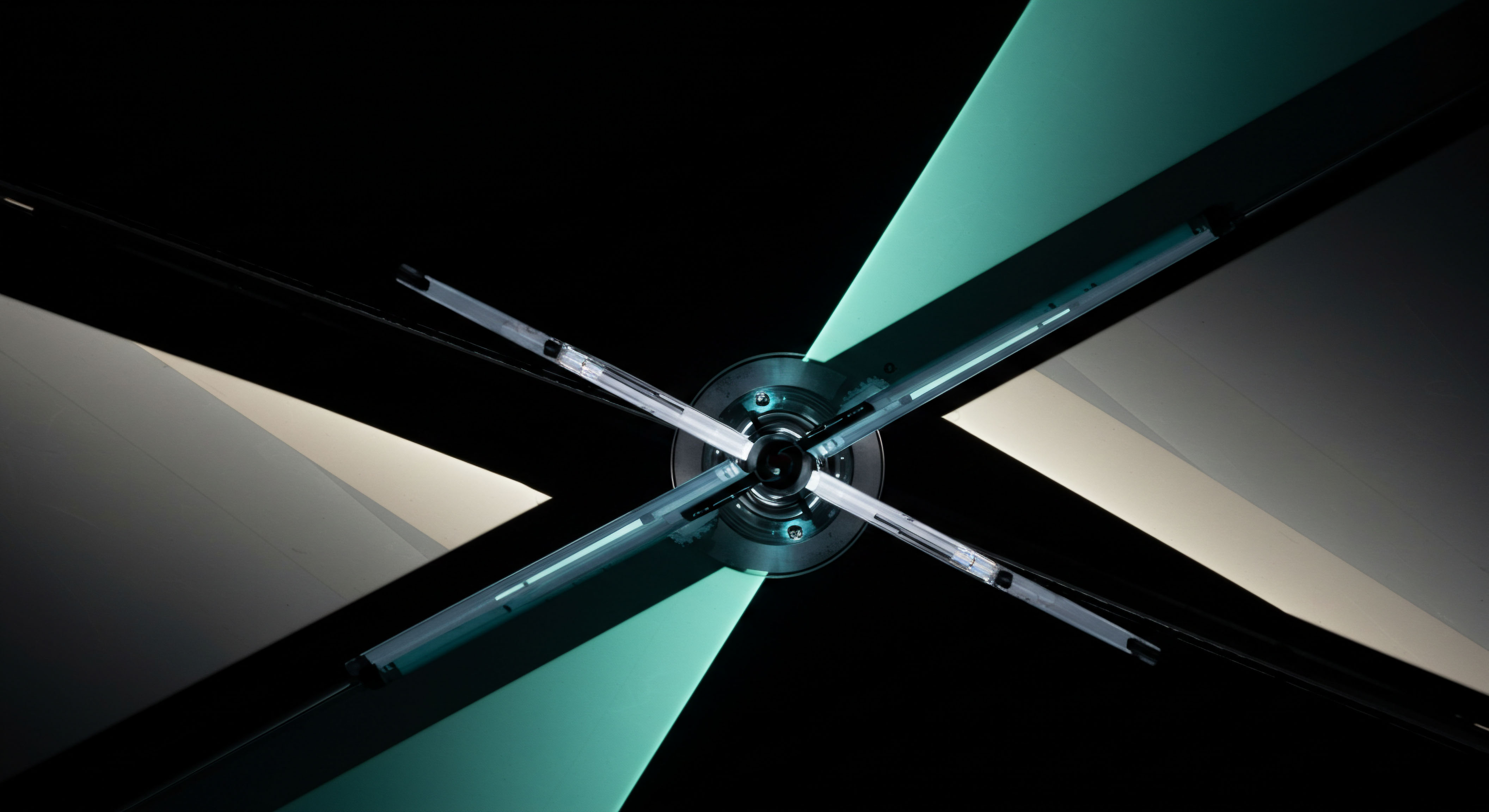

The integration architecture is designed for a clear division of labor:

- The FPGA ▴ Handles the “fast path.” This includes all the ultra-latency-sensitive tasks detailed in the table above ▴ receiving market data, maintaining the top of the order book, executing simple reactive logic, performing risk checks, and sending orders. It is programmed using a Hardware Description Language (HDL) like Verilog or SystemVerilog.

- The CPU ▴ Handles the “slow path.” This includes tasks that are less time-sensitive but more complex. Examples include managing the overall trading strategy, performing sophisticated statistical analysis, maintaining historical data, and communicating with the firm’s central monitoring systems. The software on the CPU is typically written in C++.

- The PCIe Bus ▴ This is the high-speed communication channel between the FPGA and the host CPU. The FPGA can write market events or status updates directly into the CPU’s memory via Direct Memory Access (DMA), minimizing CPU involvement and delay.

- The Network Switch ▴ The servers connect to a low-latency network switch. These are often FPGA-based themselves, capable of forwarding packets in nanoseconds and supporting features like multicast filtering directly in hardware to ensure each server only receives the data it needs.

This hybrid architecture provides the best of both worlds. It combines the raw, deterministic speed of hardware for the most critical tasks with the flexibility and complexity of software for higher-level strategy management. The result is a system that can react to market events at the physical limits of technology while still allowing for the sophisticated modeling and control required by modern financial markets.

References

- Aquilina, M. Budish, E. & O’Neill, P. (2021). Quantifying the high-frequency trading “arms race”. BIS Working Papers, No 955. Bank for International Settlements.

- Manahov, V. (2016). A note on the relationship between high-frequency trading and latency arbitrage. International Review of Financial Analysis, 47, 281-296.

- Budish, E. Cramton, P. & Shim, J. (2015). The High-Frequency Trading Arms Race ▴ Frequent Batch Auctions as a Market Design Response. The Quarterly Journal of Economics, 130(4), 1547-1621.

- Foucault, T. Kozhan, R. & Tham, W. (2016). Toxic Arbitrage. HEC Paris Research Paper No. FIN-2016-1148.

- Baron, M. Brogaard, J. & Kirilenko, A. (2019). The trading profits of high frequency traders. Journal of Financial Economics, 133(1), 59-81.

- Hasbrouck, J. & Saar, G. (2013). Low-latency trading. Journal of Financial Markets, 16(4), 646-679.

- Pagnotta, E. & Philippon, T. (2018). Technology and the new landscape of finance. NBER Working Paper No. 25057.

- Wah, E. (2013). High-Frequency Trading and Market Stability. Reserve Bank of Australia.

- Chaboud, A. P. Chiquoine, B. Hjalmarsson, E. & Vega, C. (2014). Rise of the machines ▴ Algorithmic trading in the foreign exchange market. The Journal of Finance, 69(5), 2045-2084.

- O’Hara, M. (2015). High-frequency market microstructure. Journal of Financial Economics, 116(2), 257-270.

Reflection

The intricate system of co-location and hardware acceleration reveals a fundamental truth about modern markets ▴ the pursuit of alpha is now inextricably linked to the mastery of physics and information theory. The engineering of latency is a discipline focused on shaving nanoseconds from processes, a scale of time that is almost abstract. Yet, the accumulated value of these infinitesimal moments is substantial, shaping liquidity dynamics and defining the very structure of market competition. The architecture described is a testament to human ingenuity in the face of physical constraints.

Contemplating this system prompts a critical question for any market participant, regardless of their strategy’s time horizon. What are the core physical and informational constraints governing your own operational framework? While most will not operate at the nanosecond level, the principles of minimizing delay between signal, decision, and action are universal.

The HFT apparatus, in its ultimate expression, serves as a powerful model for thinking about efficiency, system design, and the identification of structural advantages within any competitive environment. The ultimate edge lies not just in what you know, but in the operational excellence of the system you build to act on that knowledge.

Glossary

High-Frequency Trading

Market Data

Co-Location

Fpga

Latency Arbitrage

Pre-Trade Risk Checks

Tick-To-Trade

Low Latency