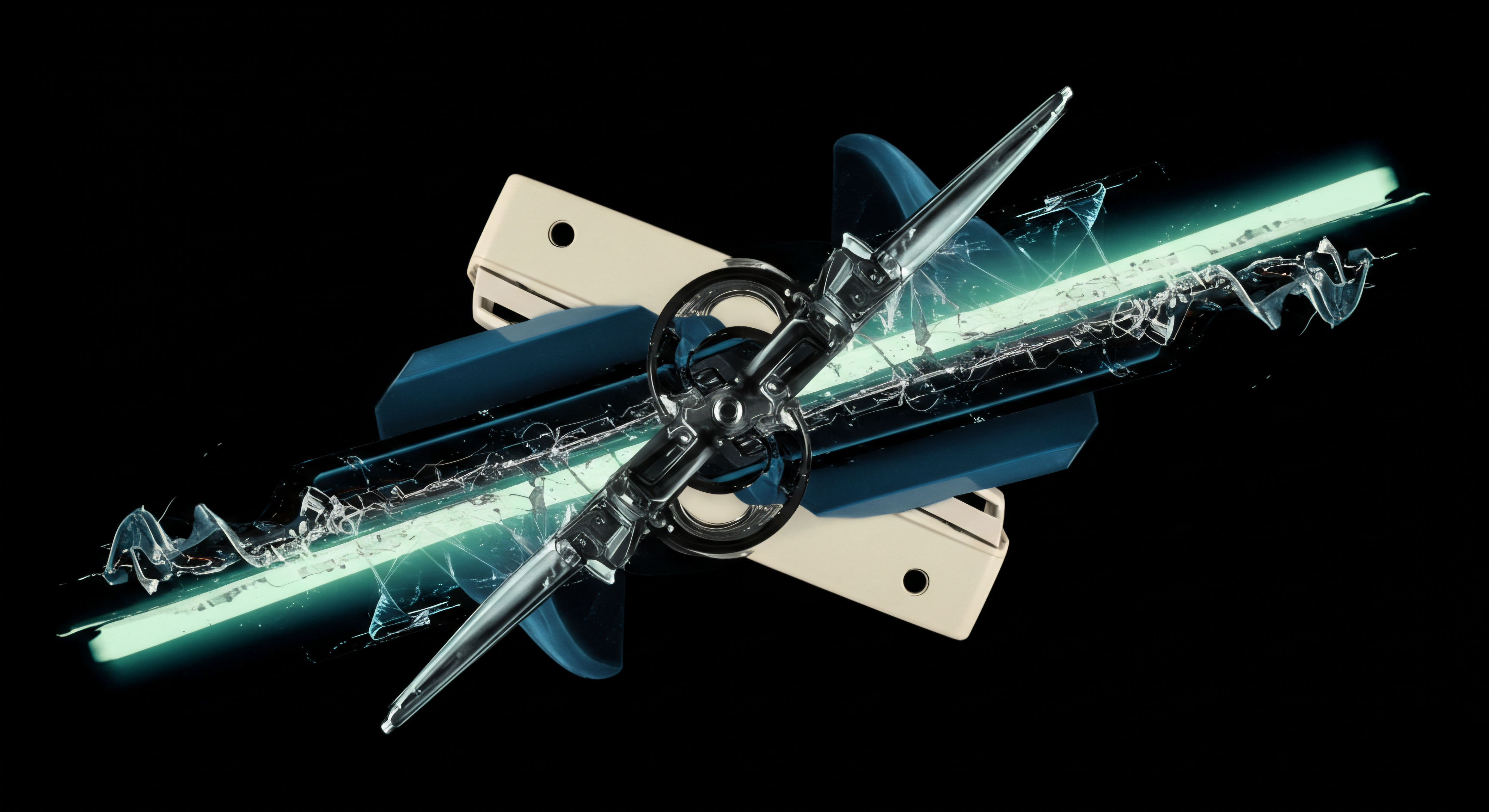

Concept

The operational calculus of institutional options trading is governed by a single, unyielding imperative ▴ the immediate and precise quantification of risk before commitment. For any entity seeking to provide liquidity or take on significant, multi-leg positions, the window between a market data update and the execution of an order is a critical vulnerability. Within this interval, which is measured in microseconds or nanoseconds, a complex array of calculations must be completed. These are not simple arithmetic; they are computationally intensive models that determine the potential loss exposure across a vast portfolio of positions under thousands of potential market scenarios.

The core challenge is that these pre-trade risk calculations, encompassing everything from credit limit checks to the calculation of option Greeks, represent a significant computational bottleneck. A software-based approach, running on general-purpose CPUs, introduces a latency penalty that directly impacts competitiveness and exposes the firm to adverse selection.

This is the environment where Field-Programmable Gate Arrays (FPGAs) provide a definitive architectural solution. An FPGA is an integrated circuit containing a matrix of configurable logic blocks and programmable interconnects. Unlike a CPU that processes instructions sequentially, an FPGA is configured at the hardware level to perform a specific task. For pre-trade risk calculations, this means creating a dedicated, massively parallel digital circuit.

Every risk check, for every affected position, can be executed simultaneously. The calculation becomes a flow of electrons through logic gates, a deterministic process with a fixed, minimal latency. The role of the FPGA is to transform the pre-trade risk check from a time-consuming software routine into a predictable, ultra-low-latency hardware function. This shift is fundamental. It redefines the operational limits of a trading desk, enabling a scale and speed of risk management that is simply unattainable through software alone.

FPGAs serve to offload the immense computational load of pre-trade risk assessments from software to dedicated hardware, achieving a deterministic, ultra-low latency required for competitive options trading.

The inherent parallelism of FPGA architecture is the key mechanism. Consider the calculation of a portfolio’s total exposure. A CPU would need to iterate through each position, calculate its risk, and aggregate the results. An FPGA can be designed to perform all these calculations in a single clock cycle.

This capability extends to complex option pricing models like Black-Scholes or binomial models, and even components of Monte Carlo simulations, which are foundational to pricing exotic options. By mapping these mathematical models directly onto silicon, the FPGA acts as a co-processor, purpose-built for the specific financial mathematics of options risk. The result is a dramatic reduction in processing time, with reported speedups ranging from 20 to over 100 times compared to software implementations. This acceleration is the central function of FPGAs in this domain, providing the technological foundation for modern, high-frequency market-making and risk management systems.

Strategy

The decision to integrate FPGAs into a trading architecture is a strategic one, centered on achieving a sustainable competitive advantage through superior execution speed and risk management capabilities. The primary strategic objective is latency arbitrage in its purest form. In the world of electronic options trading, the firm that can accurately price options and assess risk the fastest holds a decisive edge. This speed allows a firm to update its quotes more rapidly in response to market data changes, ensuring its posted prices are the most current and accurately reflect its desired risk position.

Firms with slower, CPU-based risk systems are forced to build wider spreads into their quotes to buffer against the risk of being picked off by faster counterparties during volatile periods. An FPGA-based system allows for tighter, more aggressive quoting, increasing the probability of capturing order flow while maintaining stringent risk controls.

Architectural Tradeoffs CPU Vs GPU Vs FPGA

Choosing the right processing architecture for pre-trade risk calculations involves a careful analysis of performance, flexibility, and development overhead. CPUs offer the highest flexibility and ease of programming, but their sequential processing nature creates a significant latency bottleneck. GPUs provide massive parallelism suitable for certain calculations but are optimized for large batches of data and can introduce their own latency, making them less ideal for the single, ultra-low-latency decisions required in pre-trade checks. FPGAs offer the lowest possible latency and highest power efficiency for a specific task, at the cost of significantly higher development complexity.

The strategic choice hinges on the firm’s primary business. For high-frequency market-making in options, the deterministic low latency of FPGAs is the enabling technology.

| Metric | CPU (Central Processing Unit) | GPU (Graphics Processing Unit) | FPGA (Field-Programmable Gate Array) |

|---|---|---|---|

| Primary Strength | Flexibility and ease of use. | High-throughput for large, parallel data batches. | Ultra-low, deterministic latency for specific tasks. |

| Typical Latency | Tens of microseconds. | Microseconds to milliseconds (batch-dependent). | Sub-microsecond to nanoseconds. |

| Parallelism | Limited (tens of cores). | High (thousands of cores). | Massive, fine-grained parallelism limited by chip size. |

| Development Complexity | Low (C++, Java, Python). | Moderate (CUDA, OpenCL). | High (VHDL, Verilog, High-Level Synthesis). |

| Power Consumption | Moderate to High. | Very High. | Low for the given task. |

| Best Use Case | General trading logic, post-trade analysis. | Overnight portfolio risk simulations, model training. | Pre-trade risk checks, market data processing, ultra-low-latency execution. |

What Is the Strategic Impact on Liquidity Provision?

For an options market maker, the ability to manage risk in real-time directly translates to the amount and quality of liquidity it can provide to the market. A firm confident in its sub-microsecond risk checks can quote tighter and with larger sizes across a wider array of instruments. This confidence stems from knowing that the system can instantly pull quotes portfolio-wide if a risk limit is breached. This prevents the cascading losses that can occur when a software-based system is too slow to react to a sudden market move.

Consequently, firms with FPGA-accelerated risk systems become more reliable liquidity providers, which enhances their reputation and attracts more order flow. This creates a virtuous cycle where superior technology enables better market share and profitability.

The strategic adoption of FPGAs transforms pre-trade risk from a computational constraint into a source of competitive advantage, enabling more aggressive and reliable liquidity provision.

Regulatory Compliance and Future-Proofing

Another strategic dimension is the evolving regulatory landscape. Mandates from regulators globally are increasingly focused on preventing market disruptions caused by algorithmic trading. These rules often require stringent pre-trade risk controls. A software-based implementation of these additional checks would add a cumulative latency penalty, degrading performance.

FPGAs offer a solution where new risk checks can be added in parallel within the hardware design, often with a negligible impact on overall latency. By investing in an FPGA framework, a firm is not just optimizing for today’s market structure but is also building a flexible and scalable platform that can adapt to future regulatory requirements without sacrificing its competitive latency profile.

Execution

The execution of an FPGA-based acceleration strategy for pre-trade risk is a complex, multi-disciplinary undertaking that bridges quantitative finance, hardware engineering, and systems architecture. It requires a departure from traditional software development cycles and an embrace of a hardware-centric design philosophy. The goal is to physically wire the firm’s risk model into a silicon chip that sits directly in the critical path of order flow, acting as an ultra-fast, deterministic gatekeeper.

The Operational Playbook

Implementing an FPGA risk calculation engine is a systematic process. It moves from high-level model selection to low-level hardware programming and integration. Success requires meticulous planning and expertise across multiple domains.

- Algorithm Selection and Optimization ▴ The first step is to select the specific risk calculations to be offloaded. For standard options, this might be a Black-Scholes-Merton model for calculating Greeks (Delta, Gamma, Vega). For more complex products, it could be a simplified Monte Carlo simulation. The chosen algorithm must then be optimized for hardware implementation. This involves converting floating-point arithmetic to fixed-point where possible, and restructuring the calculations to maximize parallelism.

- Hardware and Toolchain Selection ▴ The team must select an appropriate FPGA device and development board (e.g. from vendors like Xilinx/AMD or Intel). This choice depends on the complexity of the algorithm, the required number of logic cells and DSP blocks, and the I/O capabilities for connecting to the network and host server. The team will also choose a design methodology, which can be a traditional Hardware Description Language (HDL) like VHDL or Verilog, or a High-Level Synthesis (HLS) approach that transpiles C++ or similar languages into HDL.

- HDL Development and Simulation ▴ This is the core engineering phase where hardware engineers translate the optimized algorithm into a circuit design. They write HDL code to define the logic gates, registers, and memory blocks that will perform the calculations. This process is followed by extensive simulation, where the HDL code is tested against millions of input vectors to ensure its logical correctness and equivalence to the original software model.

- Synthesis, Place, and Route ▴ The verified HDL code is run through a synthesis tool. This tool converts the human-readable code into a netlist, a low-level description of the circuit. The “place and route” process then maps this logical circuit onto the physical resources of the FPGA and determines the wiring between them. This step is computationally intensive and critical for meeting timing constraints (i.e. ensuring the circuit can run at the desired clock speed).

- System Integration and Testing ▴ The programmed FPGA, now a dedicated risk co-processor, is integrated into the trading system. This typically involves a PCIe interface to a host server. A software driver and API are developed to allow the main trading application to offload risk calculations to the FPGA. End-to-end testing is performed, sending live or simulated market data through the system to verify that the FPGA correctly performs its gating function based on the calculated risk and predefined limits.

Quantitative Modeling and Data Analysis

The performance gains from FPGA acceleration are most evident when analyzing the latency breakdown of a pre-trade risk check. The FPGA’s ability to parallelize calculations collapses what would be a sequence of steps in software into a near-instantaneous hardware operation. This is particularly powerful when calculating the “Greeks,” the sensitivities of an option’s price to various factors.

By mapping complex financial models directly onto silicon, FPGAs reduce multi-microsecond software calculations to a deterministic, sub-microsecond hardware function.

An FPGA can be designed with separate, parallel calculation units for Delta, Gamma, and Vega. When the input parameters (stock price, strike, volatility, etc.) are received, all three Greeks are computed simultaneously. This is a fundamental departure from a CPU, which would typically calculate them one after another.

| Process Step | CPU-Based System (Latency in µs) | FPGA-Accelerated System (Latency in µs) | Notes |

|---|---|---|---|

| Market Data Ingress (NIC to App) | 2.5 | 0.2 | FPGA can perform network offload, processing packets directly. |

| Order Decode & Portfolio Lookup | 1.0 | 0.5 | Host CPU performs this in both, but faster hand-off in FPGA system. |

| Risk Calculation (Greeks, Scenarios) | 15.0 | 0.3 | The core acceleration. FPGA parallelism vs. CPU sequential processing. |

| Limit Check (Exposure, Credit) | 2.0 | 0.1 | Limits can be stored and checked in parallel on the FPGA. |

| Order Dispatch Decision | 0.5 | 0.1 | Simple pass/fail signal from FPGA to host or direct to NIC. |

| Total Latency | 21.0 µs | 1.2 µs | Over 17x improvement in this hypothetical example. |

How Does FPGA Architecture Handle Portfolio Effects?

A critical function of pre-trade risk is understanding not just the risk of a single trade, but its marginal impact on the entire portfolio. FPGAs excel here. A portion of the FPGA’s onboard memory can be used to store the current risk profile of the entire options portfolio. When a new potential trade arrives, the FPGA calculates the risk of the new trade and, in parallel, computes the new aggregate portfolio risk.

This instantaneous, holistic view is exceptionally difficult to achieve in software at low latencies. The FPGA can be programmed to check numerous risk limits simultaneously ▴ total delta exposure, gamma concentration, vega limits, and counterparty credit limits, generating a single pass/fail signal in nanoseconds.

Predictive Scenario Analysis

Consider a specialized volatility arbitrage fund, “Helios VolArb,” operating in the highly competitive S&P 500 options market. Their strategy relies on making markets in short-dated options, requiring thousands of quote updates per second across hundreds of instruments. Initially, Helios employed a state-of-the-art, CPU-based trading system. Their pre-trade risk checks, coded in optimized C++, ran on the fastest available server CPUs.

The average latency for a full risk check ▴ including market data processing, calculating the Greeks for the affected instrument, and aggregating the impact on their total portfolio’s delta and gamma limits ▴ was approximately 25 microseconds. On a normal trading day, this was sufficient. The system performed reliably, and the fund was profitable.

The architectural vulnerability was exposed during a surprise announcement by a central bank, triggering a massive spike in market volatility. As the underlying index began moving rapidly, Helios’s system was flooded with market data updates. Their CPU-based risk check system, which processed requests sequentially, developed a queue. The 25-microsecond average latency ballooned to over 150 microseconds as the CPUs struggled to keep up.

This latency had two devastating consequences. First, their pricing engine was now using stale risk information to generate quotes. They were hit on multiple stale quotes by faster firms, leading to an immediate, unplanned increase in negative gamma exposure. Second, by the time their system could calculate the new portfolio risk and attempt to send updated, wider quotes to the exchange, the market had moved again.

They were perpetually behind the curve. Within minutes, the system automatically breached its portfolio-wide gamma limit, forcing a complete shutdown of quoting. The fund was flat, but it had missed a period of historic opportunity and had taken several significant losses from being adversely selected.

Following this event, Helios initiated a strategic pivot to an FPGA-based architecture. The project was a significant undertaking, requiring the hiring of two hardware engineers and a capital investment of over $500,000 in FPGA development cards and tools. The team spent six months re-implementing their core risk logic in VHDL. They designed a massively parallel architecture.

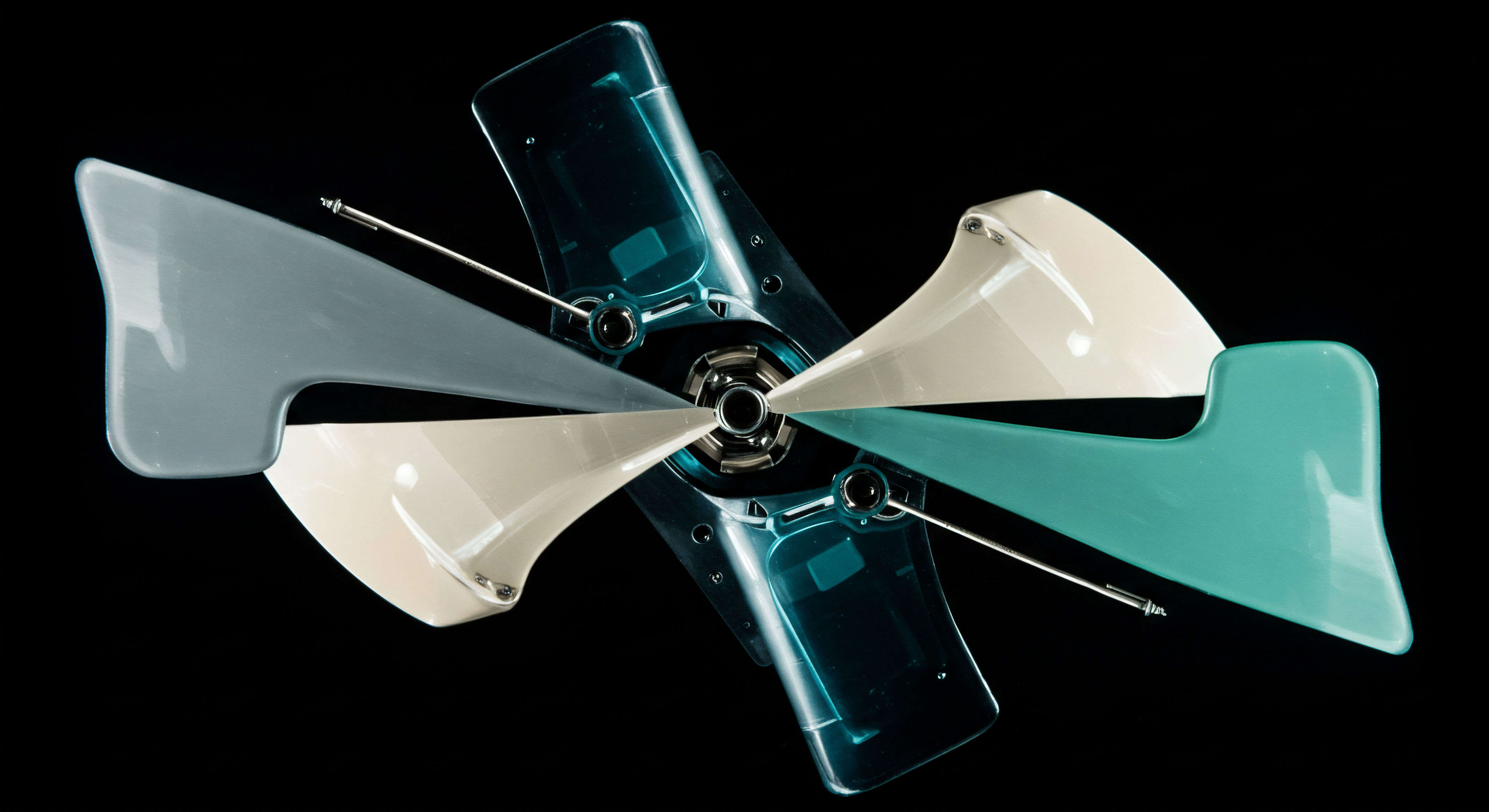

One section of the FPGA was dedicated to UDP packet processing, decoding the market data directly off the network wire. Another section contained 512 identical “Greek Calculators,” each capable of computing the Delta, Gamma, and Vega of a single option in parallel. A final section, the “Portfolio Aggregator,” stored the fund’s overall risk position in the FPGA’s on-chip memory and could update it based on the output of any Greek Calculator in a single clock cycle.

The integration was challenging. The software team had to build a new API to communicate with the FPGA card over the PCIe bus. The new system offloaded the entire pre-trade risk check to the hardware. When a market data update arrived, the FPGA performed the entire check and returned a simple “pass” or “fail” signal to the trading application in 700 nanoseconds ▴ a more than 35-fold reduction in latency.

Six months later, a similar market-moving event occurred. This time, the Helios system performed flawlessly. As market data poured in, the FPGA risk engine never developed a queue. It processed every event with the same deterministic 700-nanosecond latency.

Their quotes were always live, always based on the most recent market data and an accurate, real-time view of their portfolio risk. While their competitors, still running on CPU-based systems, widened their spreads or pulled their quotes entirely, Helios’s system was able to continue providing liquidity. They were able to capture the inflated bid-ask spread during the peak volatility, resulting in their most profitable trading day on record. The FPGA had become the core of their operational resilience and competitive edge.

System Integration and Technological Architecture

The physical integration of an FPGA into a trading system is a critical component of the execution strategy. The FPGA is not a standalone device; it is a co-processor that must be seamlessly woven into the fabric of the firm’s data and order flow.

- Physical Placement ▴ The FPGA is typically housed on a PCIe card, which is installed in a high-performance server located in the co-location data center of the exchange. For ultimate performance, some firms use FPGAs with integrated network ports, allowing market data to flow directly from the fiber optic cable to the FPGA’s logic, bypassing the server’s CPU and networking stack entirely.

- Data Flow ▴ In a typical setup, raw market data (e.g. UDP multicast) is received by a network interface card. The data can be passed to the FPGA via a low-latency bus like PCIe. The FPGA performs its calculations ▴ decoding the market data, calculating risks, checking limits. The result, often a simple boolean pass/fail, is passed back to the host CPU’s trading application. The trading application then makes the final decision to send an order.

- Integration with OMS/EMS ▴ The FPGA acts as a gate for the Order Management System (OMS). The logic within the OMS, before dispatching a FIX message to the exchange, will make a call to the FPGA’s API. It sends the parameters of the potential order to the FPGA and waits for the response. If the response is ‘pass’, the OMS releases the order. If it is ‘fail’, the order is rejected, and an alert is raised. This ensures that no order that violates pre-defined risk limits can ever reach the exchange.

References

- O’Mahony, A. Hanzon, B. & Popovici, E. (2024). The Role of FPGAs in Modern Option Pricing Techniques ▴ A Survey. Electronics, 13(16), 3186.

- Wimsey, T. et al. (2022). Low-power option Greeks ▴ Efficiency-driven market risk analysis using FPGAs. arXiv preprint arXiv:2206.03909.

- Maven Securities. (n.d.). FPGAs in Trading. Maven Securities Blog.

- Celoxica. (n.d.). Pre-trade Risk Checks. Celoxica White Paper.

- “Pre-Trade Risk On a Chip.” Traders Magazine, 2014.

- Xilinx. (2018). Accelerating Quantitative Finance. Xilinx White Paper WP502.

- Intel Corporation. (2020). Intel FPGAs for Low-Latency Trading. Intel White Paper.

- Long, J. & Wang, S. (2010). Accelerating the pricing of financial derivatives with FPGAs. 2010 International Conference on Field-Programmable Technology, 33-40.

Reflection

Engineering Your Operational Alpha

The exploration of FPGAs in the context of pre-trade risk reveals a fundamental truth about modern financial markets ▴ a firm’s technological architecture is inseparable from its trading strategy. The latency, determinism, and parallelism of your risk management system directly define the boundaries of your opportunity set. The concepts and execution details presented here are components of a larger operational system. Viewing your firm’s entire trading pipeline, from market data ingress to order execution, as a single, integrated system is the critical next step.

Where are the true bottlenecks in your current architecture? How does latency in one component cascade to create risk in another? The strategic integration of a specialized tool like an FPGA is a powerful solution, but its true value is only realized when it is part of a holistically designed and rigorously optimized operational framework. The ultimate edge lies in engineering that framework with intent.

Glossary

Market Data

Risk Calculations

Pre-Trade Risk

Pre-Trade Risk Check

Risk Management

Order Flow

Risk Checks

Quantitative Finance

Monte Carlo Simulation

Verilog

Vhdl

Fpga Acceleration

Portfolio Risk

Pre-Trade Risk Checks