Concept

The operational challenge of latency arbitrage is rooted in the physics of distributed systems. Financial markets, now fully electronic and geographically fragmented, present a continuous stream of minute pricing discrepancies. These are not market anomalies in the classical sense; they are the natural, inevitable byproduct of information traveling at finite speeds across fiber optic cables connecting data centers in places like Mahwah, New Jersey, and Aurora, Illinois.

The time it takes for a price update to propagate from one exchange to another creates a fleeting, nanosecond-scale window of opportunity. An asset’s price on one venue is, for a moment, a ghost of the future price on another.

Latency arbitrage is the practice of systematically exploiting these transient information asymmetries. The core premise involves observing a market event on one venue and executing a corresponding trade on a second venue before the latter has processed the same event. This act requires a trading system to perceive, decide, and act faster than the market’s own consensus mechanism can synchronize. The entire endeavor is a race against the propagation of light and the processing delays inherent in exchange matching engines.

Execution risk in this context is the direct financial penalty for being too slow, where a strategy built on speed fails because its perception of the market was fractions of a second out of date.

This introduces a unique and severe form of execution risk. The risk is absolute. If the arbitrageur’s order arrives at the second venue after the price has already updated, the opportunity vanishes. Worse, the attempt may result in a losing trade, executed at the newly updated, unfavorable price.

The very foundation of the strategy, which is to be ahead of the market’s information curve, becomes its primary vulnerability. The risk is a direct function of the system’s end-to-end latency ▴ the total time elapsed from market data photon hitting the network card to the responsive order packet leaving it.

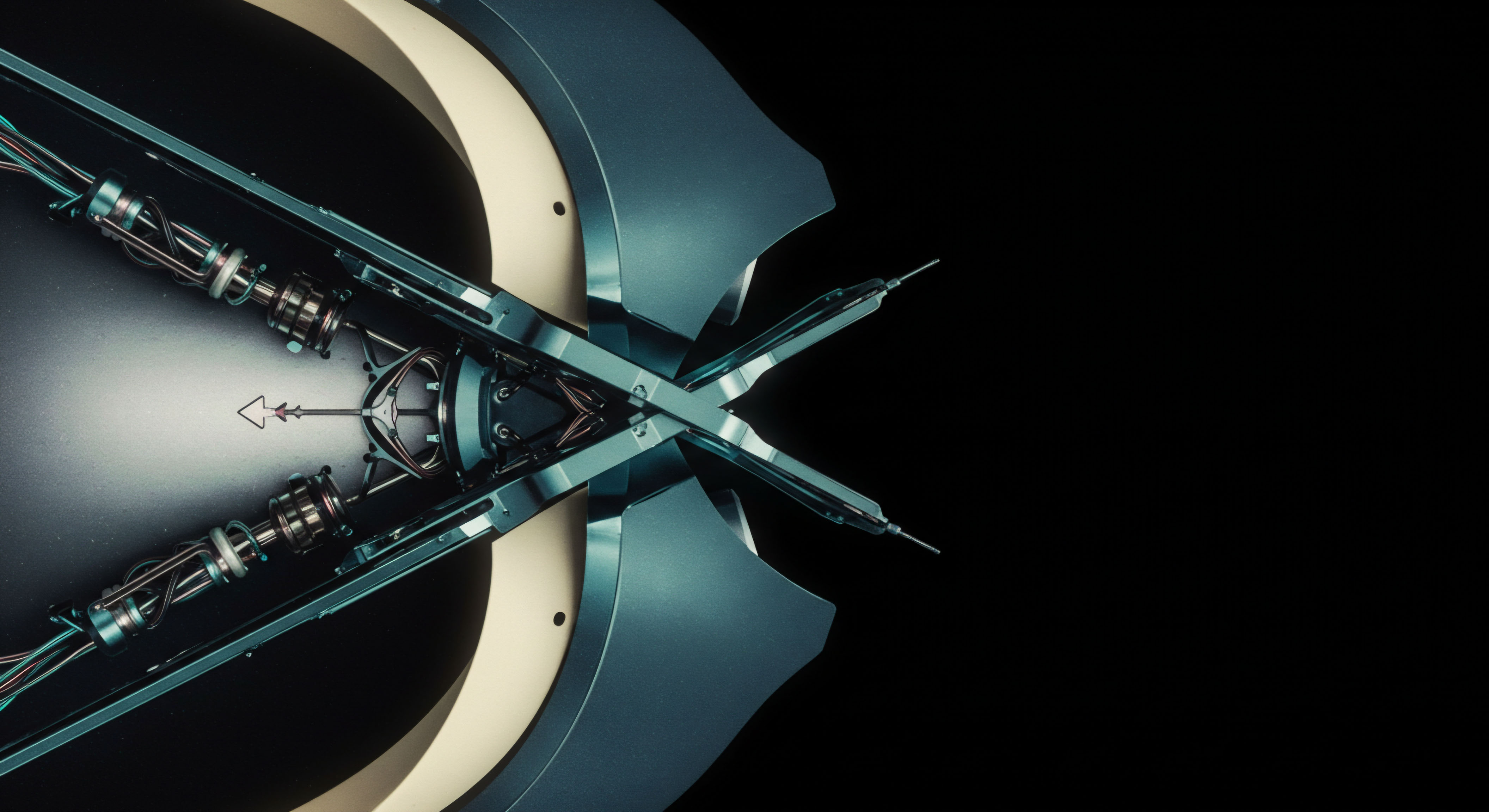

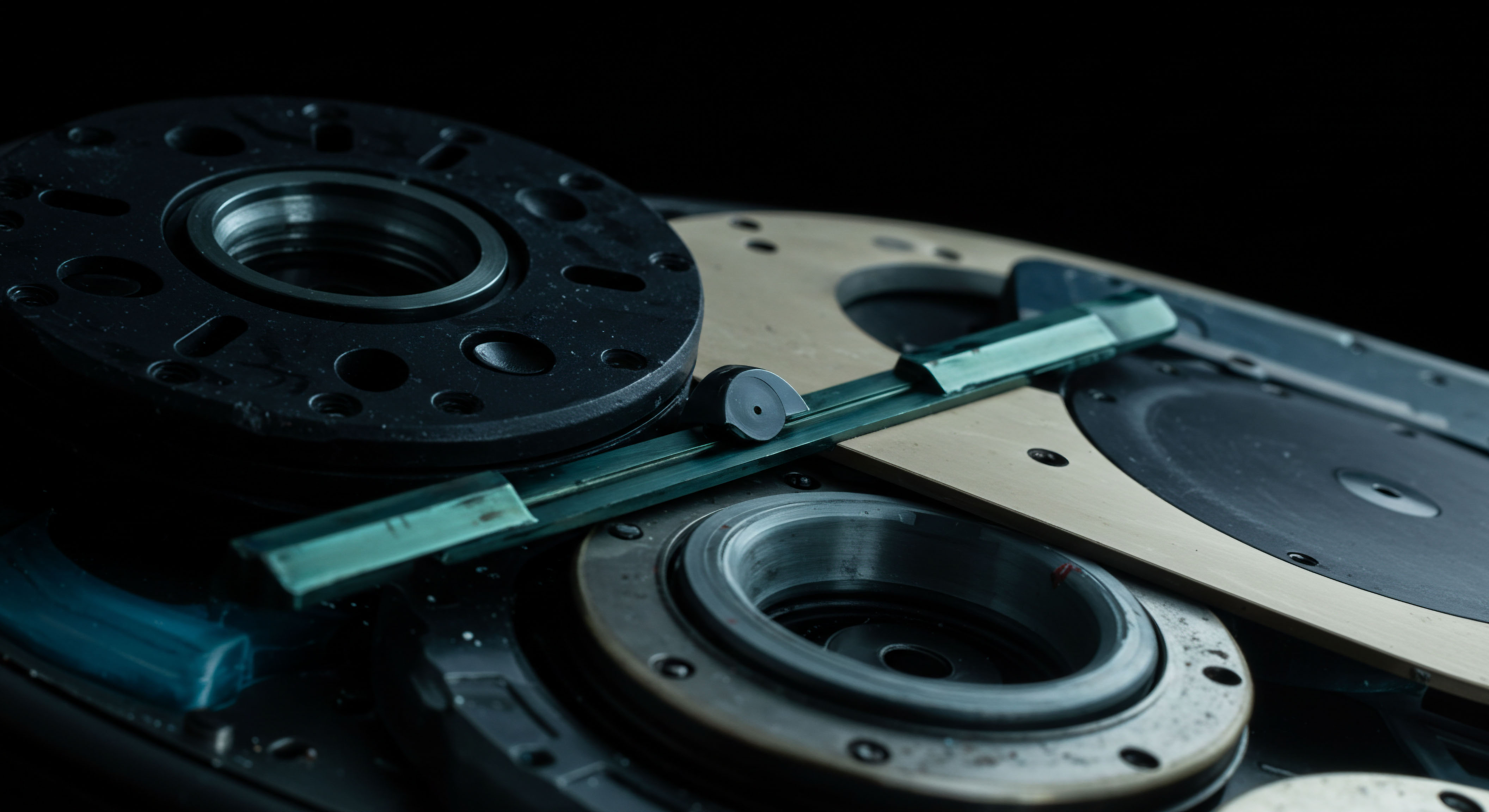

This is the precise operational problem that Field-Programmable Gate Arrays (FPGAs) are engineered to solve. An FPGA is a semiconductor device containing a matrix of configurable logic blocks and programmable interconnects. Unlike a Central Processing Unit (CPU) that runs a software operating system and executes instructions sequentially, an FPGA is configured to become the application.

The trading logic is not a program running on the chip; the logic is etched directly into the hardware circuits. This architectural distinction is the source of its power in mitigating latency arbitrage risk.

By placing the FPGA directly in the data path, as close to the network connection as physically possible, trading firms can collapse the entire software stack. The functions of a network card, a server’s operating system, and the trading application itself are fused into a single piece of silicon. This integrated system processes market data, applies trading logic, and generates orders in a continuous, deterministic flow, measured in nanoseconds. The role of the FPGA is to provide a trading system with a faster, more reliable central nervous system, ensuring that when an opportunity is perceived, the reaction is so immediate that execution risk is structurally minimized.

Strategy

The decision to integrate FPGAs into a trading architecture represents a fundamental strategic commitment to controlling the physical layer of execution. It moves a firm’s competitive focus from crafting clever software algorithms to engineering superior hardware-level processing. The strategy rests on two pillars ▴ achieving deterministic latency and leveraging the power of in-line data processing.

The Pursuit of Determinism

In the context of latency arbitrage, the variance in processing time, often called “jitter,” is as dangerous as the latency itself. A software-based system running on a general-purpose CPU is an environment of managed chaos. The operating system juggles countless background processes, interrupts, and context switches. This creates unpredictable delays.

A trade decision might take 5 microseconds one time and 15 microseconds the next. For a latency arbitrage strategy, this unpredictability is fatal. A strategy that is profitable on average can be wiped out by a single, ill-timed latency spike.

The core strategic value of an FPGA is its deterministic nature. Since the trading logic is implemented in hardware, the time it takes to process a packet is fixed. An operation will take the same number of clock cycles ▴ and therefore, the same number of nanoseconds ▴ every single time. This allows a firm to build a system with a precisely known latency budget.

Risk models become more accurate because the largest source of uncertainty, the performance of the trading system itself, is eliminated. The strategic shift is from hoping the system is fast enough to knowing its exact speed and building the arbitrage model around that physical certainty.

In-Line Processing as a Strategic Advantage

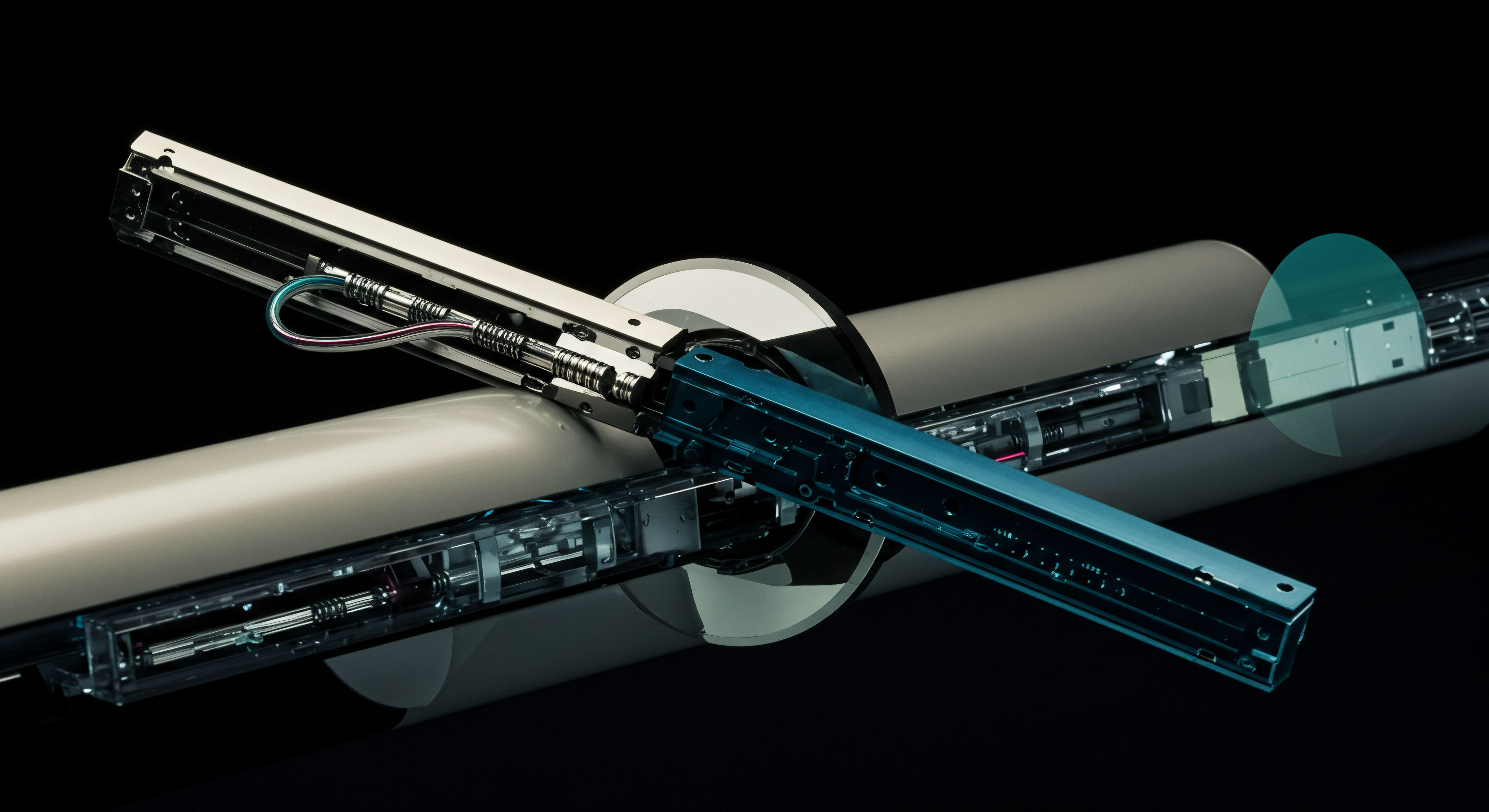

A traditional trading system receives a market data packet, passes it up through the operating system’s network stack to an application, which then decides what to do. This is a sequential and layered process. An FPGA enables a strategy of in-line, or “in-flight,” processing.

The market data packet flows into the FPGA and is acted upon as it streams through the silicon. There is no handoff between components; the FPGA is the network card, the filter, and the logic engine all at once.

This allows for a level of reflexive action that is impossible in software, where market data can be filtered, analyzed, and acted upon before it would have even reached a traditional application server.

For instance, a common strategy involves monitoring thousands of instruments but only trading a small subset. An FPGA can be programmed to inspect the header of each incoming market data packet and discard those for irrelevant instruments within nanoseconds. Only the packets of interest are passed to the deeper trading logic, also on the same chip. This pre-filtering at the hardware level dramatically reduces the data load on downstream systems and ensures the core logic only ever sees actionable information.

Comparative System Architectures

The strategic choice becomes clear when comparing the two architectures directly. A CPU-based system offers flexibility and ease of development. An FPGA-based system offers raw, deterministic performance at the cost of higher complexity and specialized engineering talent.

| Metric | CPU-Based System | FPGA-Accelerated System |

|---|---|---|

| Mean Latency (Tick-to-Trade) | Microseconds (µs) | Nanoseconds (ns) |

| Latency Variance (Jitter) | High and unpredictable | Extremely low and deterministic |

| Throughput | Limited by CPU cores and OS stack | Line-rate (e.g. 10 Gbps) processing |

| Determinism | Non-deterministic | Fully deterministic |

| Development Cycle | Fast (High-level languages) | Slow (Hardware description languages) |

What Is the Strategic Value of A/B Feed Arbitration?

A specific strategy enabled by FPGAs is A/B feed arbitration. Exchanges provide duplicate data feeds (an ‘A’ feed and a ‘B’ feed) over separate channels to guard against packet loss. A software-based system would have to ingest both feeds and run a process to compare them and identify missing packets. This reconciliation process itself introduces latency and becomes a processing bottleneck.

An FPGA can perform this arbitration at the network level. It ingests both 10Gbps feeds simultaneously, tracking the sequence numbers of each packet in real-time. If a packet is dropped on the A feed, the FPGA instantly pulls the corresponding packet from the B feed and inserts it into the data stream, creating a single, complete, and reliable view of the market. This strategy uses hardware to mitigate a fundamental infrastructure risk ▴ data loss ▴ without incurring a latency penalty, ensuring the arbitrage logic never acts on an incomplete picture of the order book.

Execution

Executing a latency arbitrage strategy with FPGAs requires a holistic approach to system architecture where every component, from the physical cabling to the logic gates on the chip, is optimized for speed and determinism. The implementation is a deep exercise in electrical engineering, computer science, and quantitative finance, focused on controlling the physical reality of the trade.

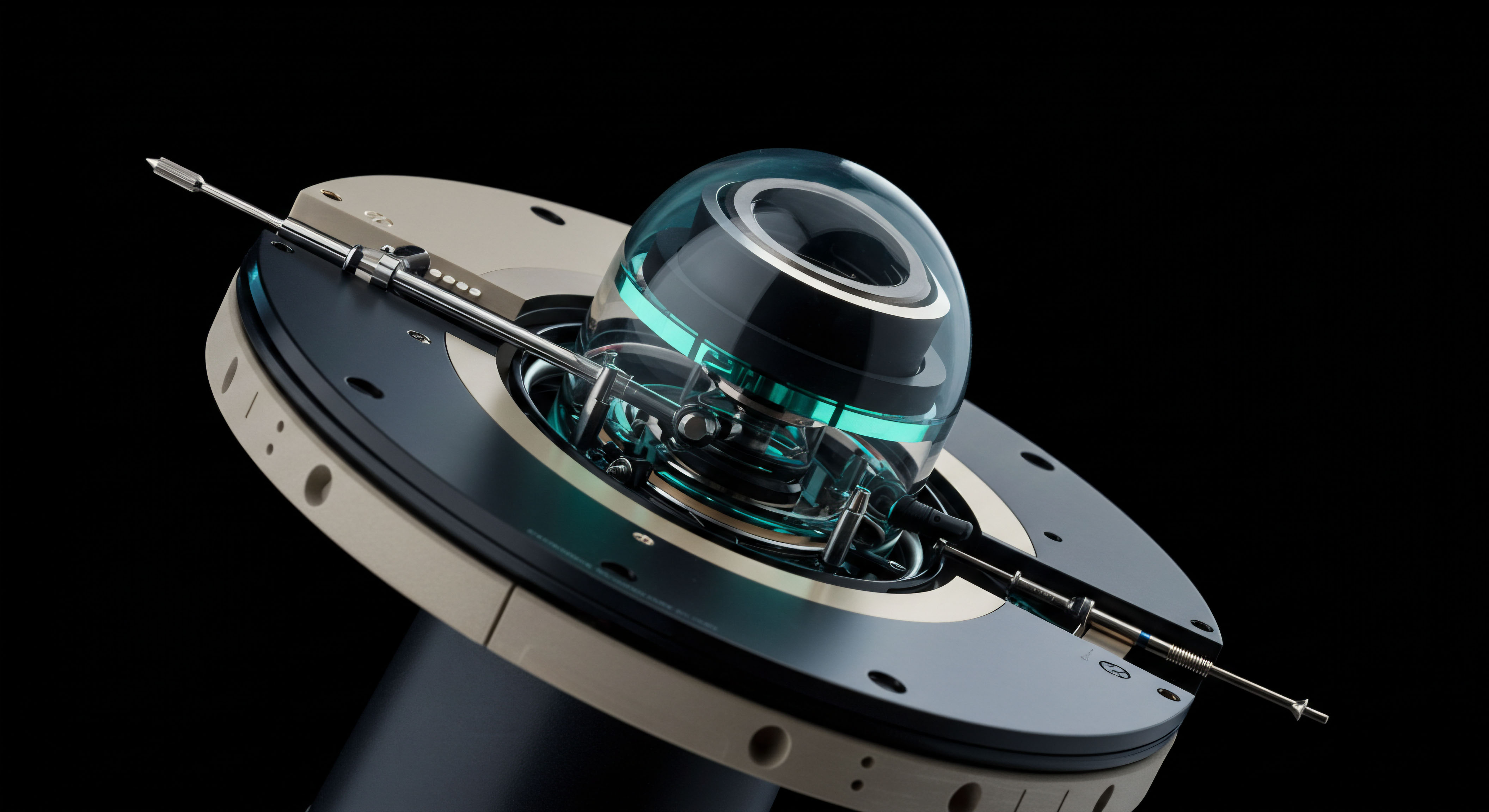

The System Architecture of a Low Latency Platform

The foundation of execution is the physical infrastructure. Firms pursuing latency arbitrage do not operate from remote offices; they operate from within the exchange’s own data center. This practice, known as colocation, is the first step in minimizing network latency.

- Colocation and Cross-Connects ▴ The firm’s servers and FPGA equipment are placed in the same physical room as the exchange’s matching engine. Communication occurs over dedicated, short-run fiber optic cables called “cross-connects.” This reduces network transit time from milliseconds to nanoseconds.

- Direct Exchange Feeds ▴ The firm subscribes to the exchange’s rawest, fastest market data feeds, such as the ITCH or T7 EOBI protocols. These feeds provide a message-by-message update of every action on the order book.

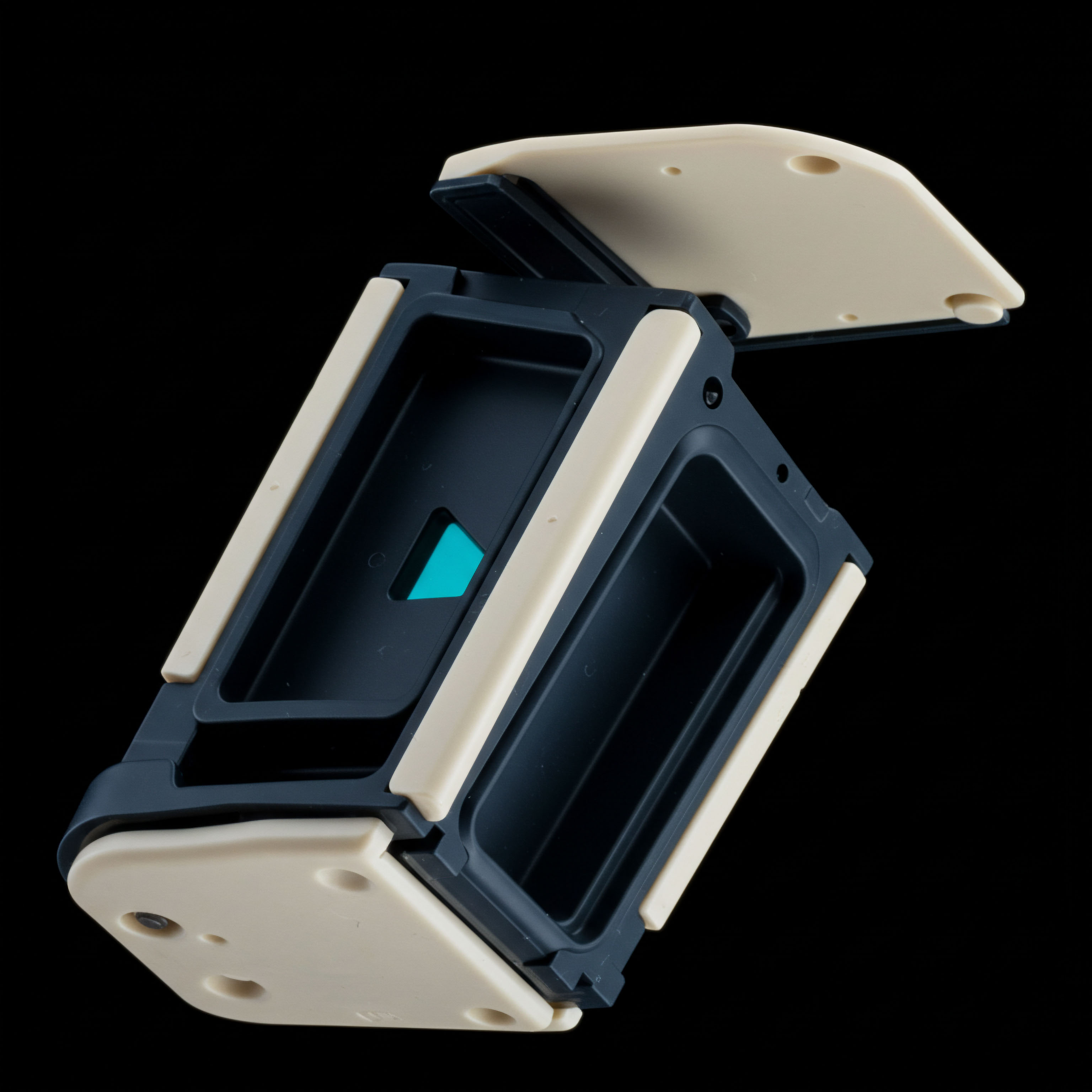

- The FPGA SmartNIC ▴ At the heart of the system is the FPGA, often in the form of a “smart” network interface card (SmartNIC). This card replaces a standard NIC in the server. It receives the raw optical signal from the cross-connect and is the entry point for all market data.

- Precision Time Protocol (PTP) ▴ All components in the trading system ▴ the FPGA, servers, and switches ▴ are synchronized to a single, high-precision clock using PTP (IEEE 1588). This ensures that timestamps applied to incoming and outgoing packets are accurate to the picosecond level, which is essential for measuring performance and debugging the system.

A Nanosecond Level View of the Execution Playbook

When a market data packet containing a relevant price update leaves the exchange’s server, a race begins. The following sequence of events occurs within the FPGA, often in under a single microsecond:

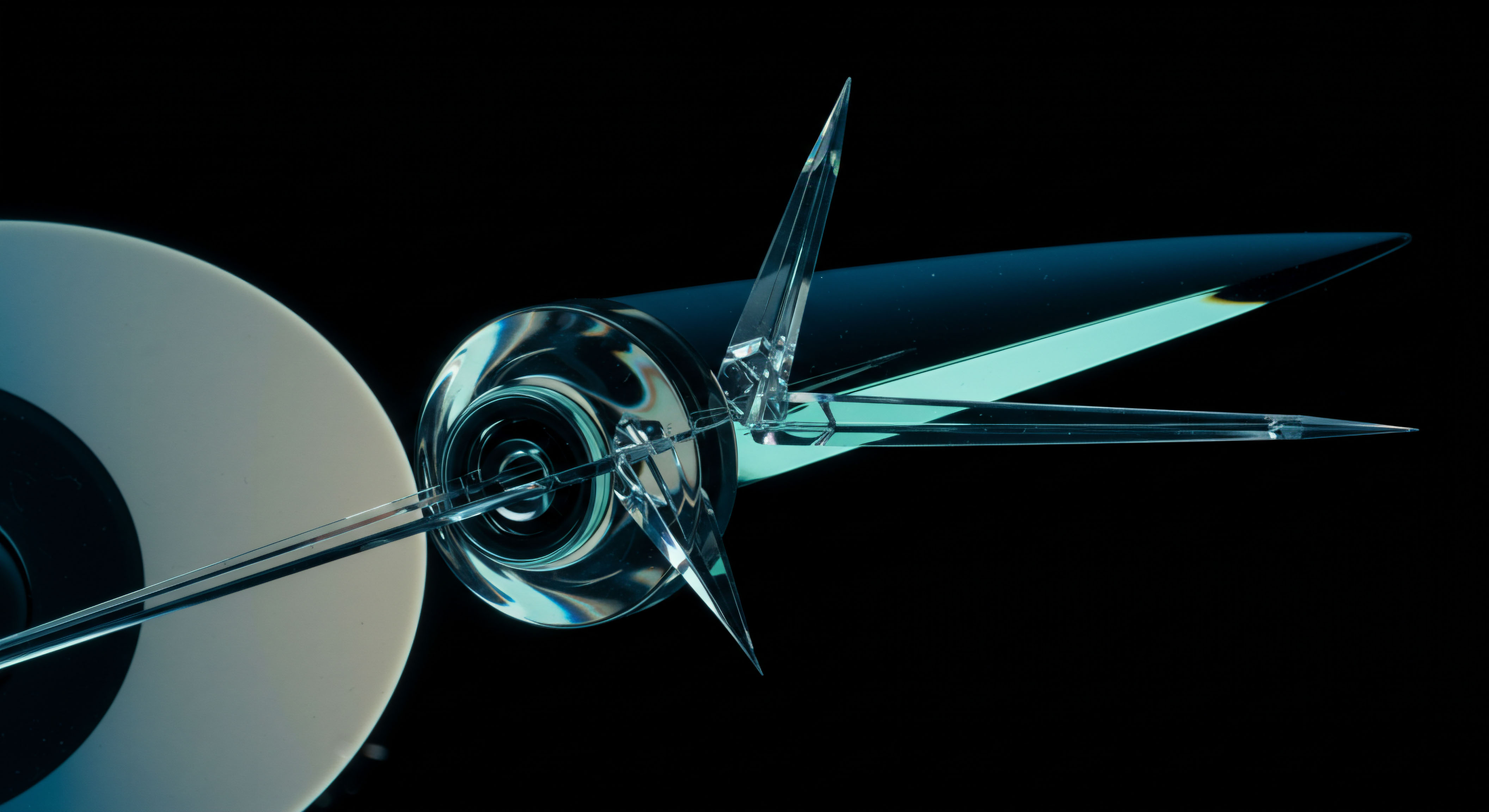

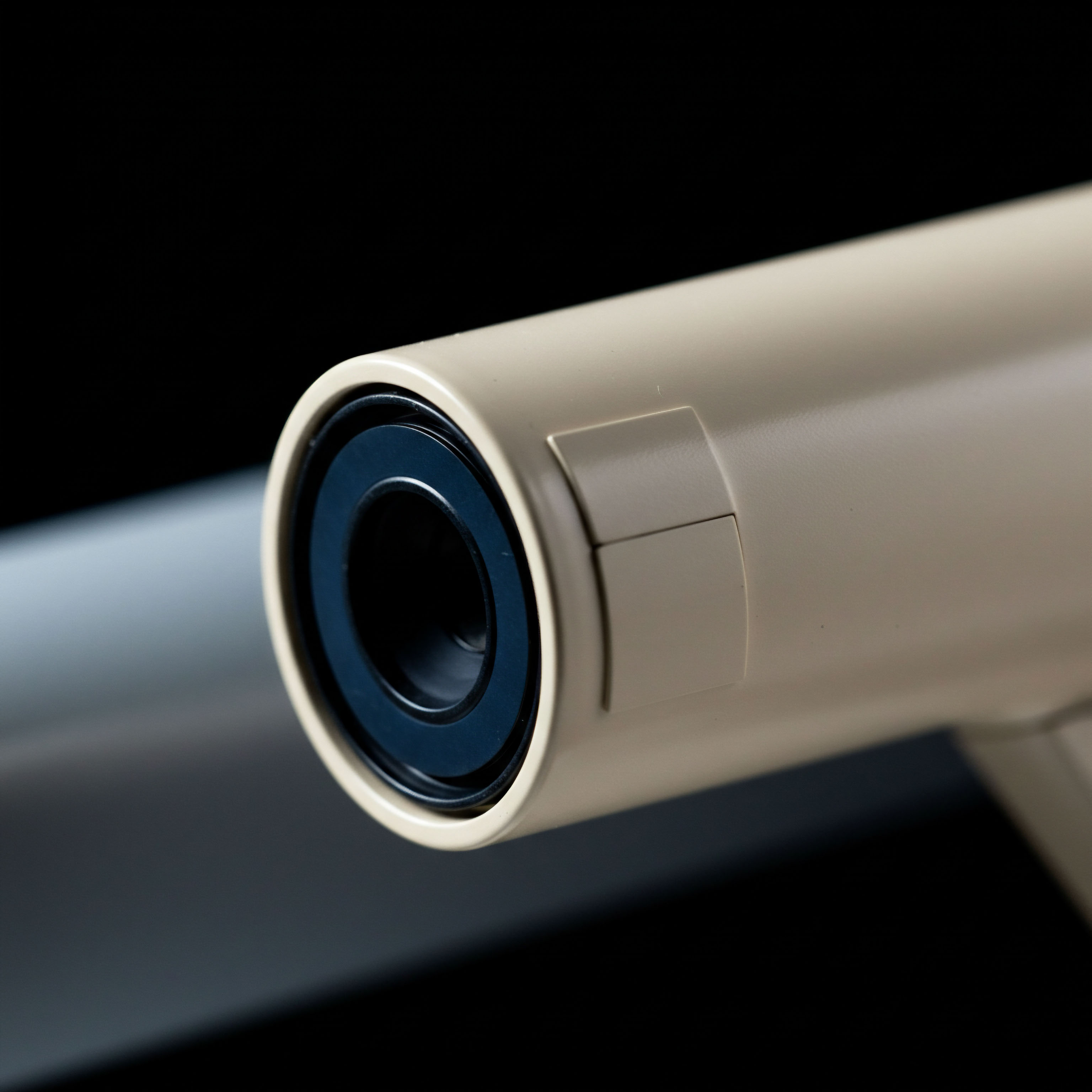

- Photon to Electron Conversion ▴ The optical signal from the fiber cross-connect enters the FPGA card’s transceiver. The transceiver converts the light pulses into electrical signals.

- Physical Layer Decoding ▴ The raw electrical signal is decoded into Ethernet frames. This happens at the physical layer of the networking stack, implemented directly in the FPGA’s hardware.

- Packet Filtering and Parsing ▴ The FPGA logic immediately inspects the Ethernet and IP headers. If the packet is part of a market data feed the system is monitoring, it is passed on. The logic then parses the UDP header and extracts the payload containing the exchange message.

- Exchange Protocol Decoding ▴ The payload is decoded according to the exchange’s specific protocol. The FPGA logic identifies the message type, instrument ID, price, and volume. This is a complex state machine that understands the native language of the exchange.

- Application of Trading Logic ▴ This is the core of the arbitrage. The decoded market state is fed into the trading logic, which is a network of logic gates configured to represent the arbitrage model. For example ▴ IF (Instrument_A_Price < Theoretical_Value) THEN (Generate_Buy_Order). This is not a software if statement; it is a physical circuit.

- Order Packet Construction ▴ If the logic is triggered, a new circuit path on the FPGA constructs a valid order packet in the exchange’s order entry protocol (e.g. OUCH). This includes populating fields for price, quantity, and other parameters.

- Transmission ▴ The newly constructed order packet is sent back out through the transceiver, converted to an optical signal, and sent down the cross-connect to the exchange’s order matching engine.

How Do FPGAs Quantitatively Reduce Latency?

The performance difference is stark. The table below provides a hypothetical but realistic breakdown of the latency budget for a single tick-to-trade event, illustrating where an FPGA-based system gains its advantage.

| Process Step | CPU-Based System Latency (ns) | FPGA-Based System Latency (ns) | Primary Source of Latency |

|---|---|---|---|

| Network Interface Card | ~1,000 – 2,000 | ~100 – 200 | DMA transfers to host memory |

| OS Kernel/Network Stack | ~2,000 – 5,000 | 0 (Bypassed) | Interrupts, context switches, data copies |

| Application Logic | ~1,000 – 10,000+ | ~50 – 500 | CPU instruction pipeline, cache misses |

| Order Encoding & Transmission | ~2,000 – 5,000 | ~50 – 150 | Kernel/driver overhead |

| Total Jitter (Variance) | High (microseconds) | Low (nanoseconds) | Software stack unpredictability |

Advanced Risk Mitigation Protocols in Silicon

The FPGA’s role extends beyond pure speed to encompass a suite of hard-coded risk controls that function with the same deterministic low latency. This makes the system safer by embedding risk management directly into the execution path.

By hard-coding risk checks into the FPGA, a firm creates a safety layer that is physically incapable of being bypassed by errant software, providing a powerful, deterministic backstop against catastrophic errors.

A primary execution risk is acting on stale or incomplete market data. As discussed, A/B feed arbitration directly mitigates this at the hardware level. Another category of risk is erroneous order entry. A “fat-finger” error in software could send an order for 1,000,000 shares instead of 1,000.

Pre-trade risk checks can be implemented in the FPGA’s logic. These circuits can validate every outgoing order packet against a set of rules:

- Maximum Order Size ▴ The logic will block any order exceeding a pre-defined quantity.

- Price Collars ▴ The circuit will prevent orders from being sent that are too far away from the last traded price.

- Position Limits ▴ The FPGA can maintain a real-time state of the current position and block any new order that would breach a firm-wide limit.

Because these checks are in hardware, they execute in nanoseconds. A software-based check would occur far too late in the process to be effective for a latency-sensitive strategy. The FPGA ensures the risk check happens before the order is even fully formed for transmission, providing a level of safety that is inseparable from the act of execution itself.

References

- “FPGAs Grow Beyond Low-Latency Roots.” Markets Media, 12 Jan. 2015.

- Denholm, Stewart, et al. “Network-Level FPGA Acceleration of Low Latency Market Data Feed Arbitration.” IEICE Transactions on Information and Systems, vol. E97-D, no. 12, 2014, pp. 2888-2898.

- “Latency Arbitrage Models.” QuestDB, Accessed 25 July 2024.

- Williston Hayes. “FPGAs and low latency trading.” FPL2020 – 30th International Conference on Field-Programmable Logic and Applications, 2 Sept. 2020. YouTube.

Reflection

The integration of Field-Programmable Gate Arrays into financial trading systems marks a profound architectural shift. It forces a re-evaluation of where a firm’s intellectual property truly resides. When the core trading strategy is no longer an algorithm expressed in C++ but a configuration of logic gates described in Verilog, the lines blur.

The institution becomes as much a hardware engineering firm as a financial one. The source of its competitive advantage is not just its quantitative models, but the physical instantiation of those models in silicon.

This raises a fundamental question for any trading entity ▴ what is the core business? Is it predicting market direction, or is it building a superior machine to react to it? The use of FPGAs suggests the latter is becoming inseparable from the former.

The knowledge gained from mastering these systems is a component in a much larger operational framework. It implies that a lasting edge in modern markets is achieved not by simply having a better strategy, but by building a fundamentally superior system for executing that strategy at the most granular level of market interaction.

Glossary

Latency Arbitrage

Trading System

Execution Risk

Order Packet

Market Data

Fpga

Trading Logic

Deterministic Latency

A/b Feed Arbitration

Colocation

Cross-Connect

Smartnic

Precision Time Protocol

Tick-To-Trade