Concept

The imperative to manage market access risk, codified in SEC Rule 15c3-5, represents a foundational parameter of modern electronic trading systems. From an architectural perspective, this rule is a set of non-negotiable, real-time validation requirements that must be applied to every order entering the market. The core challenge resides in the operational impact of these checks. In a software-based environment, the process of verifying each order against a series of financial and regulatory limits introduces latency.

This latency is characterized by its variability and unpredictability, an attribute known as jitter. For any trading system where execution speed is a determinant of performance, such unpredictable delays are structurally compromising.

Hardware acceleration provides a direct architectural solution to this problem. It reframes the enforcement of 15c3-5 from a sequential, software-level task to a parallel, hardware-level function. By utilizing Field-Programmable Gate Arrays (FPGAs), risk checks are moved from the host server’s CPU and operating system directly into the network data path. The checks become an intrinsic part of the data’s journey from the client to the exchange, executed “on the wire” at line rate.

This approach fundamentally alters the nature of compliance-related latency. It becomes a deterministic, minimal, and predictable component of the overall tick-to-trade latency, measured in nanoseconds rather than microseconds or even milliseconds. The role of hardware acceleration, therefore, is to integrate the mandate of 15c3-5 into the very fabric of the trading infrastructure, ensuring compliance without sacrificing the system’s core function of high-performance execution.

Hardware acceleration transforms mandatory 15c3-5 risk checks from a source of unpredictable software latency into a deterministic, nanosecond-level function integrated directly into the trading data path.

Deconstructing SEC Rule 15c3-5

SEC Rule 15c3-5, often called the Market Access Rule, was adopted by the U.S. Securities and Exchange Commission to govern brokers and dealers who provide access to the market. The rule mandates the establishment of risk management controls and supervisory procedures designed to mitigate the financial, regulatory, and operational risks associated with market access. This includes direct market access (DMA) and sponsored access arrangements, where clients use the broker-dealer’s market participant identifier (MPID) to send orders directly to an exchange. The rule effectively prohibits “unfiltered” or “naked” access, requiring that every order passes through the broker-dealer’s pre-trade risk controls before reaching the execution venue.

From a systems engineering viewpoint, the rule specifies several categories of required checks:

- Financial Risk Management ▴ These controls are designed to prevent the entry of orders that could lead to excessive financial exposure for the broker-dealer. This includes pre-set credit or capital thresholds for each client. For instance, a check must ensure that the notional value of a new order, when aggregated with existing open orders, does not exceed a client’s established limit.

- Regulatory Risk Management ▴ This encompasses a broader set of checks to ensure compliance with all applicable securities laws and rules on a pre-order basis. A key component is the prevention of erroneous orders. This involves checks for order size, price, and potential duplication. For example, the system must be able to reject an order to sell 1,000,000 shares of a stock when the intended size was 10,000, a classic “fat-finger” error. It must also identify and block orders that are unusually far from the current market price or appear to be duplicates of recently submitted orders.

The Architectural Challenge of Software Based Controls

A conventional approach to implementing 15c3-5 checks involves software running on a server. When an order is received, the server’s CPU must pause its other tasks, load the order details, retrieve the relevant risk parameters from memory, execute a series of conditional checks (if-then statements), and then, if all checks pass, forward the order to the exchange. This entire process is subject to the inherent limitations of general-purpose computing architectures.

The primary issue is the reliance on a sequential processing model. A CPU executes instructions one after another. Even with multiple cores, the management of these tasks by the operating system (OS) introduces non-determinism. The OS may interrupt the risk-check process to handle another task, a network event, or a system call.

This “context switching” adds unpredictable delays. Furthermore, the time it takes to retrieve risk parameters can vary depending on whether the data is in the CPU’s fast L1 cache, slower L2/L3 cache, or main system RAM. These factors combine to create latency that is not only significant but, more importantly, inconsistent. For a high-frequency trading strategy that depends on reacting to market data within a few microseconds, a sudden delay of tens or hundreds of microseconds caused by OS jitter can be the difference between a successful trade and a missed opportunity.

Strategy

The strategic adoption of hardware acceleration for 15c3-5 compliance is centered on achieving a state of “compliance without compromise.” This strategy recognizes that in competitive electronic markets, latency is a primary determinant of execution quality. A firm’s ability to respond to market events faster than its competitors is a tangible asset. The latency introduced by software-based risk controls directly degrades this asset. The strategic objective, therefore, is to architect a trading system where regulatory compliance and high performance are not mutually exclusive goals but are instead fused into a single, coherent execution fabric.

This strategy moves beyond viewing 15c3-5 as a mere regulatory hurdle. It reframes it as a system specification that must be met with the most efficient engineering solution available. The choice between a software-based and a hardware-accelerated implementation becomes a fundamental strategic decision about the firm’s technological posture and competitive positioning. A software-first approach implicitly accepts a performance compromise, relegating the firm to a slower tier of market participants.

A hardware-first strategy, utilizing FPGAs, is an explicit commitment to maintaining top-tier performance by building the required risk controls directly into the high-speed data path. This ensures that every order is compliant while adding only a minimal, deterministic latency overhead.

Why Is a Hardware First Strategy Superior?

A hardware-first strategy provides a structural advantage that is difficult for software-based systems to replicate. The core of this advantage lies in parallelism and determinism. An FPGA is a “Field-Programmable Gate Array,” a semiconductor that can be configured by a developer after manufacturing. Instead of running sequential instructions on a CPU, an FPGA implements the logic of the risk checks directly in hardware circuits.

This allows for true parallel processing. When an order packet arrives, an FPGA can perform multiple checks simultaneously. One block of logic can be verifying the order size while another checks the price against market data and a third validates the client’s credit limit. All these operations happen at the same time, in a predictable number of clock cycles.

This results in a total processing time that is extremely low and, crucially, highly consistent. This consistency, or determinism, is a key strategic benefit. It eliminates the jitter associated with software systems, allowing trading algorithms to be designed with a precise understanding of the system’s response time.

Adopting a hardware-first strategy for 15c3-5 compliance is a commitment to top-tier performance by embedding risk controls into the execution fabric, thereby eliminating the performance compromise inherent in software-based solutions.

Comparative Latency Analysis

The strategic decision to use hardware acceleration is clarified by a direct comparison of the latency characteristics of software versus FPGA-based pre-trade risk systems. The table below illustrates the orders-of-magnitude difference in performance, which forms the basis of the competitive advantage.

| Latency Metric | Software-Based System (CPU/OS) | Hardware-Accelerated System (FPGA) |

|---|---|---|

| Average Latency | 10 – 100+ microseconds (µs) | 200 – 800 nanoseconds (ns) |

| Worst-Case Latency (Jitter) | Can spike to several milliseconds (ms) due to OS/network events | Highly deterministic, minimal deviation from average |

| Processing Model | Sequential (instructions executed one by one) | Parallel (multiple checks performed simultaneously in logic) |

| Primary Latency Source | OS context switching, cache misses, PCIe bus transfers, network stack | Logic gate propagation delay, fixed pipeline depth |

| Impact on Trading Strategy | Unsuitable for most latency-sensitive strategies; introduces uncertainty | Enables ultra-low latency strategies; provides predictable response times |

The Strategic Implications for Business Models

The implementation choice for 15c3-5 controls has direct consequences for a firm’s business model and the services it can offer. For broker-dealers offering market access to sophisticated clients like proprietary trading firms, the latency of their risk-control infrastructure is a key selling point.

- High-Performance Market Access ▴ By using FPGAs, a broker-dealer can offer its clients market access with the lowest possible pass-through latency. This is a critical competitive differentiator for attracting and retaining high-frequency trading clients who measure their performance in nanoseconds. The broker can guarantee a certain level of performance for its risk-checking gateway, which is a powerful marketing tool.

- Enhanced Risk Management ▴ While speed is a primary benefit, the deterministic nature of FPGAs also enhances the reliability of risk controls. The system’s behavior is predictable, reducing the tail risk of a software bug or system slowdown causing a catastrophic failure in risk management during volatile market conditions. This operational robustness is a key strategic asset.

- Enabling Advanced Strategies ▴ The ultra-low latency provided by hardware acceleration allows the firm and its clients to deploy more complex, latency-sensitive trading strategies. These could include statistical arbitrage, cross-venue latency arbitrage, or sophisticated market-making algorithms that require rapid responses to fleeting opportunities. A software-based system would render many of these strategies unviable.

Execution

The execution of a hardware-accelerated 15c3-5 compliance system is a matter of precision engineering. It involves integrating a specialized FPGA-based appliance into the trading infrastructure in a way that intercepts and processes order flow before it reaches the exchange. This appliance, often a specialized network interface card (SmartNIC) or a standalone server, becomes the gatekeeper for all market access, enforcing the rules mandated by 15c3-5 at the speed of hardware. The implementation requires a deep understanding of both the regulatory requirements and the low-level mechanics of network data processing and FPGA development.

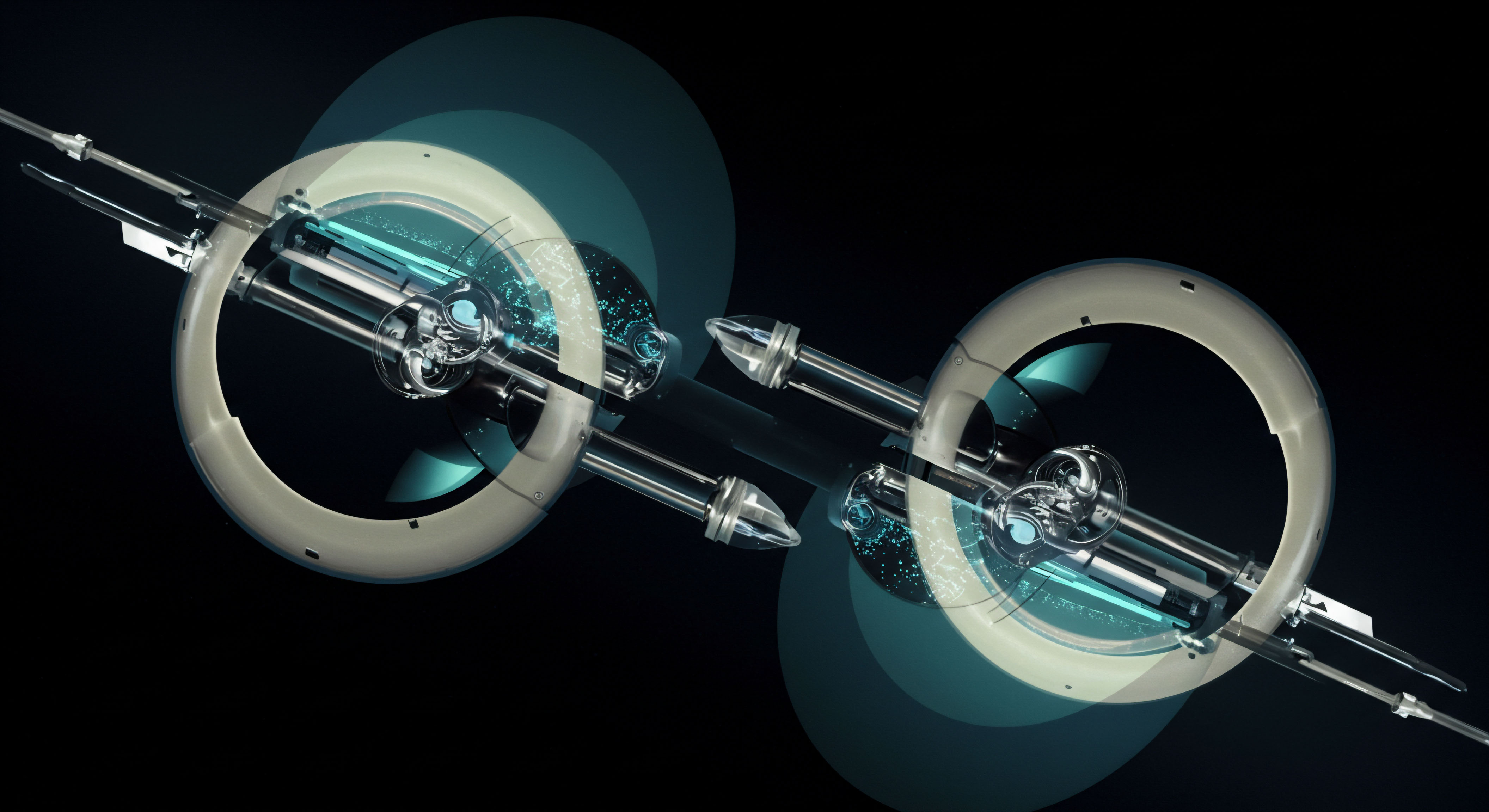

The core of the execution lies in designing the “gateware” ▴ the logic that is programmed onto the FPGA. This gateware defines a data pipeline through which every order packet must travel. Each stage in the pipeline performs a specific function, from parsing the incoming network packet to executing the various risk checks in parallel.

The output of this pipeline is either the original order, now validated and ready to be sent to the exchange, or a rejection message sent back to the originator. The entire process is designed to be completed within a few hundred nanoseconds.

Anatomy of an FPGA Based Pre-Trade Risk Check System

A typical FPGA-based pre-trade risk check (PTRC) system is comprised of several distinct logical blocks implemented within the FPGA’s fabric. The journey of an order through this system is a high-speed, deterministic process.

- Packet Ingress and Parsing ▴ The process begins when a network packet containing a trade order arrives at the physical port of the FPGA appliance. The first logic block is a low-latency Ethernet MAC (Media Access Control) that receives the packet. Immediately, a dedicated FIX (Financial Information eXchange) protocol parser begins to decode the message. This parser is not a piece of software; it is a state machine implemented in hardware that extracts the critical fields ▴ such as Ticker, Side, OrderQty, Price, and Account ▴ directly from the raw packet data.

- Parallel Risk Validation ▴ Once the key fields are extracted, they are fed simultaneously into multiple, independent risk-check modules. This is the heart of the hardware acceleration advantage.

- A Size and Value Check Module compares the ‘OrderQty’ and ‘Price’ against pre-configured limits for the specific instrument and account. For example, it checks if the order quantity exceeds the maximum permissible shares and if the total notional value exceeds the account’s single-order limit.

- A Credit Check Module accesses on-chip memory (Block RAM) that stores the current credit exposure for the client’s account. It calculates the notional value of the new order and checks if adding it would breach the total exposure limit.

- A Duplicate Order Check Module calculates a hash of the key order parameters and checks it against a list of recent order hashes stored in another block of on-chip memory. This allows it to detect and reject potential duplicate submissions instantly.

- A Regulatory and Compliance Module checks the order against other rules, such as whether the security is on a restricted list or if the order type is permitted for the given account.

- Decision and Forwarding Logic ▴ The outputs of all parallel risk-check modules (simple pass/fail signals) are fed into a final decision logic gate. If all signals are ‘pass’, the original, unmodified order packet is forwarded to the exchange-facing Ethernet MAC for egress. The latency added is simply the time it took for the packet to traverse the fixed logic path. If any signal is ‘fail’, the packet is dropped, and a rejection message is generated and sent back to the client. Simultaneously, a log of the rejected order and the reason for the failure is generated for compliance and audit purposes.

How Are Risk Parameters Configured in Hardware?

A common question is how a firm can manage and update risk limits that are baked into hardware. The solution is a hybrid architecture. The “data plane,” where the high-speed order processing occurs, is on the FPGA. The “control plane” is a software application, often with a graphical user interface (GUI), that runs on a standard server.

This software allows risk managers to set, adjust, and monitor all the 15c3-5 parameters in real-time. When a risk manager updates a credit limit, the software sends a low-level command over the PCIe bus to the FPGA, which updates the specific memory location or register on the chip that holds that limit. This allows for the dynamic control of a software system combined with the raw performance of a hardware implementation.

The execution of a hardware-accelerated compliance system involves programming an FPGA with a deterministic data pipeline that parses, validates, and forwards orders in nanoseconds, merging the rigidity of hardware with the flexibility of software-based control.

Quantitative Analysis of Latency Components

To fully appreciate the performance difference, it is useful to break down the latency contributions at each stage of the process for both a software and a hardware system. The following table provides a granular, quantitative model of where time is spent in each architecture.

| Processing Stage | Software-Based System (Typical Latency ns) | FPGA-Based System (Typical Latency ns) | Notes |

|---|---|---|---|

| Network Ingress (NIC to Memory) | 2,000 – 5,000 ns | 50 – 100 ns | Software path involves DMA transfer over PCIe bus to system RAM. FPGA processes directly from the network buffer. |

| OS/Kernel Network Stack | 5,000 – 20,000+ ns | 0 ns | FPGA solutions often use kernel-bypass techniques, eliminating this entire layer of software overhead. |

| Application-Level Parsing | 1,000 – 5,000 ns | 40 – 80 ns | CPU parsing is sequential. FPGA parsing is a parallel hardware state machine. |

| Risk Check Execution | 2,000 – 50,000+ ns | 60 – 200 ns | Software checks are conditional and access different memory locations, causing high variability. FPGA checks are parallel and deterministic. |

| Decision and Egress | 2,000 – 10,000 ns | 50 – 100 ns | Software path requires another trip through the OS network stack. FPGA forwards directly to the egress port. |

| Total Typical Latency | 12,000 – 90,000+ ns (12-90 µs) | 200 – 480 ns | The software path is also subject to extreme outliers (jitter), while the FPGA path is highly deterministic. |

References

- U.S. Securities and Exchange Commission. “Final Rule ▴ Risk Management Controls for Brokers or Dealers with Market Access.” SEC Release No. 34-63241; File No. S7-03-10, 3 Nov. 2010.

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- Lockwood, John, and Rob D’Arco. “The Low Latency FPGA Revolution ▴ The Race To Zero.” Rival Systems, 17 May 2017.

- “FPGA Pre-Trade Risk Check.” Algo-Logic Systems, Inc. 2023.

- “Why More Trading Firms Are Moving to FPGA for Low-Latency Gains.” Magmio, 1 July 2025.

- Lehalle, Charles-Albert, and Sophie Laruelle, editors. Market Microstructure in Practice. World Scientific Publishing, 2013.

- Financial Industry Regulatory Authority. “FINRA Report on Risk Management Practices for Proprietary Trading Firms.” FINRA, 2015.

- U.S. Securities and Exchange Commission. “Small Entity Compliance Guide ▴ Rule 15c3-5 – Risk Management Controls for Brokers or Dealers with Market Access.” 6 Jan. 2011.

- “Thematic assessment on pre-trade controls implemented by investment service providers engaging in algorithmic trading.” Finanssivalvonta, 28 Jan. 2025.

- “Best Practices For Automated Trading Risk Controls And System Safeguards.” FIA, July 2024.

Reflection

The integration of hardware acceleration into the framework of 15c3-5 compliance marks a significant point in the evolution of trading systems. It demonstrates a move towards an architecture where regulation and performance are engineered as a unified whole. The knowledge that such systems are not only possible but are actively deployed prompts a re-evaluation of what constitutes a truly robust operational framework.

It invites consideration of where else in the trading lifecycle architectural choices can create a decisive structural advantage. The decision to implement risk controls in hardware is a statement about a firm’s commitment to operational excellence, transforming a compliance necessity into a competitive asset.

What Is the True Cost of Software Based Latency?

The discussion often centers on the microseconds lost, but the strategic cost is far greater. It is measured in the trading strategies that cannot be deployed, the client segments that cannot be served, and the tail risks that are magnified by non-deterministic systems. Reflecting on the true, holistic cost of software-based latency can reframe investment in hardware from an expense to a foundational capability. It becomes the bedrock upon which a new tier of performance and reliability can be built, securing the firm’s position in an increasingly automated and competitive market landscape.

Glossary

Sec Rule 15c3-5

Market Access

Jitter

Hardware Acceleration

Tick-To-Trade

Securities and Exchange Commission

Risk Management Controls

Risk Management

15c3-5 Compliance

Risk Controls

Deterministic Latency

Every Order

Fpga

Pre-Trade Risk

Pre-Trade Risk Check