Concept

Navigating the volatile currents of digital asset derivatives demands an operational framework defined by absolute precision. A fractional delay in processing market data or executing a trade can transform a potential advantage into a tangible loss. Within this demanding landscape, Field-Programmable Gate Arrays emerge as the computational bedrock for deterministic market response, providing an unparalleled ability to process information and adjust quotes with ultra-low latency.

These specialized integrated circuits, distinct from conventional central processing units or graphics processing units, offer a unique synthesis of parallel processing power and reconfigurability. They represent a fundamental shift in how trading firms approach the execution frontier, moving beyond software-centric limitations to a hardware-accelerated paradigm.

FPGAs operate through a configurable array of logic blocks and programmable interconnects. This intrinsic design allows for the direct implementation of complex financial algorithms and market protocols into the hardware itself. Unlike CPUs, which execute instructions sequentially, FPGAs perform numerous operations concurrently, creating a truly parallel processing environment. This architectural advantage ensures that critical tasks, such as decoding market data feeds or evaluating pricing models, occur with a fixed, predictable latency, eliminating the timing “jitter” that plagues software-based systems.

Achieving predictable, ultra-low latency is paramount in modern financial markets, with FPGAs providing the computational foundation for deterministic responses.

The ability to reconfigure the FPGA’s internal logic on demand grants trading desks an exceptional degree of adaptability. Market microstructure continually evolves, introducing new protocols, data formats, and trading mechanisms. A software-defined system often requires extensive recoding and retesting for such changes, incurring significant development cycles and potential operational disruptions.

FPGAs, by contrast, facilitate rapid adaptation through hardware description languages (HDLs) or high-level synthesis tools, allowing the core logic to be updated with minimal downtime. This flexibility safeguards the integrity of the trading platform against obsolescence while maintaining its speed advantage.

Programmable Logic Fundamentals

The operational core of an FPGA resides in its capacity to implement custom digital circuits. These circuits process data streams directly at the hardware level, bypassing the layers of abstraction inherent in operating systems and general-purpose processors. This direct pathway minimizes overhead, translating into microsecond and even nanosecond-level response times. For quote adjustments, this means the system can react to incoming market data, re-evaluate a derivative’s fair value, and update its bid/ask prices with a speed unachievable through traditional computing architectures.

FPGAs excel in scenarios demanding high throughput combined with minimal latency. Consider the constant influx of market data feeds, often arriving at gigabit rates. A CPU-based system, despite its power, must contend with interrupt handling, context switching, and cache misses, each introducing variability into the processing pipeline.

An FPGA, programmed specifically to parse and filter these feeds, dedicates its resources to this single, critical function, ensuring that every message is processed with consistent, minimal delay. This fundamental difference underpins the strategic value FPGAs bring to the hyper-competitive arena of institutional trading.

Strategy

The strategic deployment of FPGAs within an institutional trading framework centers on securing a deterministic edge in the execution of complex financial instruments. Firms recognize that sustained alpha generation in modern markets necessitates not only speed but also unwavering consistency in execution. FPGAs become instrumental in transforming raw market data into actionable intelligence and immediate order adjustments, particularly within the demanding domain of derivatives.

High-Fidelity Execution Protocols

For instruments like multi-leg options spreads or block trades, high-fidelity execution translates into the precise and simultaneous placement of multiple orders to achieve a desired net position without adverse price movements. FPGA-accelerated systems streamline the entire Request for Quote (RFQ) process. When a quote solicitation protocol arrives, the FPGA can rapidly evaluate the constituent legs of a spread, calculate implied prices, and generate outbound quotes or orders with minimal internal latency. This capability minimizes information leakage and slippage, preserving the integrity of the trading strategy.

FPGAs provide the speed and determinism necessary for precise execution of complex, multi-leg trading strategies.

The deterministic latency offered by FPGAs allows for advanced order types and sophisticated trading applications. Consider automated delta hedging (DDH) for options portfolios. As underlying asset prices fluctuate, the delta of an options position changes, requiring dynamic adjustments to maintain a desired risk profile.

An FPGA-based system can monitor market data, re-calculate delta exposures, and generate hedging orders in real-time, directly in hardware. This level of responsiveness reduces hedging costs and mitigates unintended risk accumulation, a significant advantage in volatile markets.

A firm’s intelligence layer benefits immensely from FPGA integration. Real-time intelligence feeds, providing granular market flow data, can be processed directly by FPGAs at the network interface. This includes parsing exchange protocols, filtering relevant messages, and even performing initial statistical analysis on incoming data streams.

The ability to extract and act upon market signals within nanoseconds allows for rapid identification of arbitrage opportunities, liquidity imbalances, or other fleeting market phenomena. System specialists then leverage this accelerated data to refine models and strategies, augmenting the overall operational control.

Strategic Advantages of FPGA Deployment

- Latency Reduction ▴ FPGAs provide orders of magnitude improvement in tick-to-trade latency, measured in nanoseconds.

- Deterministic Performance ▴ Consistent and predictable execution times eliminate variability, which is crucial for algorithmic reliability.

- Hardware-Level Protocol Processing ▴ Direct decoding and encoding of market data and trading protocols (e.g. FIX, FAST) within hardware.

- Parallel Computation ▴ Simultaneous execution of multiple calculations, ideal for complex pricing models and risk checks.

- Reconfigurability ▴ Adaptability to evolving market rules, protocols, and strategy adjustments without requiring entirely new hardware.

The decision to deploy FPGA technology represents a commitment to achieving superior capital efficiency and execution quality. This technology positions a firm at the vanguard of market response, enabling strategies that exploit even the most ephemeral opportunities. The inherent flexibility of FPGAs, coupled with their speed, ensures that a trading system remains agile and competitive, capable of navigating the intricate dynamics of multi-dealer liquidity pools and over-the-counter options markets with unmatched precision.

| Component/Task | Typical Latency (Software on CPU) | Typical Latency (FPGA Accelerated) | Improvement Factor |

|---|---|---|---|

| Market Data Parsing (FAST/FIX) | 10-50 microseconds | 10-100 nanoseconds | 100x – 1000x |

| Order Book Reconstruction | 5-20 microseconds | 50-200 nanoseconds | 50x – 400x |

| Basic Risk Checks (pre-trade) | 2-10 microseconds | 20-100 nanoseconds | 100x – 500x |

| Simple Quote Generation | 1-5 microseconds | 10-50 nanoseconds | 100x – 500x |

Execution

Operationalizing FPGA technology for ultra-low latency quote adjustments requires a meticulous approach to hardware-software co-design and a deep understanding of market microstructure. The execution phase transforms strategic intent into tangible performance, demanding rigorous attention to technical standards, risk parameters, and quantitative metrics. This section delves into the precise mechanics of implementing and integrating FPGAs within a high-performance trading infrastructure, offering a detailed procedural guide for maximizing execution quality.

Hardware-Software Co-Design Paradigm

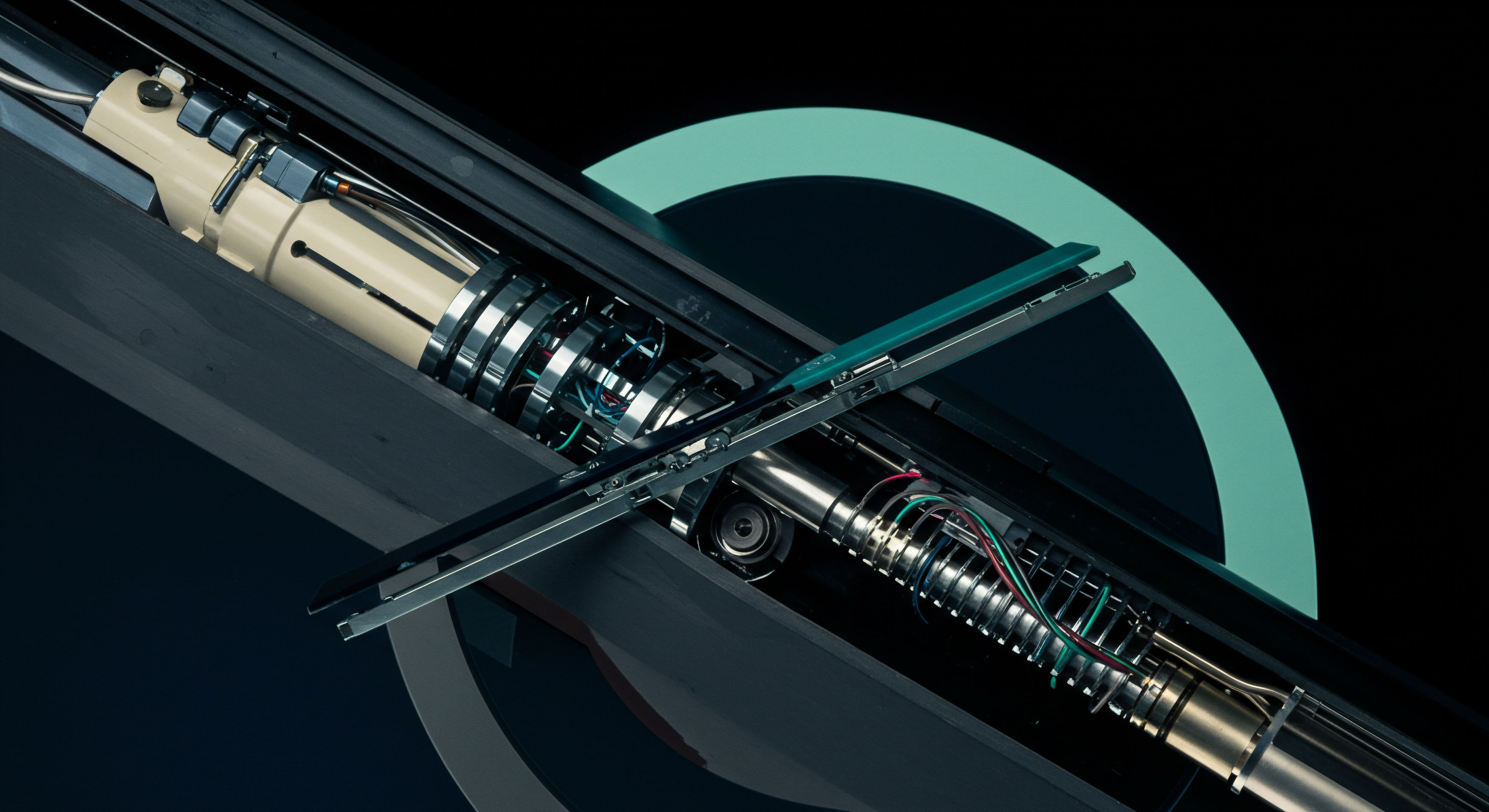

The core of an FPGA-accelerated trading system involves offloading latency-critical functions from general-purpose CPUs to dedicated hardware logic. This typically commences with a comprehensive analysis of the trading workflow, identifying bottlenecks in market data processing, pricing model evaluation, and order generation. Components suitable for hardware acceleration often include network protocol parsing (e.g. Ethernet, IP, UDP, FIX, FAST), order book management, pre-trade risk checks, and elementary pricing calculations.

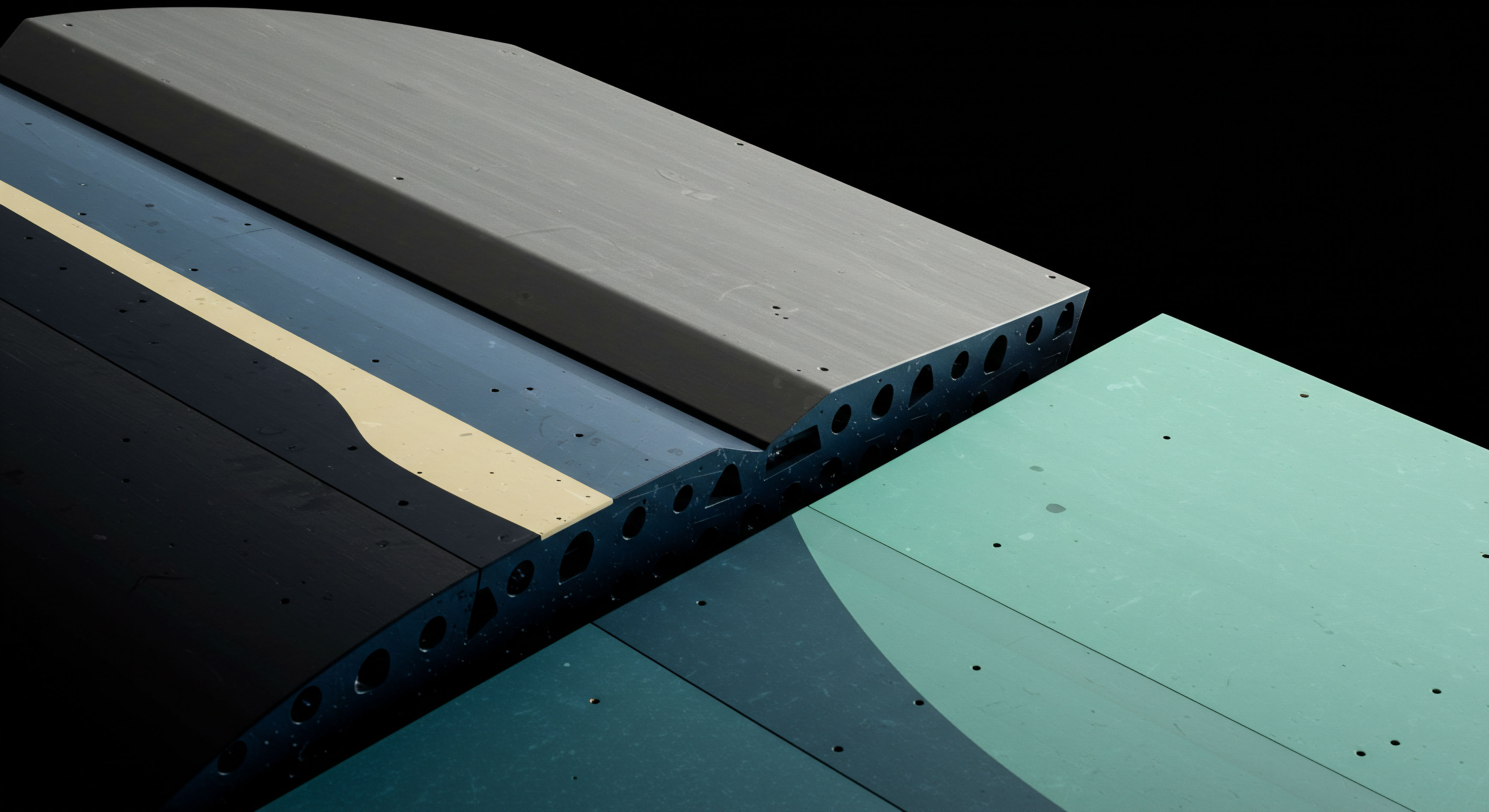

Developers employ Hardware Description Languages (HDLs) such as VHDL or Verilog to describe the digital circuits that will be programmed onto the FPGA. This low-level programming provides granular control over timing and resource utilization, ensuring optimal performance. However, the complexity of HDL development has led to the emergence of High-Level Synthesis (HLS) tools, which allow engineers to describe hardware logic using C, C++, or OpenCL. HLS accelerates the development cycle, making FPGA implementation more accessible while still yielding significant performance gains.

FPGA implementation demands a detailed understanding of hardware-software co-design to achieve optimal latency and throughput.

FPGA Development Lifecycle for Quote Adjustment Engines

- Requirement Definition ▴ Precisely identify latency-critical functions in quote adjustment, including market data ingress, pricing calculations, and outbound order messaging.

- Architectural Design ▴ Develop a hardware-software partition, allocating specific tasks to the FPGA (e.g. market data decoding, order matching) and others to the CPU (e.g. higher-level strategy, risk aggregation).

- HDL/HLS Implementation ▴ Code the FPGA logic using VHDL/Verilog or HLS tools, focusing on pipelining and parallelism for maximum throughput and minimal latency.

- Verification and Simulation ▴ Rigorously test the FPGA logic using hardware-in-the-loop simulation and formal verification methods to ensure functional correctness and timing closure.

- Deployment and Integration ▴ Integrate the FPGA card into the trading server, establishing high-speed communication channels (e.g. PCIe) with the CPU and direct network connectivity.

- Real-Time Monitoring and Optimization ▴ Continuously monitor latency and throughput in live environments, iteratively refining the FPGA design and software stack for ongoing performance enhancements.

Direct Data Path Processing

A hallmark of FPGA-accelerated systems is the direct processing of data streams. Market data packets, upon arrival, can be ingested directly by the FPGA’s network interface. The FPGA then decodes exchange-specific protocols, reconstructs order books, and performs initial calculations ▴ all within the programmable logic.

This bypasses the operating system’s network stack and kernel processing, eliminating sources of unpredictable latency. The resulting processed data, or a derived signal, can then be passed to the CPU for higher-level strategic decisions or directly used to generate outbound quote adjustments.

For options trading, this direct processing is transformative. Complex pricing models, such as Monte Carlo simulations or finite difference methods, often involve numerous iterative calculations. Implementing these directly in FPGA hardware allows for massive parallelism, where hundreds or thousands of simulations run concurrently. This dramatically accelerates the calculation of fair values and sensitivities (e.g.

Greeks), enabling real-time adjustments to quoted prices in response to market movements or changes in implied volatility. The computational speed-up can be orders of magnitude compared to CPU-only solutions.

Integration with Financial Information Exchange (FIX) Protocol

The Financial Information Exchange (FIX) protocol serves as the ubiquitous standard for electronic communication in financial markets. FPGA integration extends to accelerating FIX message processing. Instead of software parsing FIX messages, which introduces latency, dedicated hardware modules within the FPGA can perform FIX encoding and decoding.

This means that an incoming Request for Quote (RFQ) message can be parsed at the hardware level, relevant parameters extracted, and a responsive quote generated and encoded back into a FIX message for transmission, all with minimal delay. This capability is vital for maintaining an edge in bilateral price discovery protocols and anonymous options trading environments.

Pre-trade risk checks, a regulatory imperative, also benefit from FPGA acceleration. These checks, which validate order size, price limits, and exposure limits, can be implemented as concurrent logic within the FPGA. As an order or quote adjustment is generated, it passes through these hardware-enforced risk gates in parallel, adding negligible latency to the critical path.

This ensures compliance without compromising execution speed, a balance difficult to strike with software-only solutions. The robust nature of FPGA logic contributes to the system’s overall resilience and functional integrity.

| FPGA Resource Type | Usage Percentage (Example) | Impact on Performance/Capacity |

|---|---|---|

| Logic Cells (LUTs/FFs) | 65% | Directly impacts the complexity of implemented algorithms and protocols. |

| Block RAMs (BRAMs) | 40% | Stores order book data, pricing model parameters, and market data history. |

| DSP Slices | 80% | Accelerates mathematical operations crucial for pricing models and signal processing. |

| I/O Pins | 25% | Connects to network interfaces (e.g. 10GbE, 40GbE) and host PCIe bus. |

| Clock Resources | 15% | Ensures synchronous operation and high-frequency clocking for low latency. |

The pursuit of ultra-low latency in quote adjustments is a continuous endeavor, requiring an integrated approach where hardware acceleration forms a central pillar. By embedding financial logic directly into programmable silicon, institutions gain a decisive advantage, translating microsecond gains into enhanced profitability and reduced operational risk. The future of high-fidelity execution unequivocally involves these dedicated computational fabrics.

References

- Lockwood, J. Gupte, A. et al. “A Low-Latency Library in FPGA Hardware for High-Frequency Trading (HFT).” IEEE 20th Annual Symposium on High-Performance Interconnects, 2012.

- Boutros, A. Grady, B. Abbas, M. & Chow, P. “Build fast, trade fast ▴ FPGA-based high-frequency trading using high-level synthesis.” International Conference on ReConFigurable Computing and FPGAs, 2017.

- Pottathuparambil, R. Coyne, J. Allred, J. Lynch, W. & Natoli, V. “Low-Latency FPGA Based Financial Data Feed Handler.” IEEE 19th Annual International Symposium on Field-Programmable Custom Computing Machines, 2011.

- Lockwood, J. et al. “FPGA for High-Frequency Trading ▴ Reducing Latency in Financial Systems.” ResearchGate, 2011.

- Neelakandan, A. et al. “FPGA Accelerated Low-Latency Market Data Feed Processing.” Imperial College London, 2010.

- Pottathuparambil, R. et al. “Low Latency FPGA Acceleration of Market Data Feed Arbitration.” Department of Computing, Imperial College London, 2012.

- Haddad, A. et al. “High Frequency Trading Acceleration Using FPGAs.” ResearchGate, 2013.

- Sheng, S. et al. “An Accelerator for Decoding Market Data Based on FPGA.” IEEE International Conference on Field-Programmable Technology (ICFPT), 2017.

- Kilic, M. & Akyol, M.A. “Implementation of High Frequency Trading Technology on FPGA.” Istanbul Technical University Electrical-Electronics Faculty, 2023.

- Orthogone Technologies. “Ultra-low latency trading ▴ Software based or Hybrid FPGA.” Orthogone Technologies, 2023.

- Orthogone Technologies. “Hardware acceleration for ultra-low latency trading systems.” Orthogone Technologies, 2023.

- Wall Street FPGA. “Hardware Acceleration of Monte Carlo Simulation for Option Pricing.” Wall Street FPGA, 2010.

- Goyal, S. et al. “The Role of FPGAs in Modern Option Pricing Techniques ▴ A Survey.” MDPI Electronics, 2022.

- AMD. “Accelerating Option Pricing with Vitis Quantitative Finance.” AMD White Paper, 2019.

Reflection

The deployment of FPGAs for ultra-low latency quote adjustments marks a significant evolution in the operational calculus of institutional finance. Understanding this technological imperative transcends mere technical comprehension; it necessitates introspection into one’s own operational framework. Consider the intrinsic value of deterministic response times in an environment where microseconds define competitive advantage. Does your current system provide the consistent, predictable performance required to navigate the nuanced interplay of liquidity, technology, and risk?

The capacity to adjust quotes with nanosecond precision is a capability, a control surface, that redefines the parameters of what is possible in high-fidelity execution. This knowledge, when internalized, compels a re-evaluation of existing infrastructure, urging a move towards systems that offer not just speed, but a profound architectural advantage. This is not simply about faster trading; it is about building a superior operational framework that provides an enduring strategic edge. The ultimate objective is to master market systems, thereby achieving superior execution and capital efficiency without compromise.

Glossary

Field-Programmable Gate Arrays

Ultra-Low Latency

Parallel Processing

Market Data

Market Microstructure

Quote Adjustments

Deterministic Latency

Capital Efficiency

Execution Quality

Ultra-Low Latency Quote Adjustments