Precision in Market Data Ingestion

In the high-stakes arena of institutional trading, the temporal dimension of market data acquisition dictates a significant portion of competitive advantage. Every nanosecond shaved from the quote capture pipeline directly translates into enhanced informational asymmetry and superior execution outcomes. The relentless pursuit of minimizing latency within this critical initial phase is a foundational imperative for any entity seeking to maintain an edge in contemporary financial markets. Understanding the intricate mechanisms that underpin rapid data processing reveals a deeper appreciation for the operational realities faced by leading firms.

Optimizing quote capture latency involves a complex interplay of hardware, software, and network protocols, all meticulously engineered to extract pricing information from exchange feeds with unparalleled swiftness. The core challenge lies in the sheer volume and velocity of data streams emanating from multiple trading venues. Processing these streams efficiently, normalizing disparate formats, and making them available for algorithmic decision-making requires a processing architecture capable of extraordinary throughput and minimal delay.

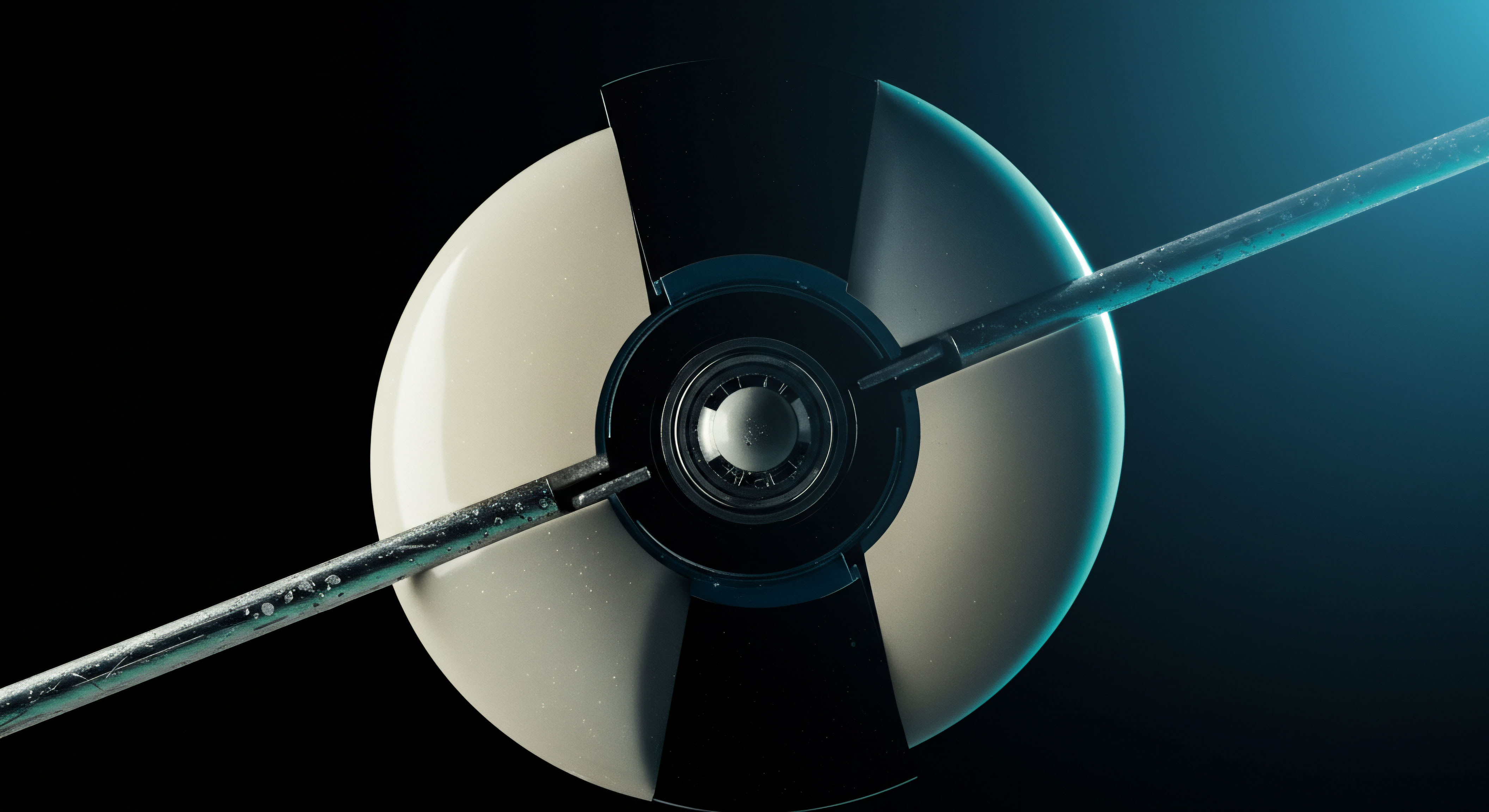

A fundamental component of this optimization strategy involves offloading computationally intensive tasks from general-purpose CPUs to specialized hardware accelerators. These dedicated processing units are designed for specific types of computations, performing them with an efficiency that far surpasses conventional processors. The architectural shift towards acceleration acknowledges that traditional CPU-centric systems encounter bottlenecks when confronted with the demanding real-time requirements of market data processing. These bottlenecks often manifest in increased latency, which can compromise the integrity of price discovery and execution quality.

Hardware accelerators provide a dedicated processing advantage, directly reducing the computational overhead in high-volume market data environments.

The implementation of hardware acceleration fundamentally alters the latency profile of quote capture systems. Rather than contending with the sequential processing limitations of a CPU, which must manage a multitude of diverse tasks, accelerators execute parallel operations with a singular focus. This architectural specialization ensures that critical data parsing, filtering, and timestamping functions are performed at wire speed, thereby preserving the temporal fidelity of incoming quotes. A system designed with this principle in mind effectively mitigates the risk of stale data influencing trading decisions, a paramount concern for all market participants.

Optimizing Data Pipelines with Specialized Processing

The strategic deployment of hardware accelerators within market data pipelines represents a calculated decision to optimize the entire trading lifecycle, beginning with raw quote ingestion. This approach transcends mere speed enhancements, encompassing a holistic re-evaluation of data flow, processing efficiency, and resource allocation. Firms strategize to leverage these specialized components to achieve deterministic latency, ensuring that data arrives at the decision engine within predictable and tightly bound timeframes.

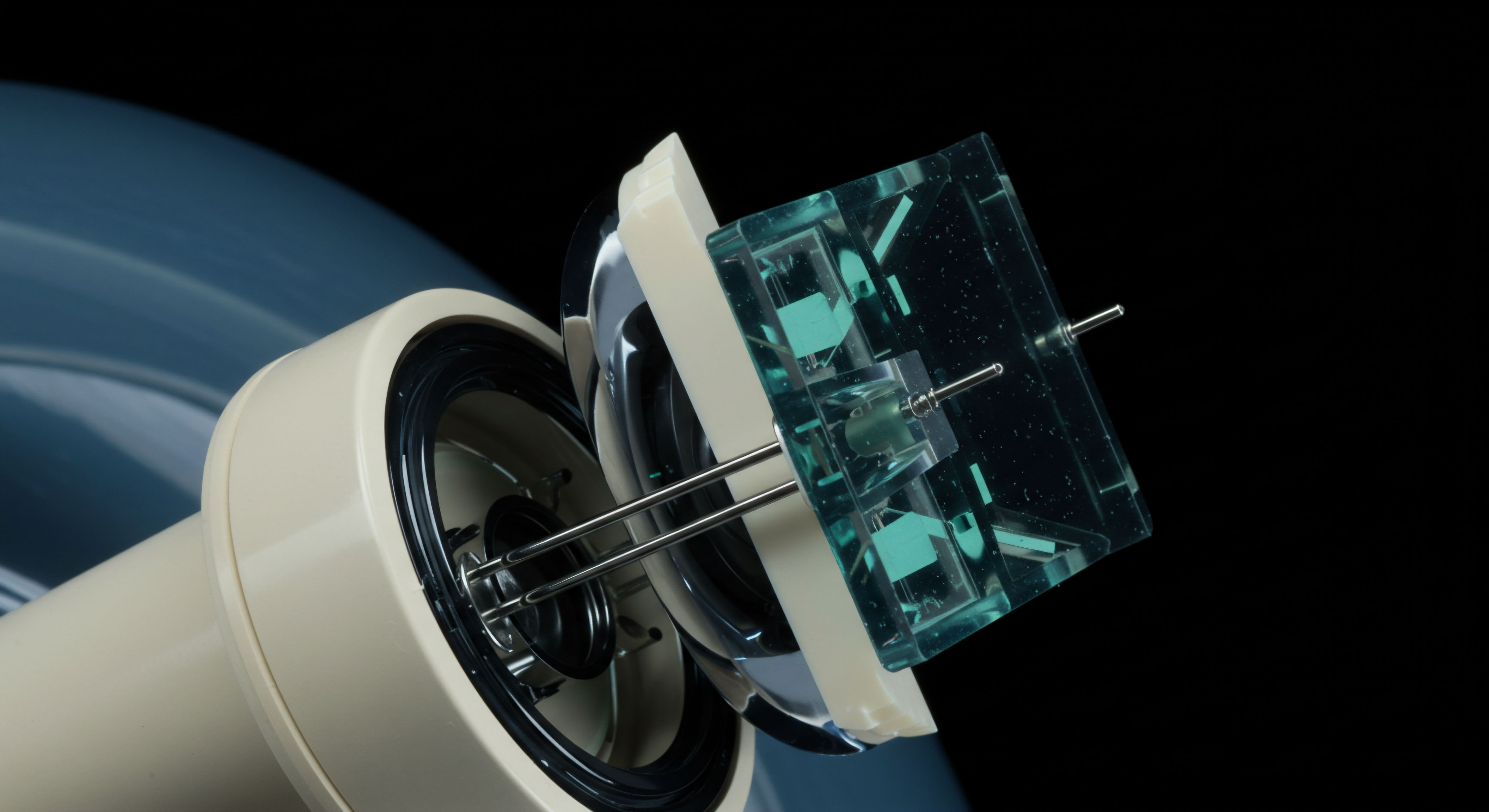

One primary strategic consideration involves selecting the appropriate accelerator technology. Field-Programmable Gate Arrays (FPGAs) and Graphics Processing Units (GPUs) stand as prominent contenders, each offering distinct advantages tailored to specific processing requirements. FPGAs excel in customizability and ultra-low latency operations, making them ideal for tasks requiring bit-level manipulation and deterministic timing, such as network packet processing and direct market data parsing. Their reconfigurable nature permits rapid adaptation to evolving exchange protocols and market microstructure changes.

GPUs, conversely, provide immense parallel processing power, well-suited for high-throughput, computationally intensive tasks that can be broken down into many smaller, independent operations. This includes tasks like complex options pricing models or real-time risk calculations, which, while not directly quote capture, often consume critical CPU cycles that could otherwise be dedicated to data ingestion. A thoughtful integration strategy balances the strengths of these technologies to construct a resilient and high-performance data fabric.

Strategic hardware accelerator selection, primarily FPGAs and GPUs, tailors processing power to specific market data and computational demands.

Another strategic dimension involves the integration of these accelerators into existing infrastructure. This requires careful consideration of data transfer mechanisms, ensuring that the accelerated processing does not introduce new bottlenecks through inefficient data movement between the accelerator and the host system. High-speed interconnects, such as PCIe 4.0 or 5.0, are fundamental to realizing the full potential of these devices. Direct Memory Access (DMA) capabilities become paramount, allowing accelerators to access system memory without burdening the CPU, thereby streamlining the data path.

The strategic shift towards accelerated quote capture also informs the design of advanced trading applications. For instance, in the context of RFQ mechanics, where high-fidelity execution for multi-leg spreads is crucial, accelerated data processing ensures that incoming quotes from multiple dealers are captured, normalized, and presented to the trading algorithm with minimal delay. This rapid ingestion allows for a more accurate and timely assessment of the best available liquidity, significantly reducing information leakage and adverse selection risk during bilateral price discovery.

Furthermore, the intelligence layer within an institutional trading platform benefits immensely from accelerated data processing. Real-time intelligence feeds, which depend on rapidly updated market flow data, gain precision and timeliness. When the raw data foundation is accelerated, subsequent analytical processes ▴ such as anomaly detection or liquidity aggregation ▴ operate on the freshest possible information. This allows system specialists to maintain expert human oversight, intervening with confidence when complex execution scenarios demand their attention, backed by the most current market state.

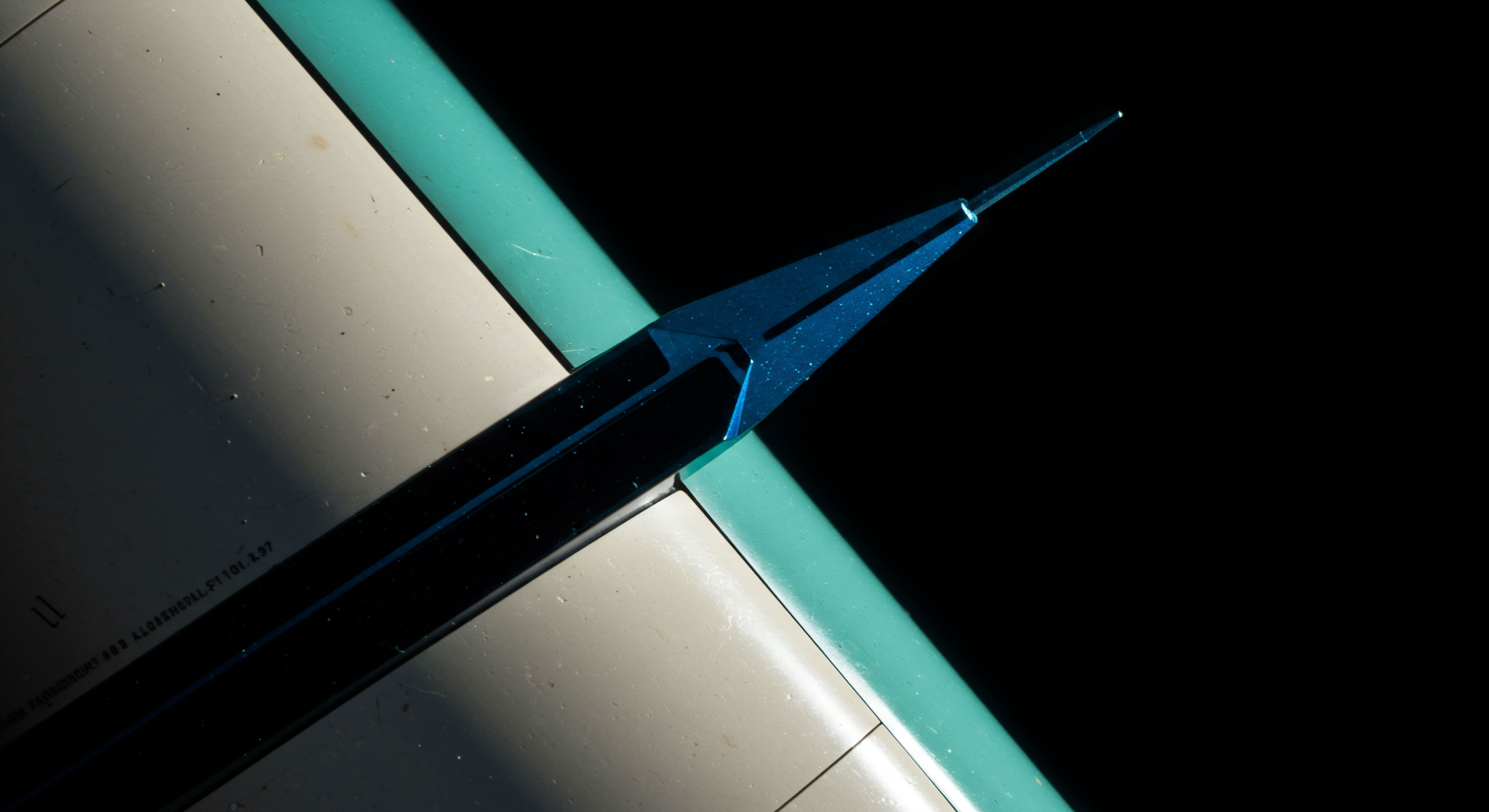

A comprehensive strategy for latency optimization extends beyond simply accelerating data parsing. It also encompasses the careful management of network jitter and operating system overhead. By offloading network protocol stacks onto FPGA cards, for example, firms can bypass the unpredictable latency introduced by kernel-level processing.

This direct hardware interaction provides a more deterministic path for market data, ensuring that the system’s performance remains consistent even under peak market volatility. The overarching goal is to create an execution environment where every component is optimized for speed and reliability.

Operationalizing Ultra-Low Latency Data Pathways

The practical execution of a hardware-accelerated quote capture system demands meticulous attention to granular detail, from physical deployment to software stack optimization. This section outlines the precise mechanics of implementation, focusing on achieving tangible improvements in latency and throughput for institutional trading operations. The journey from conceptual advantage to operational reality involves a series of calculated steps, each contributing to the overarching objective of superior execution.

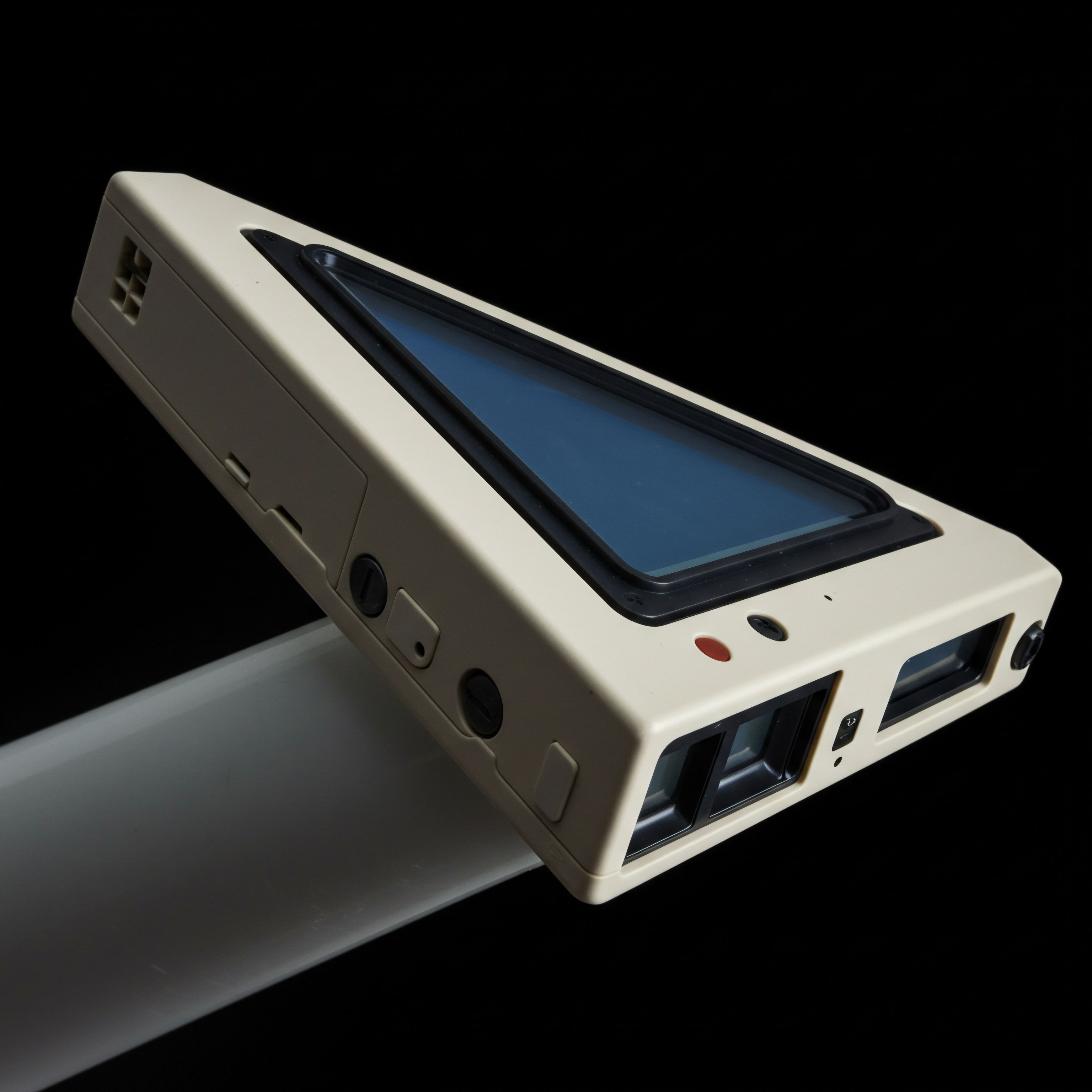

Selecting and Configuring Hardware Accelerators

Choosing the right hardware accelerator is a critical first step. For raw market data ingestion, FPGAs often represent the optimal choice due to their reconfigurability and deterministic, sub-microsecond latency capabilities. These devices are typically integrated as PCIe cards within specialized low-latency servers.

- FPGA Selection ▴ Identify FPGA cards with sufficient logic elements, memory bandwidth, and high-speed network interfaces (e.g. 10/25/40/100 GbE). Consider vendor support for low-latency network stacks and market data protocols.

- Firmware Development ▴ Develop or procure custom FPGA firmware (bitstreams) specifically designed for market data parsing. This includes logic for:

- Network Protocol Decapsulation ▴ Efficiently handling Ethernet, IP, and UDP headers in hardware.

- Market Data Protocol Parsing ▴ Decoding exchange-specific message formats (e.g. ITCH, OUCH, FIX FAST) at wire speed.

- Timestamping ▴ Applying high-precision hardware timestamps to each incoming quote, often synchronized via PTP (Precision Time Protocol).

- Filtering and Normalization ▴ Filtering irrelevant messages and normalizing diverse quote formats into a consistent internal representation.

- Host Interface Optimization ▴ Configure DMA engines on the FPGA to transfer parsed and timestamped data directly into host application memory buffers, bypassing CPU intervention.

Software Stack Integration and Optimization

While hardware provides the raw speed, the software stack must be engineered to complement it, minimizing overhead and ensuring efficient data consumption.

- Kernel Bypass Networking ▴ Implement user-space network drivers (e.g. Solarflare’s OpenOnload, Mellanox’s VMA) to move network processing out of the operating system kernel, further reducing latency and jitter.

- Memory Management ▴ Utilize huge pages and memory pinning to prevent paging and ensure contiguous memory allocation for data buffers, enhancing cache performance.

- Thread Affinity ▴ Pin critical application threads to specific CPU cores, avoiding context switching overhead and cache invalidation.

- Lock-Free Data Structures ▴ Design data structures that permit concurrent access without relying on mutexes or locks, which introduce serialization points and latency.

- Application Logic Refinement ▴ Optimize downstream application logic (e.g. arbitrage engines, order management systems) to consume the accelerated data stream with minimal processing delay.

Performance Metrics and Validation

Quantifying the impact of hardware acceleration requires rigorous measurement and validation against predefined latency targets.

| Component | CPU-Centric Latency (µs) | Hardware-Accelerated Latency (µs) | Improvement Factor |

|---|---|---|---|

| Network Ingestion & Parsing | 10.0 – 20.0 | 0.5 – 2.0 | 5x – 40x |

| Data Normalization | 5.0 – 10.0 | 0.2 – 1.0 | 5x – 50x |

| Application Data Delivery | 2.0 – 5.0 | 0.1 – 0.5 | 4x – 50x |

| Total Quote Capture | 17.0 – 35.0 | 0.8 – 3.5 | ~10x Average |

Measuring end-to-end latency involves injecting precisely timestamped packets at the network ingress point and recording the timestamp when the data becomes available to the trading application. Specialized network tap devices and hardware timestamping cards are indispensable for these measurements. This granular approach ensures that every segment of the data path is accounted for, revealing potential bottlenecks.

Risk Parameters and System Resilience

Implementing high-performance systems introduces unique risk considerations. The complexity of custom hardware and highly optimized software necessitates robust testing and failover mechanisms.

- Redundancy ▴ Deploy multiple, identical accelerated systems in an active-passive or active-active configuration to ensure continuous operation in the event of a hardware or software failure.

- Monitoring ▴ Implement comprehensive real-time monitoring of hardware health (temperature, fan speed, error rates), network statistics (packet loss, retransmissions), and application performance (processing queues, latency percentiles).

- Deterministic Performance ▴ Rigorously test the system under simulated peak market conditions to validate its deterministic latency characteristics and ensure it performs predictably under stress.

- Change Management ▴ Establish stringent change management protocols for firmware updates, driver installations, and application code deployments, given the tight coupling between hardware and software.

Rigorous testing and redundancy protocols are essential for maintaining the integrity of ultra-low latency systems under all market conditions.

The integration of hardware accelerators into a trading system is a continuous process of refinement and optimization. Firms regularly evaluate new hardware generations, assess emerging network protocols, and refine their custom logic to maintain their latency advantage. This persistent pursuit of efficiency ensures that their quote capture capabilities remain at the forefront of market technology, providing a sustained competitive edge in the dynamic landscape of institutional finance. A commitment to this iterative enhancement distinguishes leading firms from their peers, solidifying their position in an ever-evolving market.

| Aspect | Description | Impact on Latency/Throughput |

|---|---|---|

| Firmware Agility | Ability to rapidly update FPGA logic for new exchange feeds or protocol changes. | Minimizes time-to-market for new data sources; sustains low latency against evolving market microstructure. |

| Direct Memory Access (DMA) | Hardware’s ability to read/write system memory independently of the CPU. | Reduces CPU overhead; accelerates data transfer between accelerator and application. |

| Precision Timestamping | Hardware-level timestamping synchronized via PTP or NTP. | Ensures accurate sequencing of market events; critical for arbitrage and TCA. |

| Kernel Bypass | Bypassing OS kernel for network stack processing. | Eliminates OS jitter; provides more deterministic and lower network latency. |

| Resource Isolation | Dedicated CPU cores and memory for critical low-latency processes. | Prevents interference from other system tasks; maintains consistent performance. |

A final, yet crucial, element involves the continuous monitoring of market microstructure. As exchanges introduce new order types, modify matching engine logic, or alter data distribution mechanisms, the optimal hardware acceleration strategy may require adjustments. This constant vigilance ensures that the deployed systems remain perfectly aligned with the prevailing market conditions, allowing for maximum operational efficiency and sustained competitive advantage.

References

- Chiu, J. (2014). High-Frequency Trading ▴ A Practical Guide to Algorithmic Strategies and Trading Systems. John Wiley & Sons.

- Cont, R. (2011). Financial Modeling with Jump Processes. Chapman and Hall/CRC.

- Harris, L. (2003). Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press.

- Lehalle, C.-A. (2009). Market Microstructure in Practice. World Scientific Publishing Company.

- O’Hara, M. (1995). Market Microstructure Theory. Blackwell Publishers.

- Parsons, D. (2019). Low-Latency Programming ▴ The Problem, The Solution, The Future. O’Reilly Media.

- Schwartz, R. A. (2001). Microstructure of Markets ▴ The Financial Market Ecosystem. John Wiley & Sons.

- Wellman, M. P. (2006). Market-Based Control ▴ A Unified Perspective on Distributed Computation. MIT Press.

Strategic Imperatives for Operational Excellence

Considering the intricate landscape of market data acquisition, the implementation of hardware accelerators becomes a defining characteristic of an institution’s operational maturity. This advancement challenges principals to examine their existing technological stack, scrutinizing every millisecond of latency within their data pathways. The knowledge acquired about these specialized processing units serves as a catalyst for introspection, prompting a re-evaluation of how swiftly and precisely market information translates into actionable intelligence.

The conversation extends beyond mere technical specifications; it delves into the strategic implications of possessing a superior data capture mechanism. A firm’s ability to consistently access and process market data with minimal latency directly influences its capacity for price discovery, its effectiveness in mitigating slippage, and its overall capital efficiency. This capability is not an isolated technical achievement; it forms a foundational pillar of an integrated trading ecosystem.

Ultimately, mastering these technological advancements requires a holistic perspective, viewing each component as part of a larger, interconnected system designed for competitive advantage. The commitment to optimizing every layer of the trading infrastructure, from the raw data feed to the final execution instruction, solidifies a firm’s position as a leader. This persistent pursuit of operational excellence empowers institutions to navigate complex market dynamics with confidence and precision, shaping their destiny in the volatile world of digital asset derivatives.

Glossary

Market Data

Hardware Accelerators

Execution Quality

Hardware Acceleration

Deterministic Latency

Market Microstructure

Data Ingestion

Bilateral Price Discovery

High-Fidelity Execution