Concept

The Physicality of Speed in Quote Dissemination

In the domain of electronic markets, the speed of information transmission is a physical constraint, governed by the laws of physics and the limitations of processing architectures. Optimal throughput for quote dissemination is achieved by minimizing the time it takes for a market participant to receive market data, process it, build a responsive quote, and transmit that quote back to the exchange. This entire sequence, known as the tick-to-trade latency, occurs in a timeframe measured in nanoseconds. At this scale, the operational inefficiencies of general-purpose computing systems become profound liabilities.

The standard approach of processing network data through a server’s central processing unit (CPU) introduces significant, non-deterministic delays. These delays arise from the CPU needing to handle operating system tasks, context switching between different processes, and managing complex memory hierarchies.

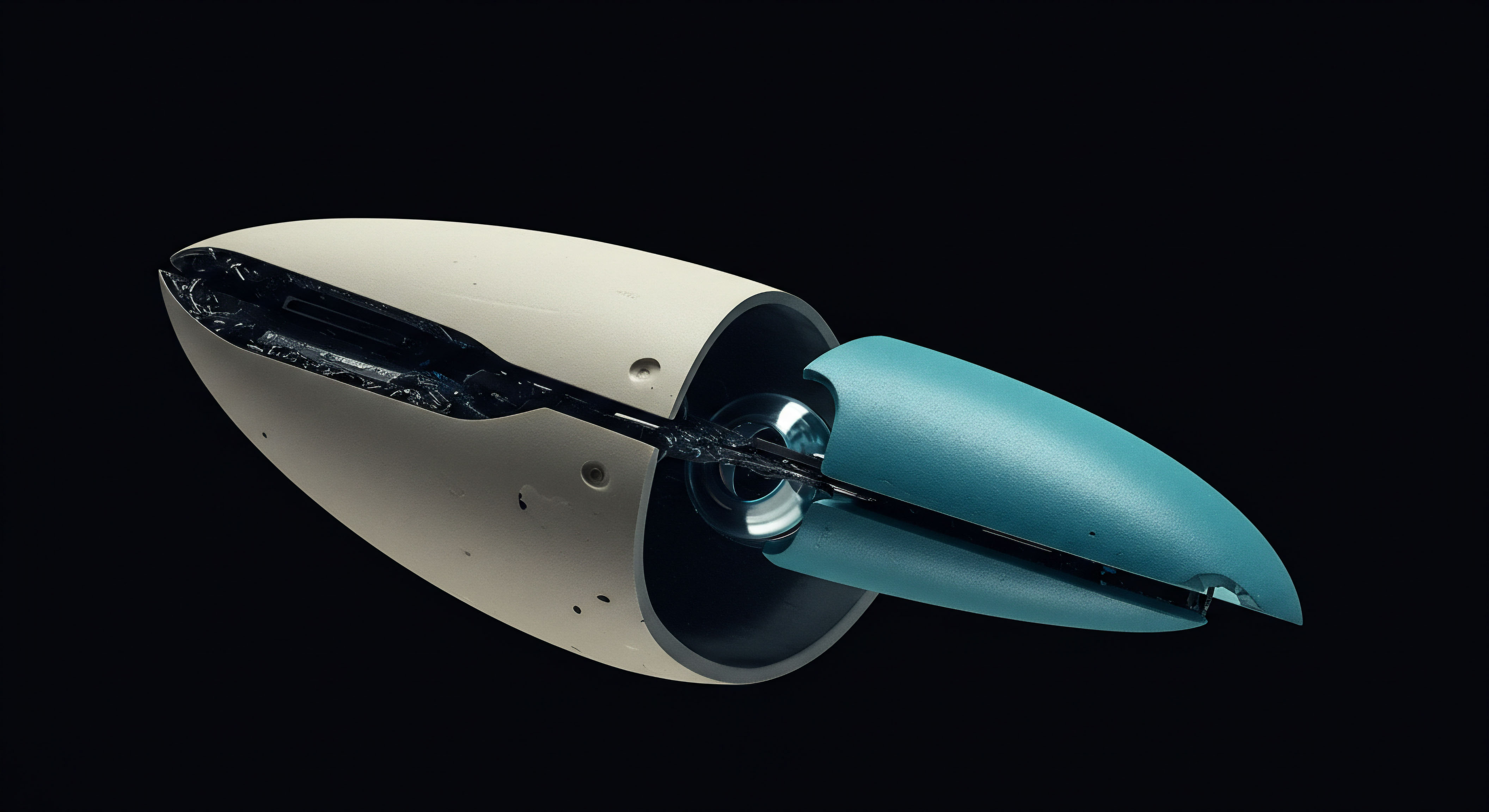

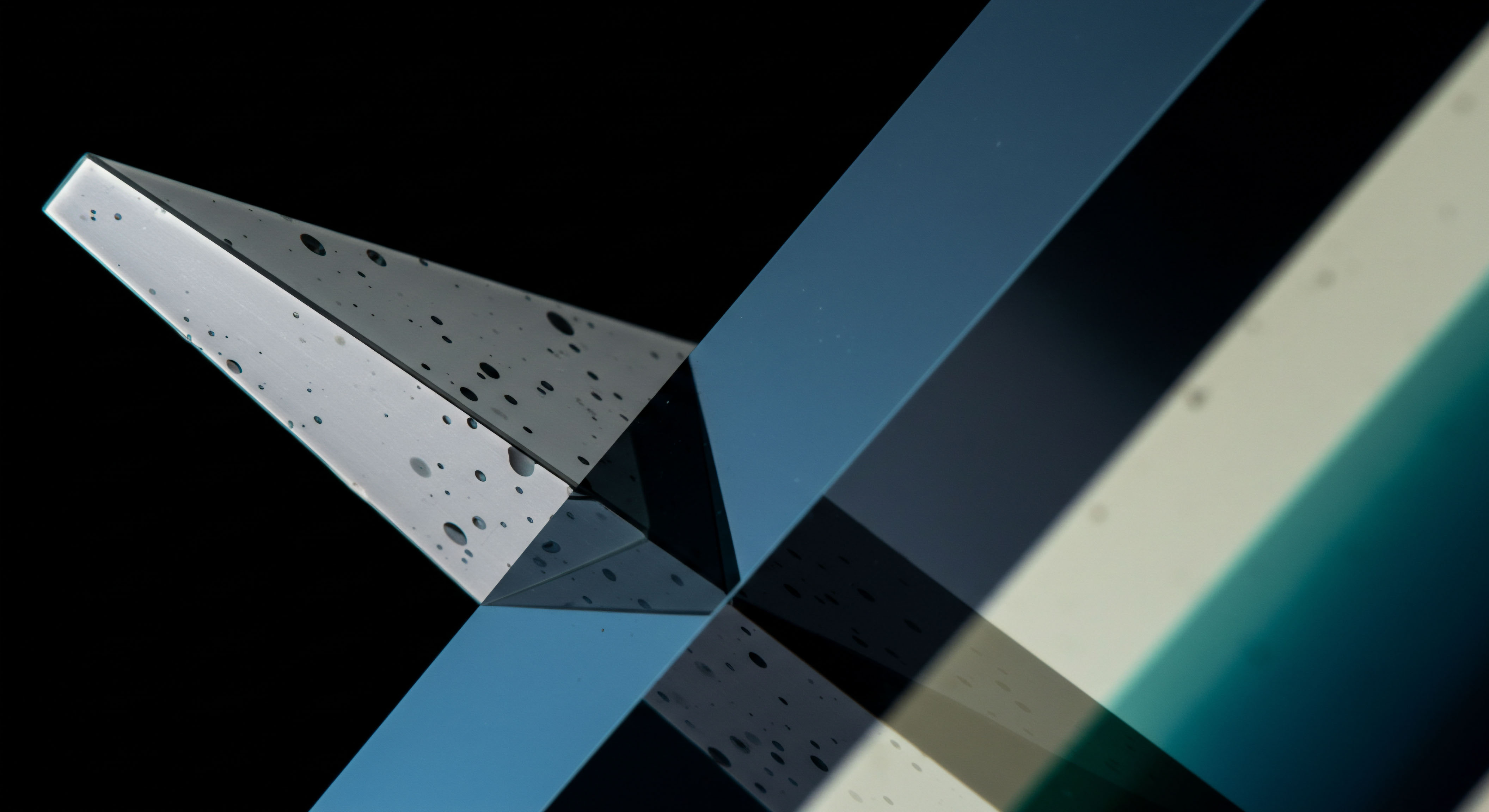

Hardware acceleration provides a direct solution to this physical problem by offloading specific, computationally intensive tasks from the CPU to specialized silicon designed for a single purpose. Field-Programmable Gate Arrays (FPGAs) and specialized Network Interface Cards (NICs) are the primary tools for this purpose. An FPGA is a configurable integrated circuit that can be programmed to perform a specific set of logical operations. By implementing tasks like network protocol parsing, order book management, and pre-trade risk checks directly in hardware, the processing pipeline becomes a deterministic, straight-line path for data.

This removes the unpredictability of a software-based system and reduces latency by orders of magnitude, moving from microseconds to nanoseconds. The core function of hardware acceleration in this context is to bring the trading logic as close to the network wire as physically possible, minimizing the distance and the number of processing steps data must travel.

Hardware acceleration addresses the physical limitations of software by moving critical data processing tasks directly into specialized silicon, achieving deterministic low-latency performance.

Deterministic Latency and Its Systemic Importance

The concept of determinism is central to understanding the role of hardware acceleration. While CPUs are exceptionally powerful and flexible, their performance on any given task can fluctuate based on their current workload, creating “jitter” or unpredictable variations in processing time. In quote dissemination, where the value of information decays in nanoseconds, such unpredictability is a critical failure point. A market maker’s ability to provide consistent liquidity depends on their capacity to update quotes at a predictable speed in response to market movements.

Hardware acceleration, particularly with FPGAs, provides this deterministic latency. Because the logic is etched into the chip’s circuitry, an FPGA performs the same operation in the same amount of time, every single time. This consistency allows a trading firm to build systems with a known, reliable response time, which is a foundational requirement for sophisticated, automated trading strategies.

This deterministic performance has a systemic impact beyond a single firm. For an exchange, ensuring that all market makers can disseminate quotes with minimal and predictable latency contributes to a tighter, more liquid market. It enhances the quality of price discovery and reduces the arbitrage opportunities that arise from technology-induced delays.

For the market maker, it is the primary tool for managing adverse selection risk ▴ the risk of having a stale quote taken by a faster participant who has already seen a price change. By ensuring the fastest possible reaction time, hardware acceleration allows firms to maintain their presence in the market with tighter spreads and greater confidence, ultimately contributing to a more efficient and stable market ecosystem.

Strategy

Selecting the Optimal Acceleration Substrate

The strategic decision to implement hardware acceleration involves a critical analysis of different technological substrates, each offering a unique balance of performance, flexibility, and development overhead. The choice is a trade-off between raw speed, the ability to adapt to changing market conditions, and the total cost of ownership. A firm’s selection defines its competitive posture and its capacity for future innovation.

The primary options form a spectrum of performance and adaptability. General-purpose CPUs represent the baseline, offering maximum flexibility through software but suffering from the highest and most unpredictable latency. Application-Specific Integrated Circuits (ASICs) occupy the opposite end, providing the absolute lowest latency by designing a chip for a single, immutable algorithm. FPGAs offer a compelling middle ground, delivering performance that approaches that of ASICs while retaining the ability to be reprogrammed and updated, making them a strategically sound choice for navigating evolving market structures and protocols.

Comparative Framework for Acceleration Technologies

A disciplined evaluation of these technologies is essential. The following table provides a framework for comparing the primary hardware acceleration options against key strategic metrics. This analysis guides the decision-making process by quantifying the trade-offs inherent in each choice.

| Metric | CPU (Software) | GPU (Parallel Processing) | FPGA (Programmable Hardware) | ASIC (Custom Silicon) |

|---|---|---|---|---|

| Typical Latency | Microseconds (µs) | Tens of Microseconds (µs) | Nanoseconds (ns) | Sub-Nanoseconds (ns) |

| Determinism | Low (High Jitter) | Moderate | High (Deterministic) | Extremely High |

| Flexibility/Re-programmability | Very High | High | High | None |

| Development Complexity | Low | Moderate | High | Very High |

| Time to Market | Fast | Moderate | Slow | Very Slow |

| Power Consumption | Moderate | High | Low | Very Low |

The strategic selection of a hardware acceleration technology hinges on a disciplined trade-off between raw latency, developmental agility, and long-term adaptability.

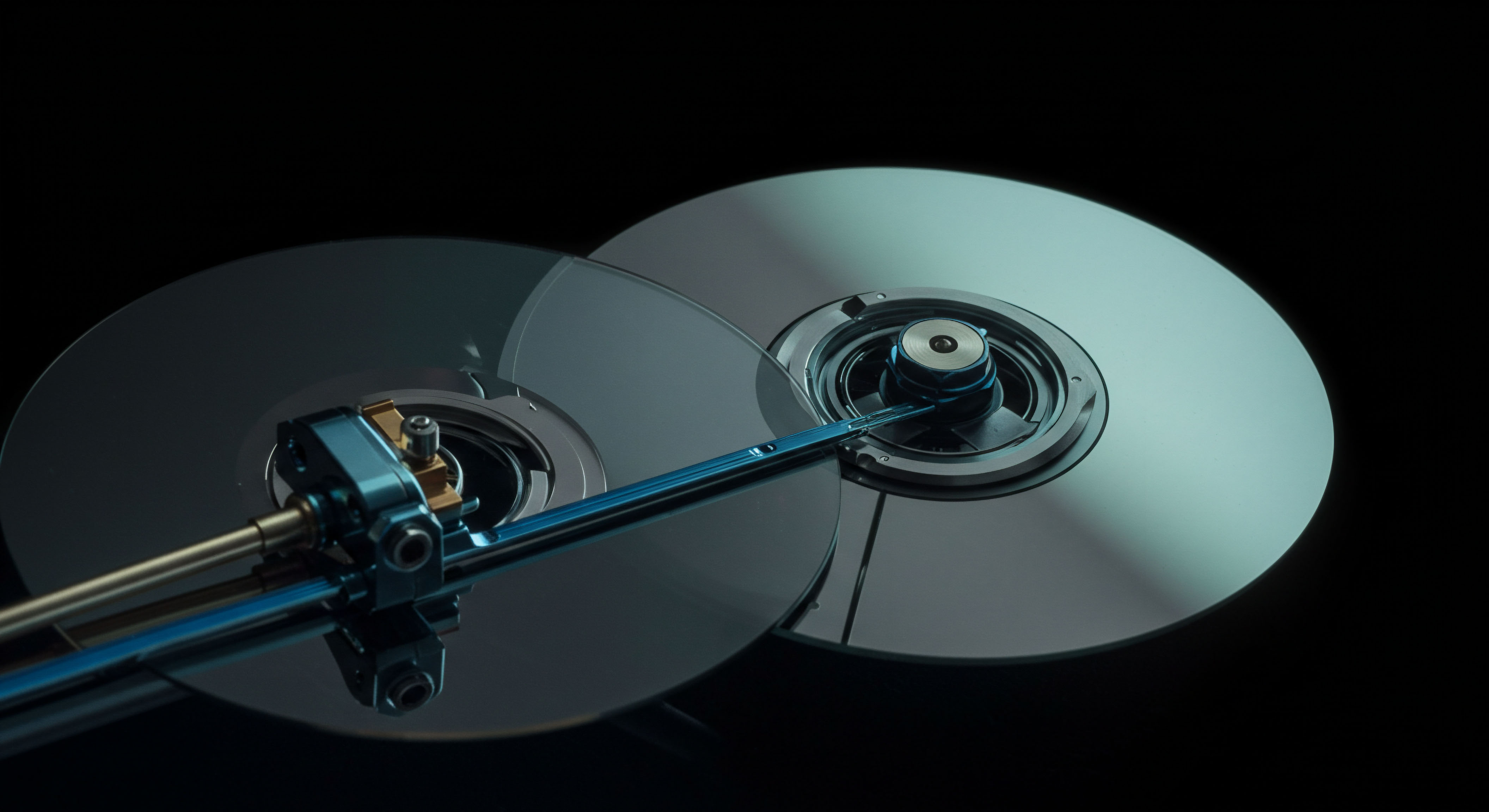

System-Level Integration and Kernel Bypass

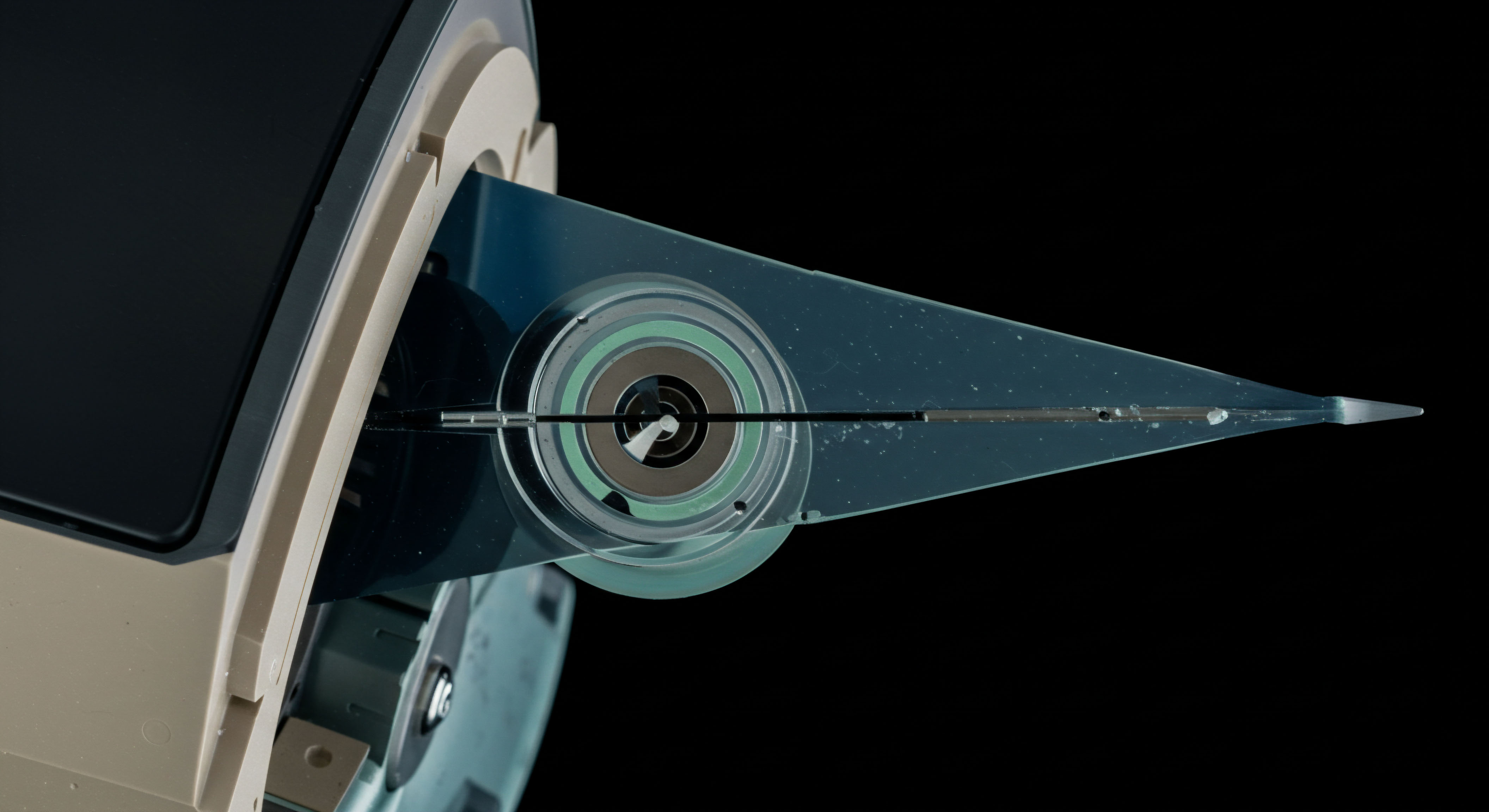

Achieving optimal throughput requires more than just specialized hardware; it demands a holistic system design that removes bottlenecks at every layer of the technology stack. A critical strategy in this endeavor is the implementation of kernel bypass networking. In a standard operating system, all network traffic is processed by the kernel, a layer of software that manages the system’s resources. This process, while robust, introduces significant latency as data is copied between the kernel’s memory space and the application’s memory space.

Kernel bypass techniques allow an application to interact directly with the network hardware, completely avoiding the operating system’s network stack. This is a foundational strategy for any serious low-latency system. Technologies that enable this include:

- OpenOnload ▴ A user-space network stack that intercepts network calls from an application and redirects them to a path that bypasses the kernel, accelerating standard socket-based applications with minimal code changes.

- Data Plane Development Kit (DPDK) ▴ A set of libraries and drivers that allows for fast packet processing in user space by enabling direct access to the Network Interface Card (NIC).

- TCP Offload Engine (TOE) ▴ A capability built into specialized NICs that handles the entire TCP/IP stack in hardware, freeing the host CPU from network processing tasks.

By combining a hardware acceleration platform like an FPGA with kernel bypass networking, a firm creates a direct, unimpeded data path from the network wire to its trading logic and back. This integrated approach ensures that the latency benefits gained from the FPGA are preserved across the entire system, resulting in a truly optimized infrastructure for quote dissemination.

Execution

The High-Throughput Quote Dissemination Pipeline

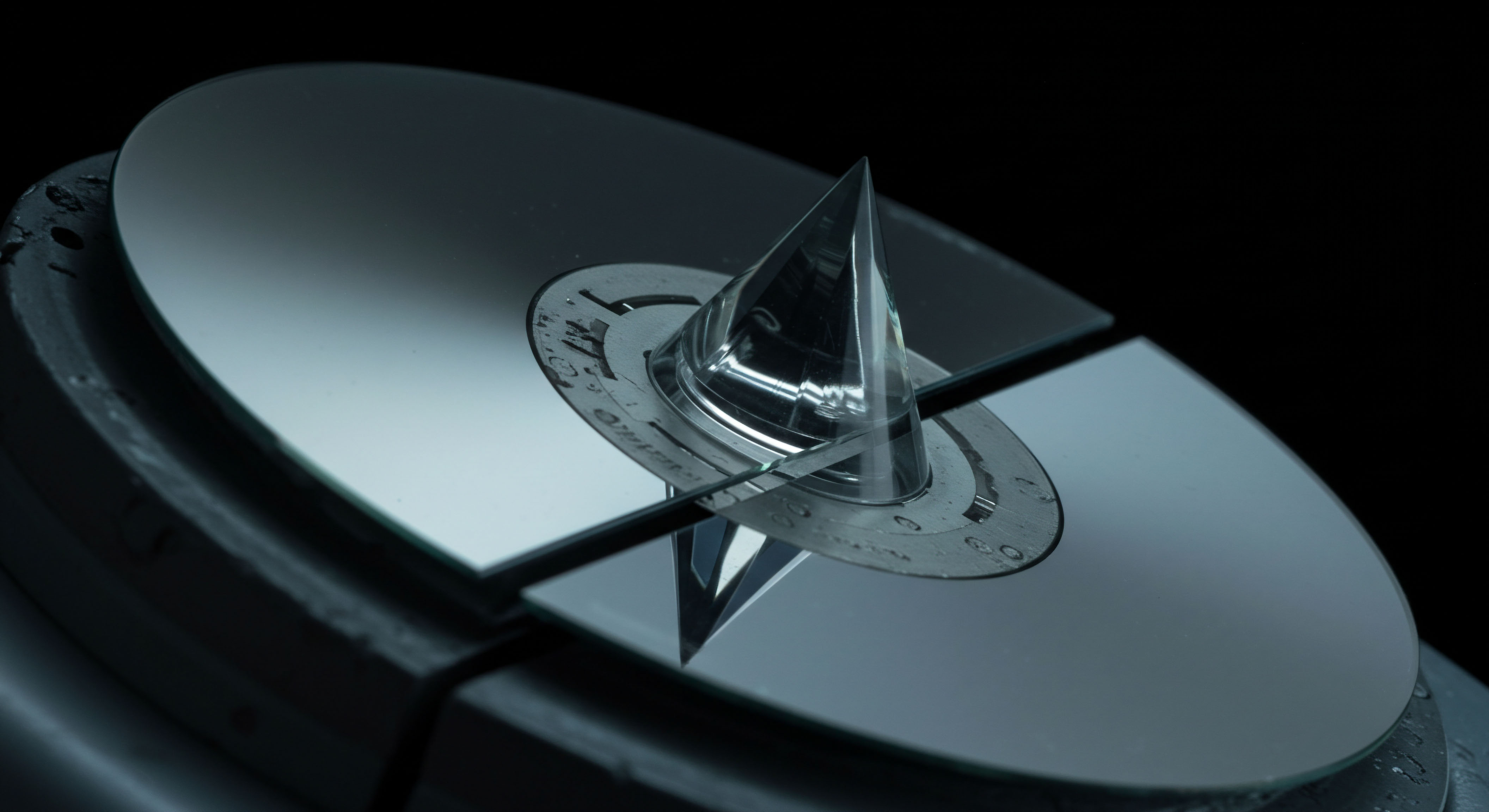

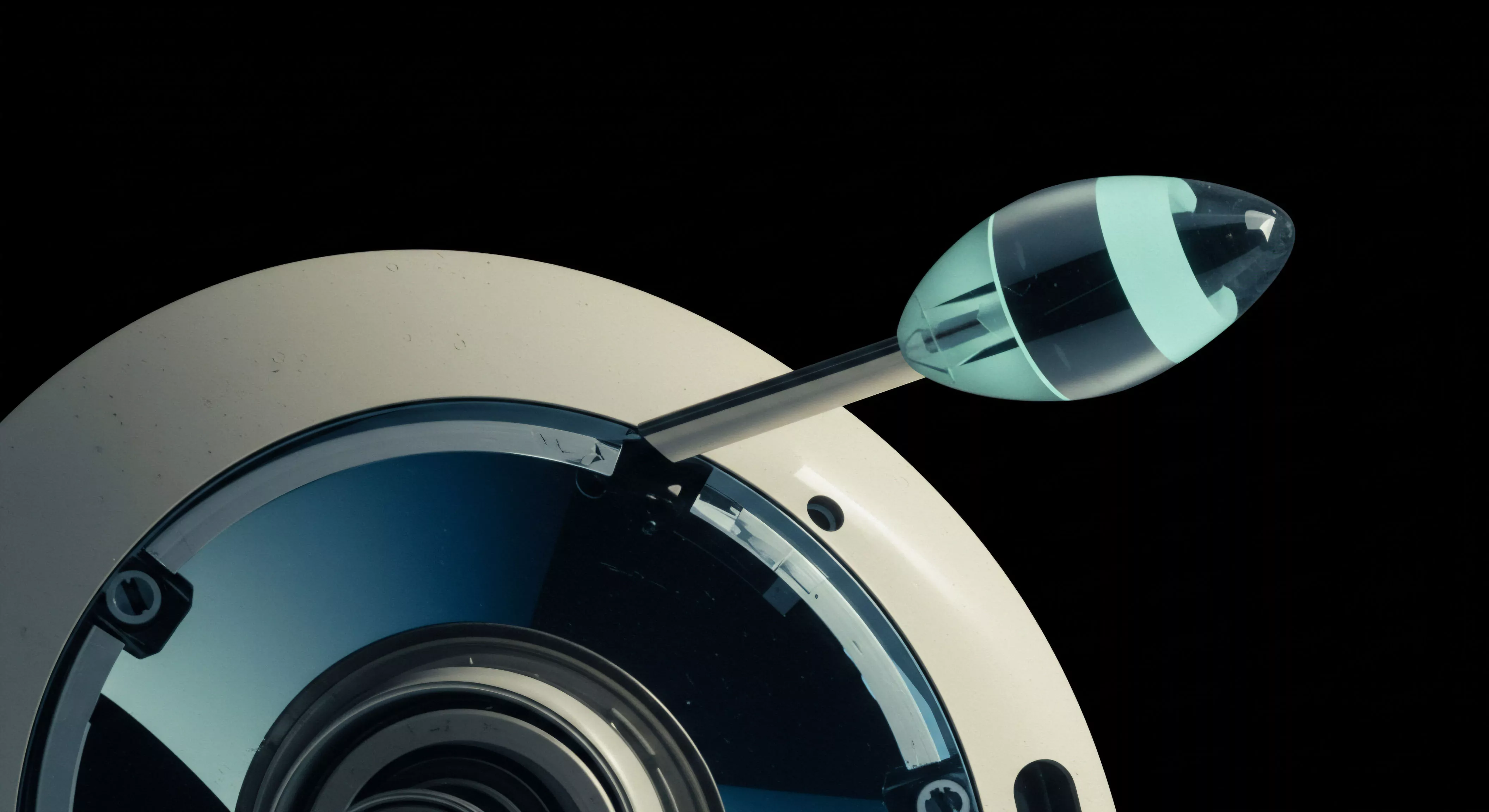

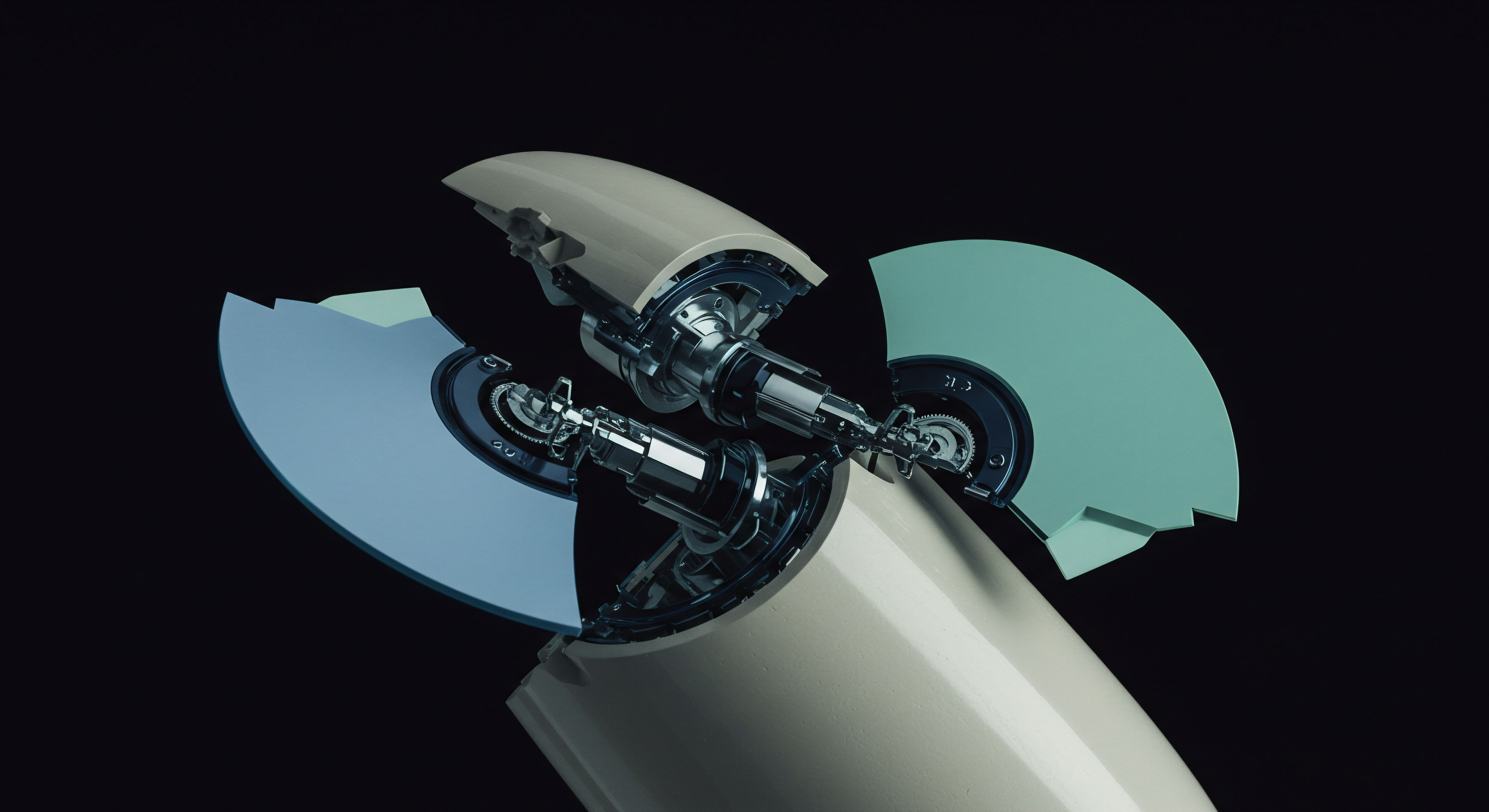

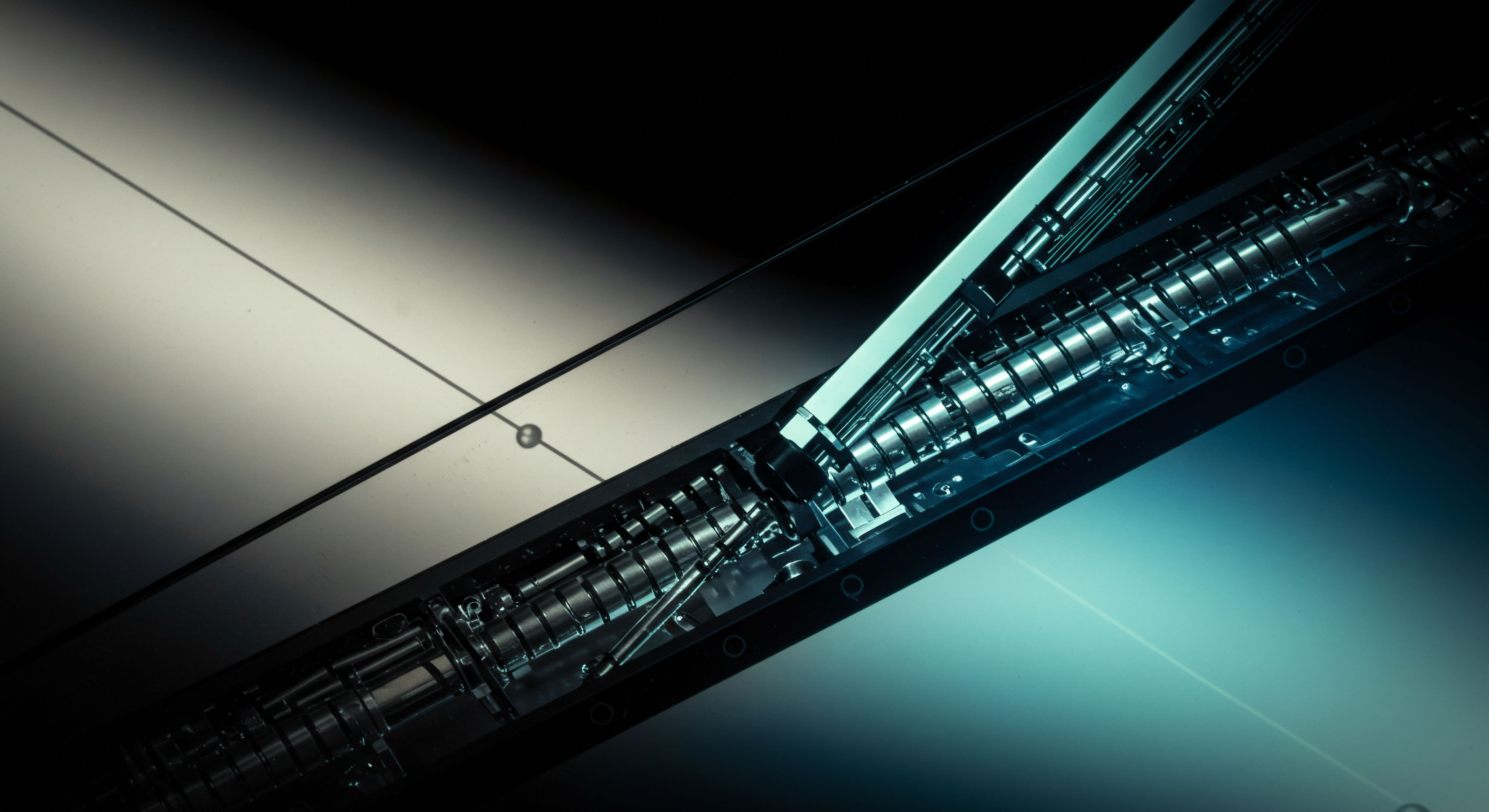

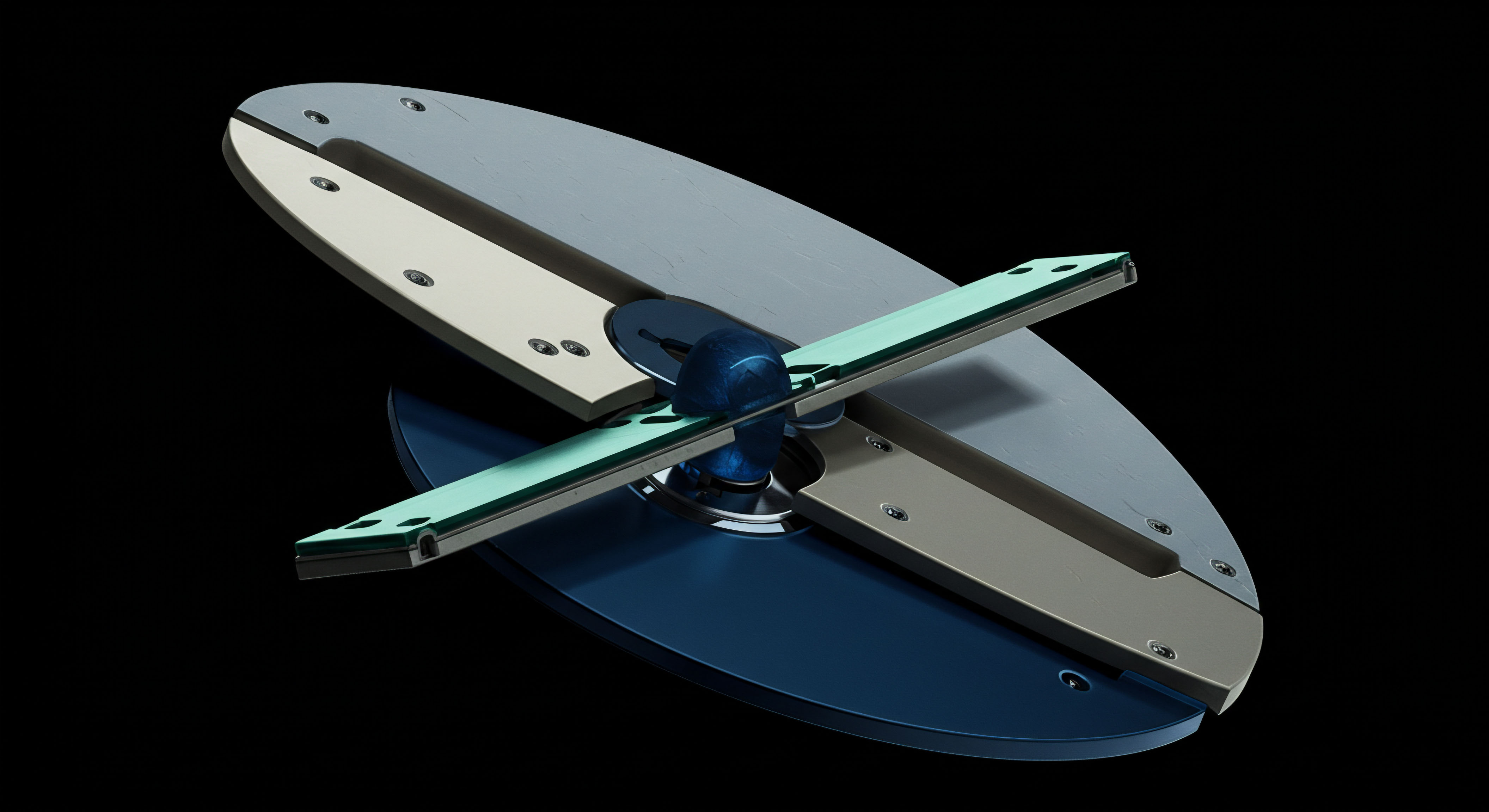

The execution of a hardware-accelerated quote dissemination system is a precisely engineered pipeline, where each stage is optimized for minimal latency and deterministic performance. This pipeline represents the physical and logical path that market data travels from the moment it enters the firm’s infrastructure to the moment a responsive quote is sent back to the market. The objective is to process this data entirely within the hardware layer, engaging the CPU only for high-level strategy management and monitoring.

The process begins at a specialized NIC, often one with an onboard FPGA. The entire tick-to-trade cycle is executed on this single piece of hardware. The key stages of this pipeline are designed to run in parallel wherever possible, a core advantage of the FPGA architecture.

This contrasts with a CPU’s sequential instruction processing. The operational flow is a model of efficiency, designed to eliminate every possible source of delay.

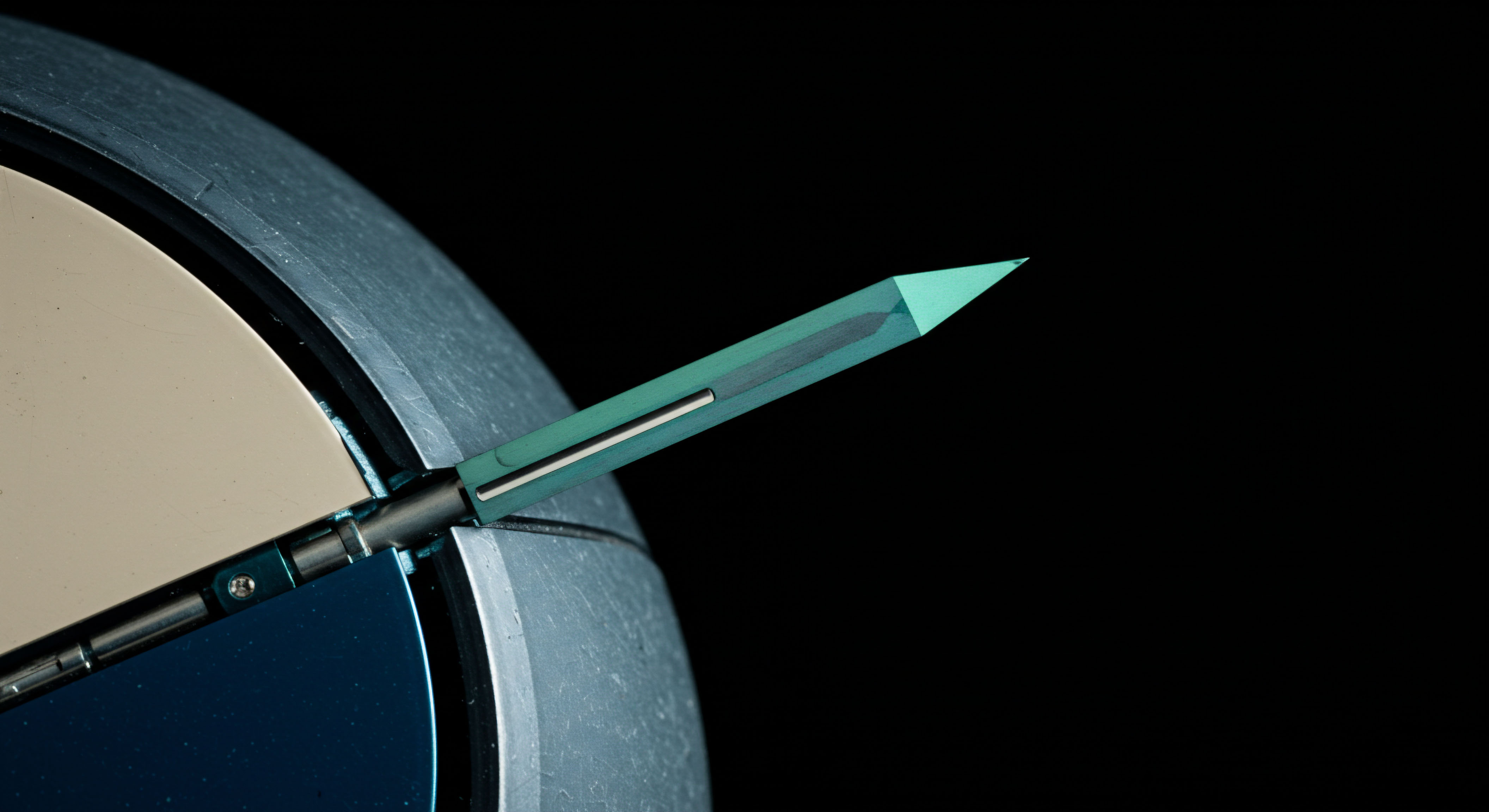

- Packet Ingestion and Decoding ▴ The FPGA directly ingests raw network packets from the exchange. The hardware contains dedicated logic to parse the network protocols (like Ethernet, IP, and UDP) and the exchange’s specific market data format (like FIX/FAST) at line rate. This happens without ever storing the full packet in memory, reducing latency significantly.

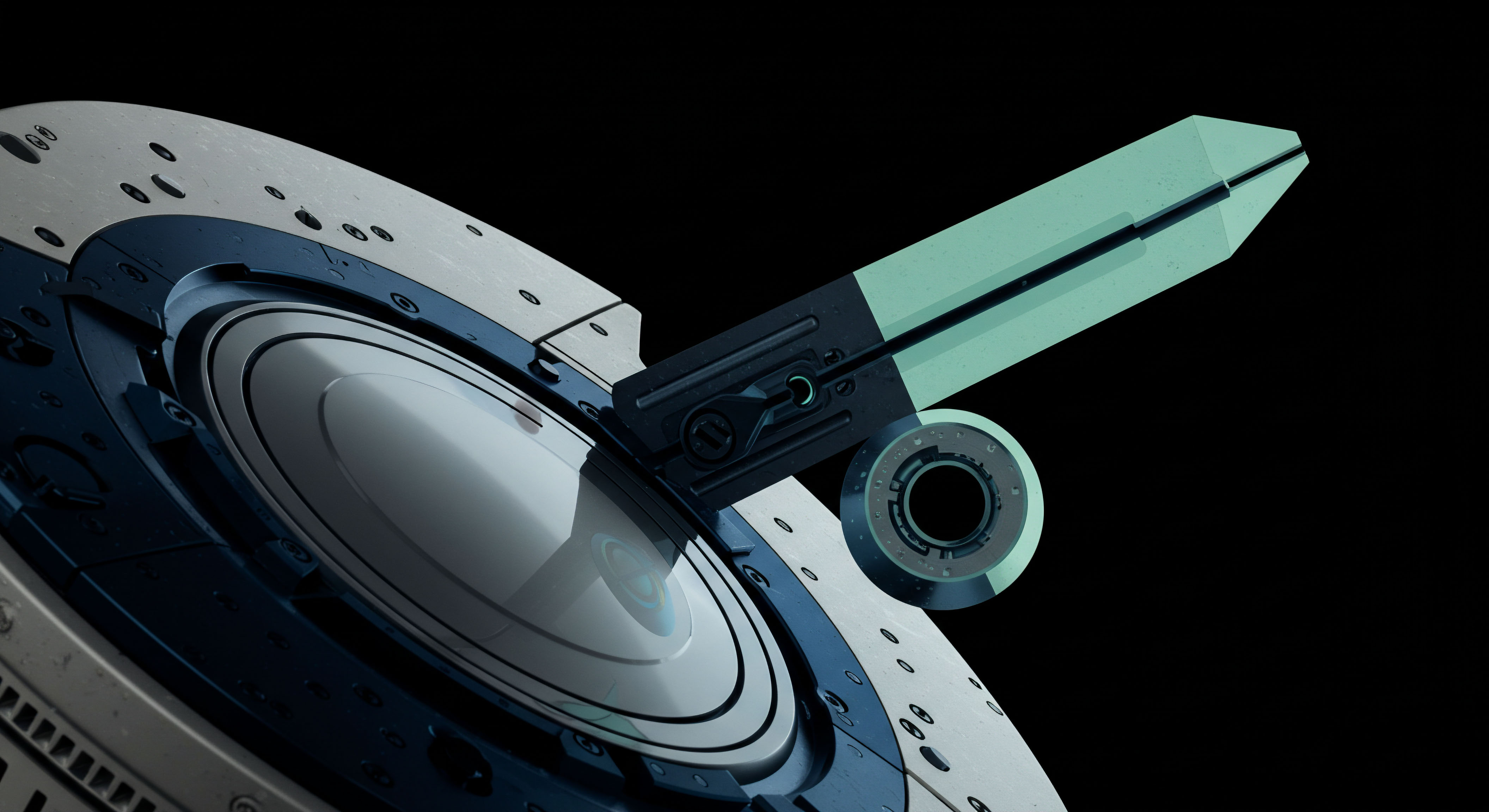

- Order Book Construction ▴ As market data messages are decoded, a dedicated engine within the FPGA updates an in-hardware representation of the order book. Using the FPGA’s fast on-chip memory allows for instantaneous updates, avoiding the delays associated with accessing a CPU’s memory cache.

- Trading Logic Execution ▴ The firm’s quoting algorithm is compiled into digital circuits on the FPGA. This logic continuously monitors the state of the hardware order book and, upon detecting a relevant change, instantly triggers the quoting process.

- Pre-Trade Risk and Compliance Checks ▴ Before a new quote can be generated, it must pass a series of risk checks (e.g. fat-finger checks, position limits, collateral verification). Implementing these checks in hardware ensures they are completed in a few nanoseconds, a process that would take microseconds in software.

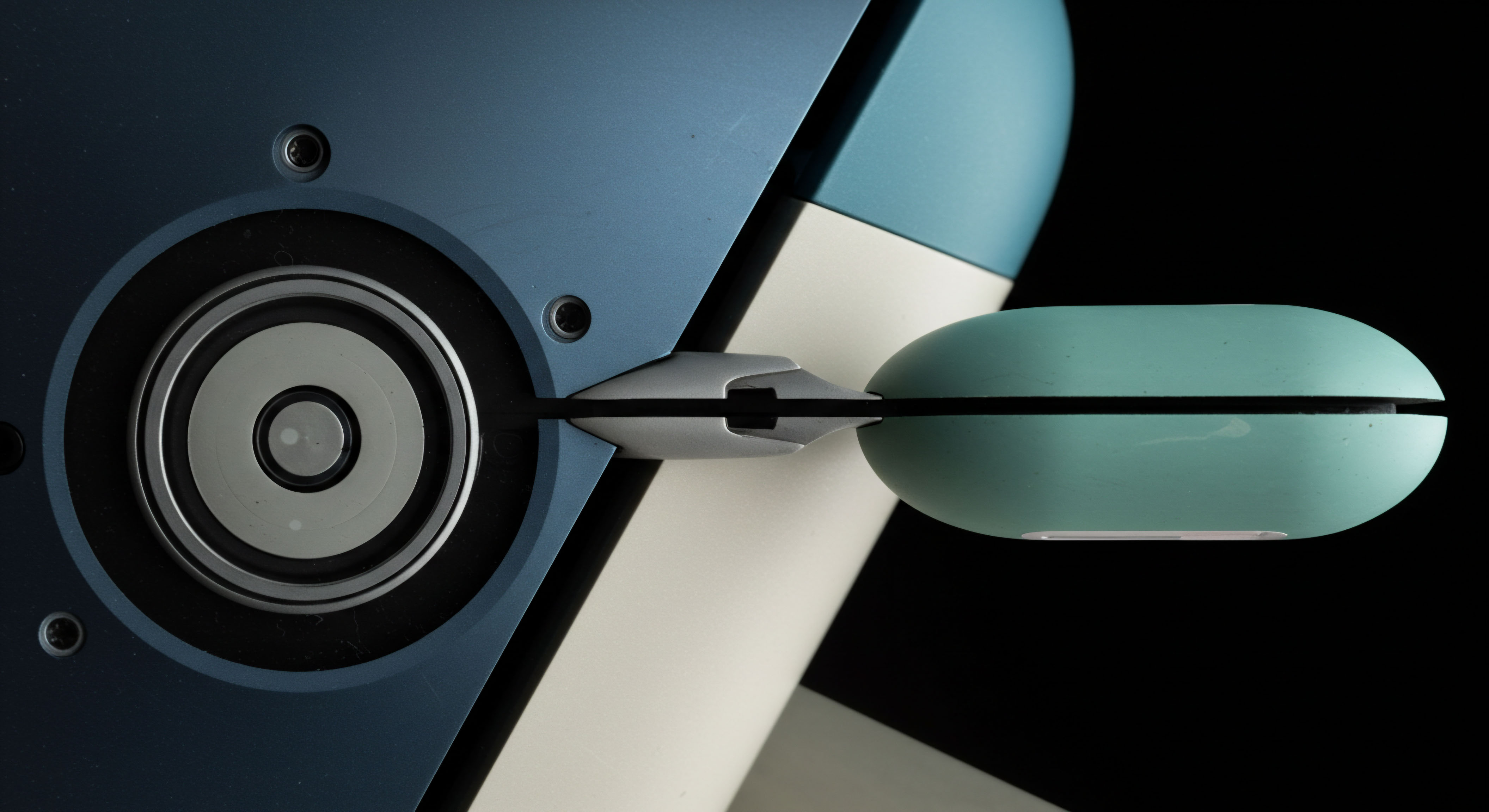

- Quote Generation and Transmission ▴ Once all checks are passed, the FPGA constructs the new quote packet and transmits it directly from the NIC’s network port. The entire process bypasses the server’s main operating system and CPU, providing the lowest possible round-trip latency.

Quantitative Analysis of Latency Reduction

The performance differential between a software-based and a hardware-accelerated system is not incremental; it is a step-function improvement measured in orders of magnitude. The following table provides a granular, quantitative breakdown of the latency contributions at each stage of the quote dissemination pipeline, illustrating the profound impact of offloading processing to an FPGA.

| Processing Stage | Software-Based System (CPU) Latency (ns) | Hardware-Accelerated System (FPGA) Latency (ns) | Magnitude of Improvement |

|---|---|---|---|

| Network Packet Ingress (NIC to App) | 3,000 – 5,000 | 50 – 100 (Kernel Bypass) | ~50x |

| Market Data Protocol Decoding | 1,500 – 2,500 | 20 – 40 | ~60x |

| Order Book Update | 500 – 1,000 | 5 – 10 | ~100x |

| Trading Logic Decision | 2,000 – 4,000 | 10 – 30 | ~130x |

| Pre-Trade Risk Checks | 2,500 – 5,000 | 15 – 25 | ~200x |

| Order Packet Formulation & Egress | 1,000 – 2,000 | 10 – 20 | ~100x |

| Total Tick-to-Trade Latency | 10,500 – 19,500 (10.5 – 19.5 µs) | 110 – 225 (0.11 – 0.23 µs) | ~90x |

Executing the quote dissemination pipeline in hardware reduces end-to-end latency from the microsecond domain to the nanosecond domain, a fundamental competitive transformation.

This quantitative data underscores the operational necessity of hardware acceleration. A software-based system, even a highly optimized one, is fundamentally constrained by the architectural overhead of general-purpose computing. The aggregate latency of a software stack places a firm at a structural disadvantage.

In contrast, the hardware-accelerated system operates at a speed that is bounded only by the speed of light and the gate delays within the silicon itself. This provides a durable and defensible competitive edge in markets where speed is the primary determinant of execution quality and profitability.

References

- Pan, Z. & Gao, Y. (2018). Design of a Low-Latency FPGA-Based High-Frequency Trading System. Journal of Signal Processing Systems, 90(4), 561 ▴ 573.

- Lockwood, J. W. et al. (2015). A Low-Latency, High-Throughput, and Scalable FPGA-Based Network System for Financial Trading. IEEE Transactions on Parallel and Distributed Systems, 26(11), 3053 ▴ 3065.

- Thomas, D. B. & Luk, W. (2009). The CASA FPGA-Based Financial Computing Platform. In 2009 International Conference on Field-Programmable Logic and Applications (pp. 639-642). IEEE.

- Hutchings, B. L. & Franklin, M. (2004). High-Speed Network Intrusion Detection on FPGAs. In Field-Programmable Custom Computing Machines, 2004. FCCM 2004. 12th Annual IEEE Symposium on (pp. 294-295). IEEE.

- Glaser, J. & Kulkarni, C. (2016). FPGA-Based Acceleration for Financial Applications. Intel White Paper.

- Van der Valk, R. & van der Vleuten, R. J. (2012). Low-latency network interface with kernel bypass for high-frequency trading. In 2012 NORCHIP (pp. 1-6). IEEE.

- Bellows, J. & Morris, R. (2011). The Case for Hardware-Based TCP/IP Offload in High-Frequency Trading. ACM SIGOPS Operating Systems Review, 45(2), 54-61.

- Cong, J. & Wei, X. (2014). A Decade of FPGAs in the Datacenter. IEEE Micro, 34(5), 67-75.

Reflection

The System as the Strategic Asset

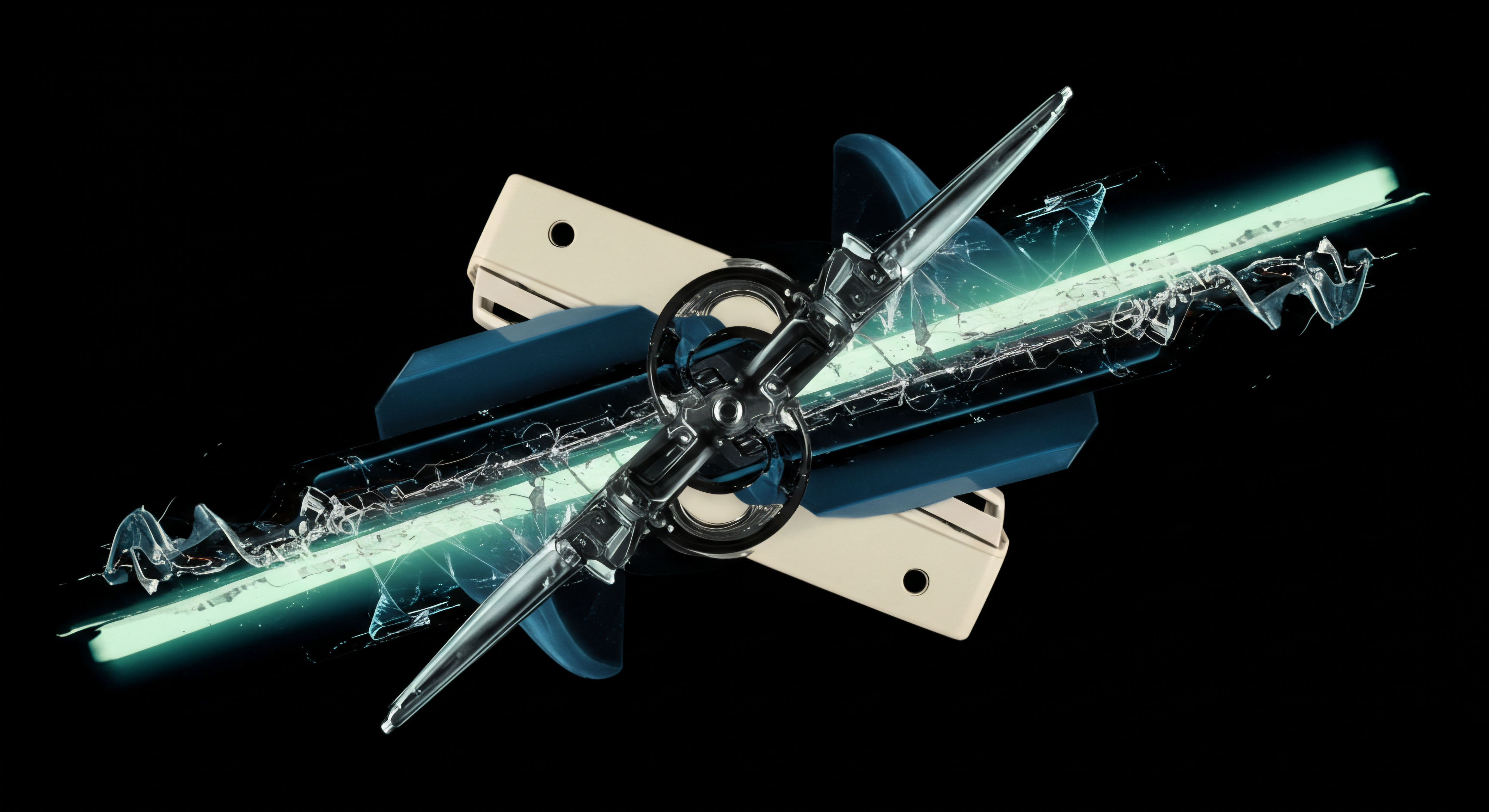

The integration of hardware acceleration into a quote dissemination framework transforms the conversation from one of simple speed to one of systemic integrity. The knowledge gained here is a component of a much larger operational intelligence system. The true strategic asset is the holistic architecture ▴ the seamless integration of hardware, software, and market structure knowledge.

The ultimate objective is the creation of a system that functions as a precise and deterministic extension of the firm’s trading strategy. The potential lies not in owning a faster component, but in commanding a superior, more coherent operational framework that anticipates and responds to market dynamics with unwavering consistency.

Glossary

Quote Dissemination

Tick-To-Trade

Hardware Acceleration

Order Book Management

Deterministic Latency

Fpga

Kernel Bypass

Network Interface Card

Tcp Offload Engine

Market Data