Concept

The Physicality of Speed

The imperative to optimize firm quote reporting is not born from a desire for abstract efficiency, but from the concrete physical limitations of market participation. At the highest levels of institutional trading, the primary constraint is the speed of light ▴ the immutable rate at which information can travel. When a market event occurs, the race to react is measured in nanoseconds, and success is determined by the physical proximity to the exchange’s matching engine and the absolute minimization of processing delay. This is the operational reality.

The challenge, therefore, becomes one of engineering a system that introduces the least possible delay between market data receipt and quote dissemination. In this environment, the processing of information within the firm’s own infrastructure emerges as the most significant and controllable variable.

A firm quote is a binding commitment to trade at a displayed price and size. Regulatory frameworks mandate that market makers honor these quotes, making the accuracy and timeliness of their dissemination a matter of compliance and risk management. Any latency in updating a quote in response to a market shift exposes the firm to adverse selection, where other, faster participants can trade on stale prices for a risk-free profit.

The efficiency of the reporting mechanism is thus directly tied to the firm’s profitability and market stability. A system that cannot process market data, apply trading logic, and broadcast an updated quote with deterministic, ultra-low latency is fundamentally uncompetitive.

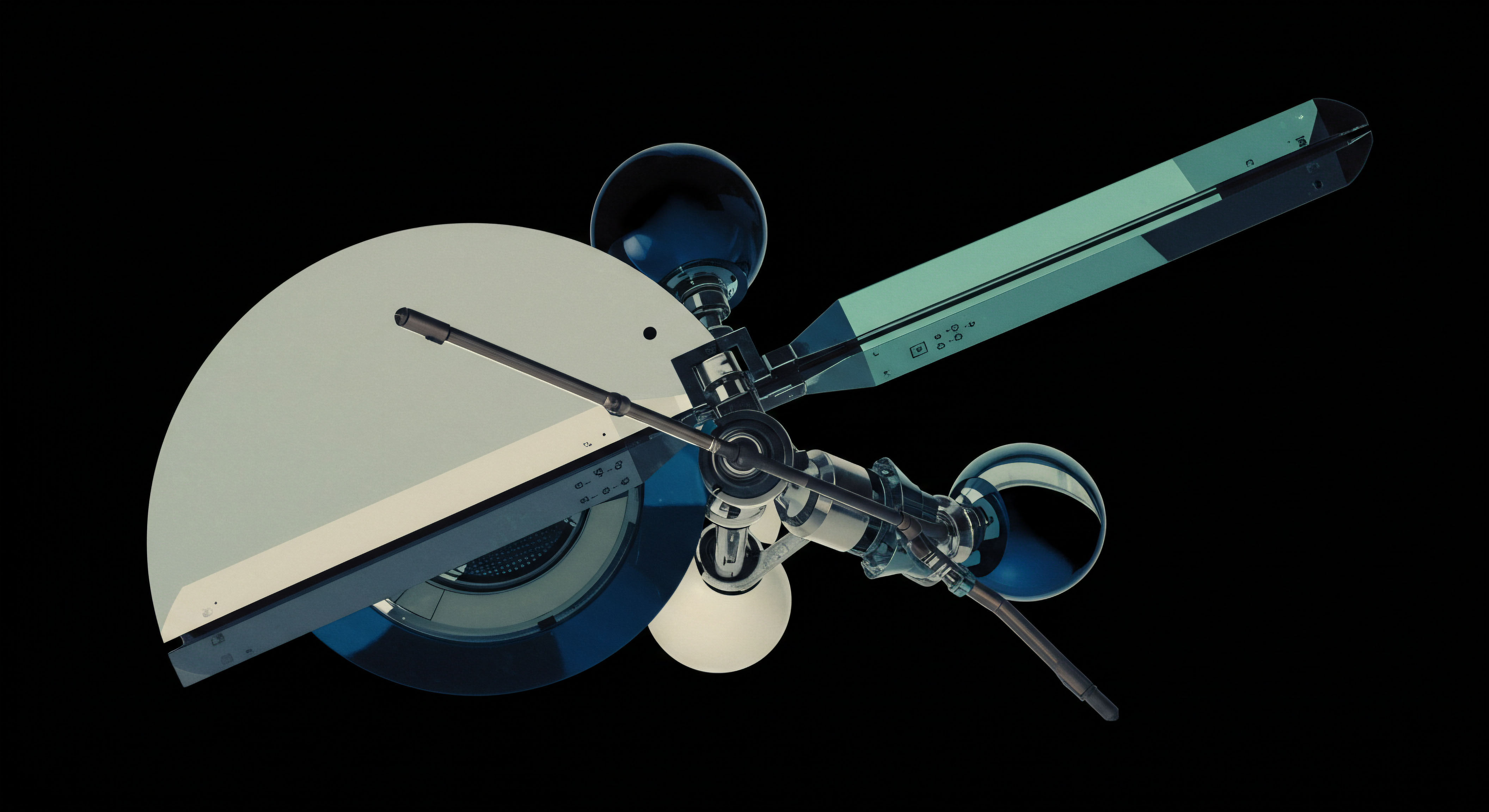

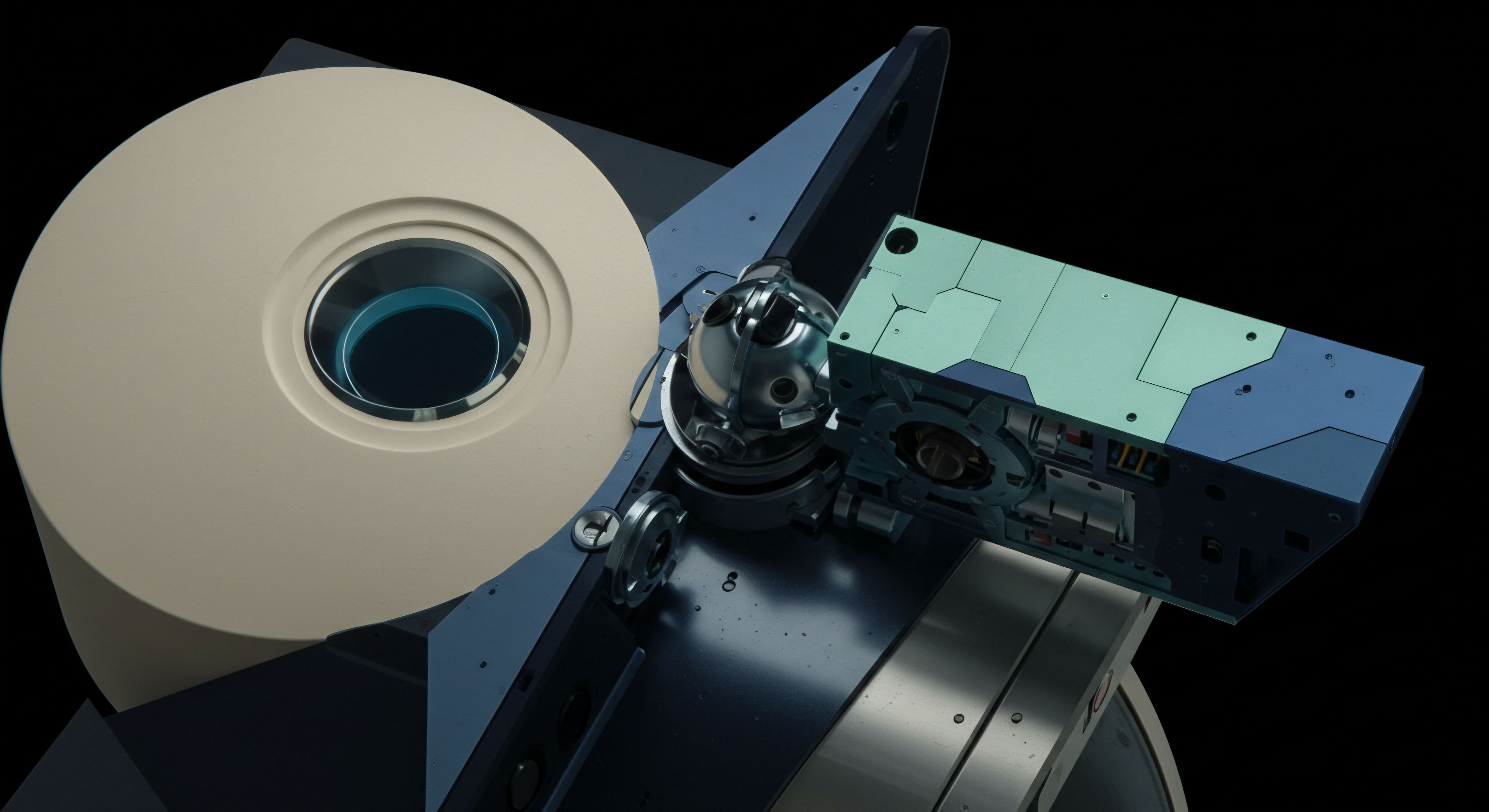

Hardware acceleration addresses the physical limits of trading by moving critical processes from the variable latency of software to the deterministic speed of silicon.

From Software to Silicon

Conventional quote reporting systems rely on software running on general-purpose central processing units (CPUs). While flexible, CPUs are designed for versatility, not singular speed. They operate through a series of abstractions ▴ operating systems, network stacks, and application layers ▴ each introducing unpredictable delays, or “jitter.” For quote reporting, where determinism is paramount, this variability is a critical flaw.

A task as fundamental as parsing an incoming market data message can be interrupted by an operating system process, delaying a critical quote update by microseconds ▴ an eternity in modern markets. This inherent non-determinism of software-based systems creates an unacceptable level of operational risk.

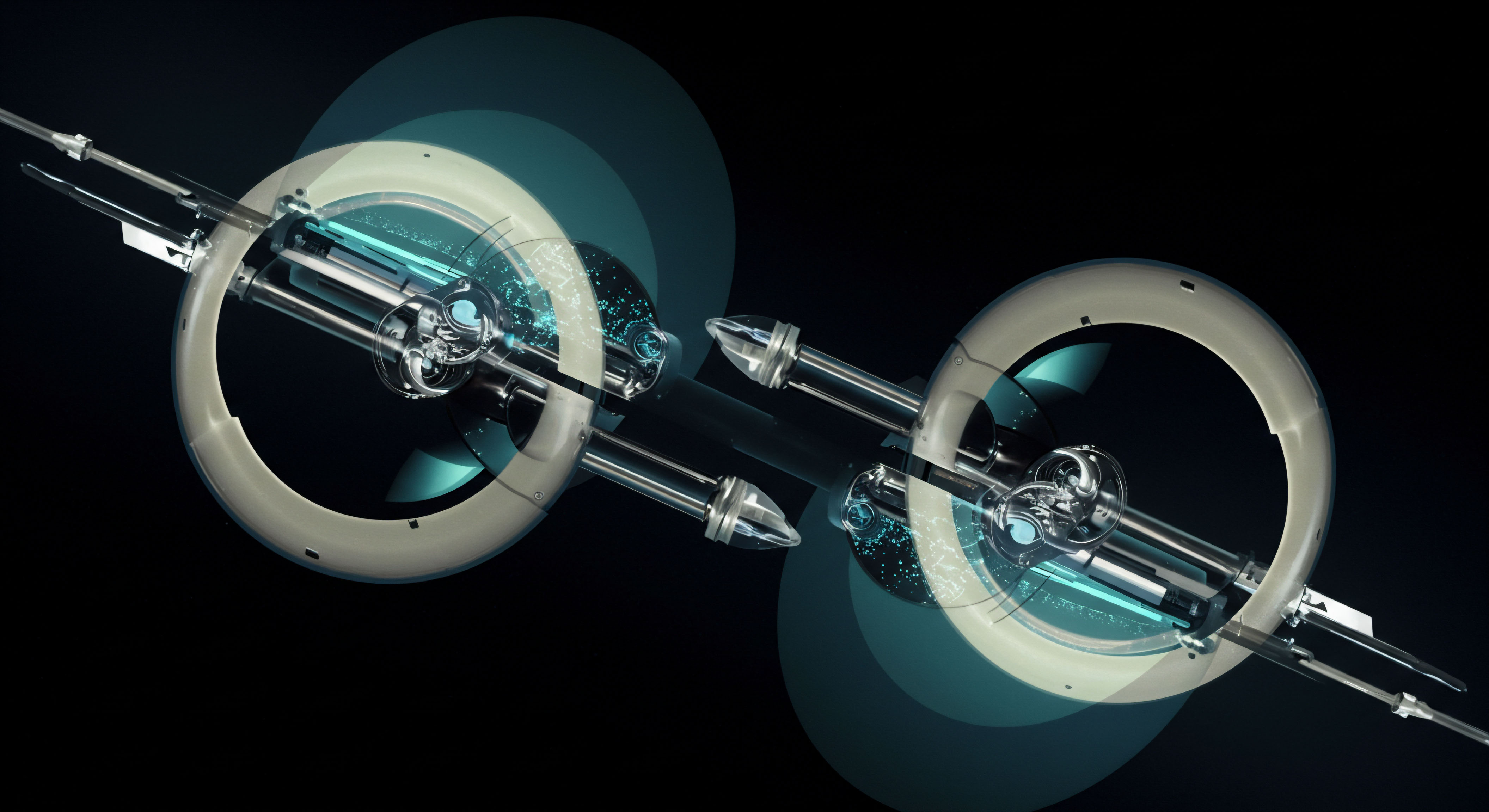

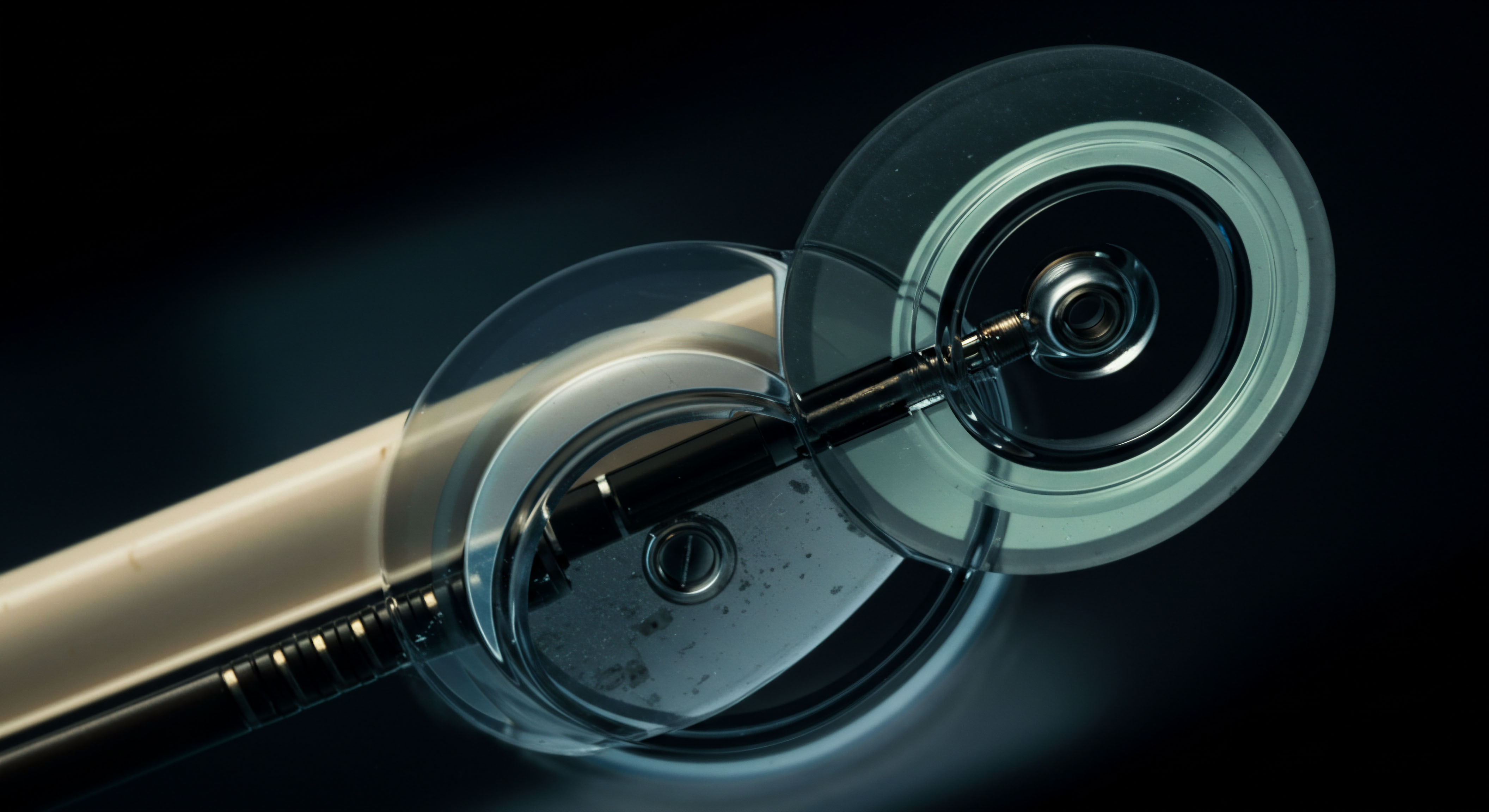

Hardware acceleration confronts this challenge by offloading specific, latency-sensitive tasks from the CPU directly onto specialized hardware, most notably Field-Programmable Gate Arrays (FPGAs). An FPGA is a semiconductor device containing a matrix of configurable logic blocks connected through programmable interconnects. Unlike a CPU that must fetch and execute instructions sequentially, an FPGA can be programmed to perform a specific task in parallel, with the logic etched directly into the hardware pathways. This means that processes like parsing financial protocols (e.g.

FIX), filtering market data, and even executing rudimentary trading logic occur at the speed of the hardware circuit, eliminating software-induced jitter entirely. The result is a system that operates with predictable, nanosecond-level latency, transforming quote reporting from a probabilistic software task into a deterministic hardware function.

Strategy

The Strategic Imperative of Determinism

The strategic decision to implement hardware acceleration is driven by the pursuit of determinism over mere speed. While raw latency reduction is a significant benefit, the primary advantage lies in achieving a predictable and repeatable processing time for every single quote message. In a software-based environment, the time to process a message can vary based on system load, kernel interruptions, and other factors, creating a statistical distribution of latencies. For a market maker, this “jitter” is a profound source of risk.

A delayed quote update can be the difference between capturing a profitable spread and suffering a loss from being adversely selected. Hardware acceleration collapses this distribution, ensuring that every message is processed within a tight, predictable nanosecond window.

This deterministic performance underpins several core trading strategies. For latency arbitrage, it ensures that a firm can consistently identify and act on price discrepancies between venues before they disappear. For market making, it allows for tighter bid-ask spreads, as the risk premium associated with quoting uncertainty is dramatically reduced.

The firm can confidently display liquidity knowing its ability to update quotes in response to market movements is guaranteed at the hardware level. This consistency transforms the firm’s technological stack into a reliable component of its overall risk management framework.

Adopting hardware acceleration is a strategic shift from managing latency as a variable risk to engineering it as a constant, predictable asset.

Comparative System Architectures

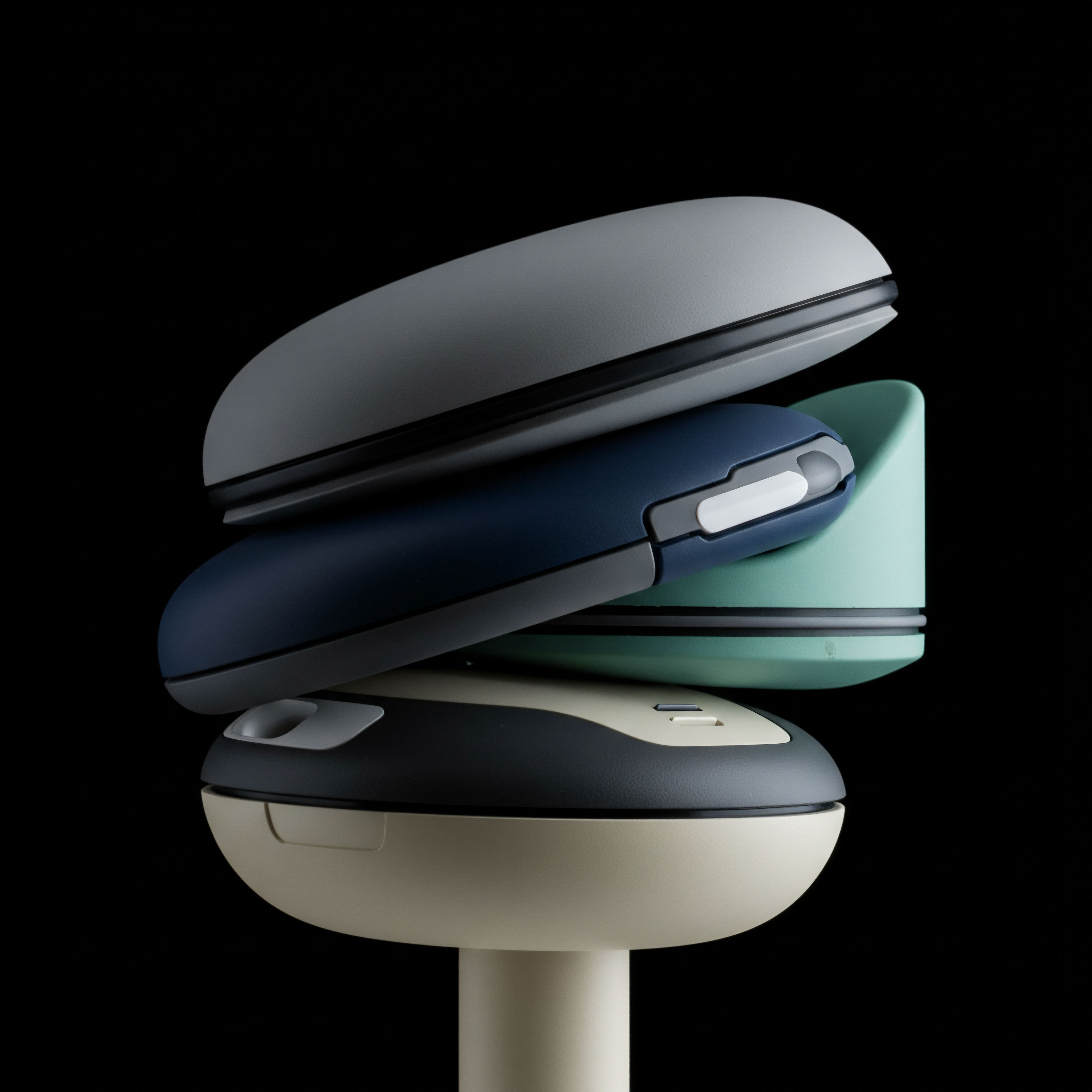

An institution evaluating the integration of hardware acceleration must analyze the trade-offs between a purely software-based system and a hybrid, hardware-accelerated model. The selection is a function of the firm’s specific trading strategies, risk tolerance, and capital investment priorities. A CPU-based approach offers flexibility and lower initial development costs, whereas an FPGA-centric model prioritizes performance and predictability at the expense of complexity and specialization.

The following table provides a comparative analysis of these two architectural philosophies, highlighting the key operational and strategic differences:

| Metric | CPU-Based System | FPGA-Accelerated System |

|---|---|---|

| Median Latency | Low Microseconds (e.g. 5-10 µs) | Low Nanoseconds (e.g. 200-800 ns) |

| Latency Jitter | High (Can vary by microseconds) | Extremely Low (Deterministic, single-digit nanosecond variance) |

| Throughput | Limited by core count and clock speed; susceptible to packet loss under high load. | Line-rate processing; can handle massive data volumes without degradation. |

| Development Cycle | Faster; leverages common programming languages (C++, Java). | Slower and more complex; requires specialized hardware description languages (VHDL, Verilog). |

| Flexibility | High; algorithms can be changed and redeployed quickly. | Lower; changes to logic require recompiling and redeploying the hardware image. |

| Operational Risk | Higher; unpredictable latency can lead to missed quotes and adverse selection. | Lower; deterministic performance allows for precise risk management. |

Core Offloading Strategies

The implementation of hardware acceleration is not an all-or-nothing proposition. Firms strategically choose which components of the trading pipeline to offload to hardware to achieve the greatest impact. The most common strategies include:

- Protocol Processing ▴ Offloading the parsing and serialization of complex financial protocols like FIX or exchange-specific binary formats. This is often the first and most impactful step, as it cleans and normalizes data before it ever reaches the CPU.

- Market Data Filtering ▴ Using the FPGA to filter out irrelevant market data (e.g. for instruments the firm does not trade) at line rate. This reduces the data volume that the CPU-based trading application needs to process, freeing up valuable cycles.

- Pre-Trade Risk Checks ▴ Implementing certain compliance and risk checks directly in hardware. Simple checks like fat-finger price collars or maximum order size can be executed on the FPGA with near-zero latency, providing a critical layer of safety.

- Full Logic Execution ▴ For the most latency-sensitive strategies, the entire trading algorithm is deployed on the FPGA. The hardware receives market data, makes a trading decision, and sends an order without any involvement from the host CPU. This represents the pinnacle of low-latency trading.

Execution

The Operational Playbook for Hardware Integration

The operational deployment of hardware acceleration for firm quote reporting is a systematic process that integrates specialized hardware into the existing trading infrastructure. This process requires a multidisciplinary team of network engineers, hardware developers, and quantitative strategists. The objective is to create a seamless data path where latency-critical functions are executed in silicon, while more complex, less time-sensitive logic remains in software. This hybrid approach optimizes performance while retaining necessary flexibility.

A successful integration follows a structured, multi-stage playbook:

- Trading Logic Segmentation ▴ The first step involves a granular analysis of the firm’s quoting strategy to identify which components are both latency-sensitive and suitable for hardware implementation. Functions that are simple, repetitive, and deterministic, such as market data parsing or basic price calculations, are prime candidates for offloading.

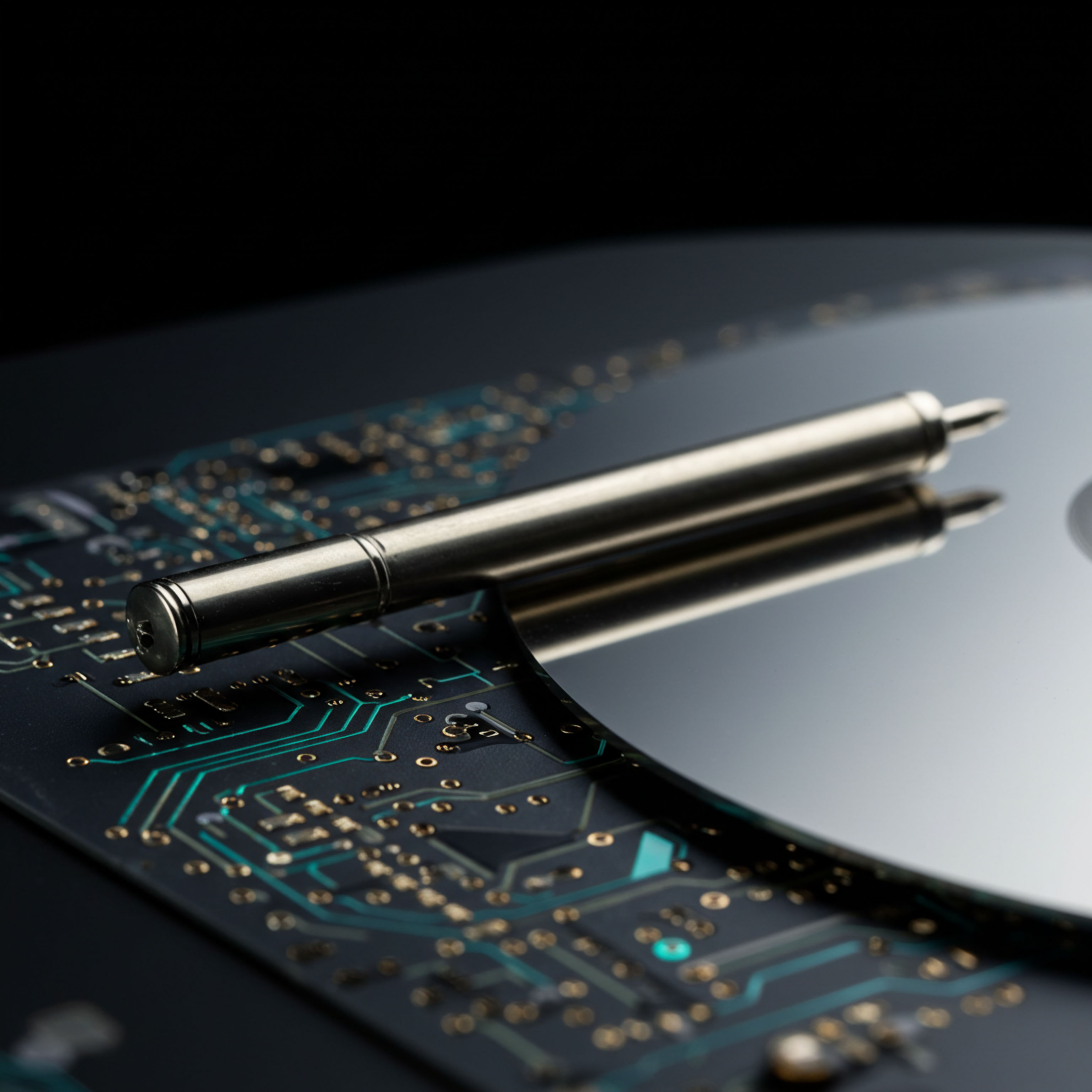

- Hardware and Vendor Selection ▴ The firm must select the appropriate FPGA-based network interface cards (Smart NICs) and development tools. This decision is based on factors like the required network port speeds (10/25/100GbE), the size and complexity of the FPGA chip, and the quality of the vendor’s software development kit and support.

- Hardware Description Language (HDL) Development ▴ Engineers write the code that defines the logic to be programmed onto the FPGA. This is typically done in VHDL or Verilog. This stage is the most resource-intensive, requiring specialized expertise and rigorous testing to ensure the logic is flawless before deployment.

- Simulation and Verification ▴ Before programming the physical hardware, the HDL code is exhaustively tested in a simulation environment. This process verifies the logical correctness of the design and measures its theoretical latency performance. Any bugs found at this stage are far less costly to fix than after deployment.

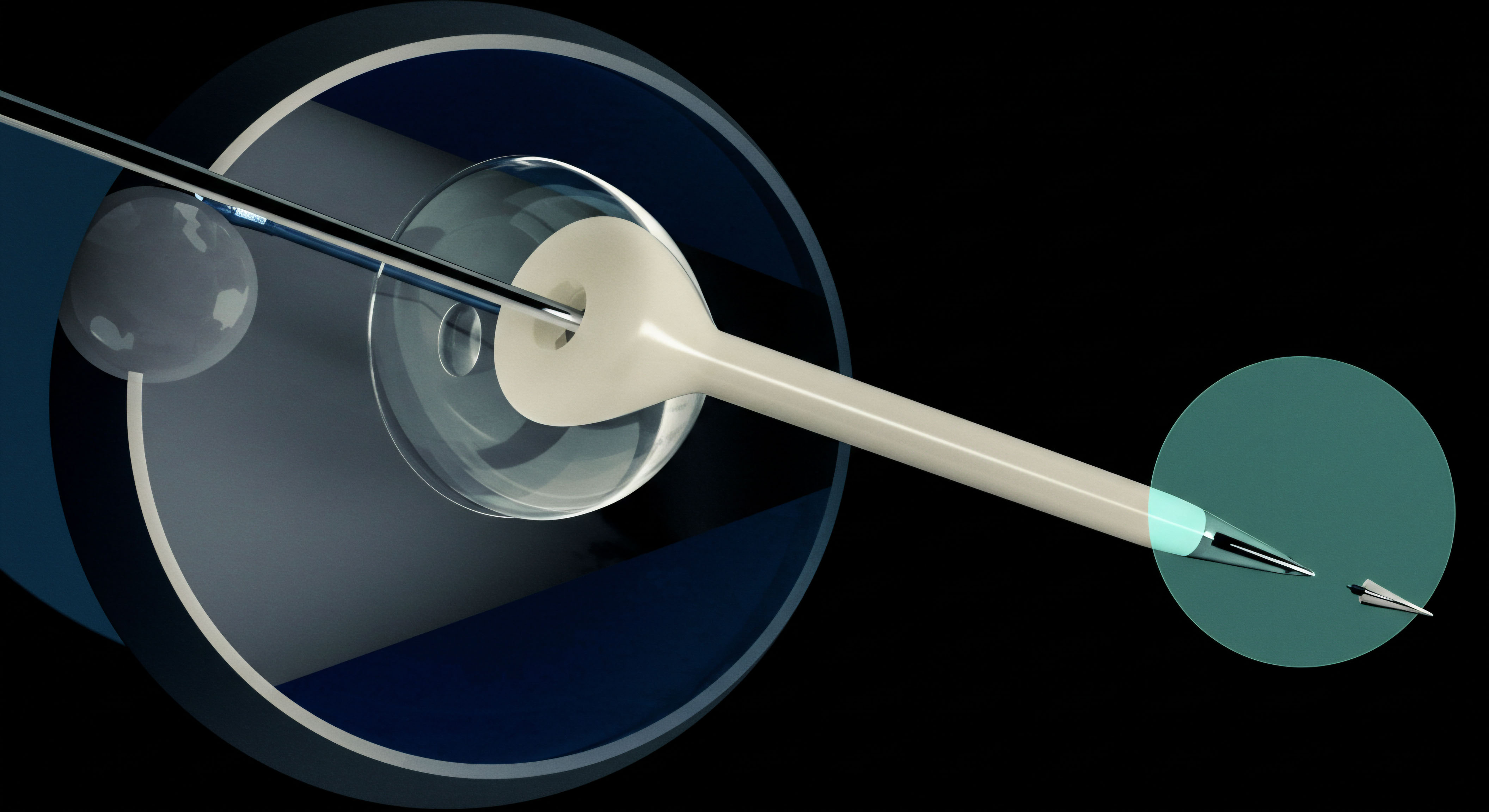

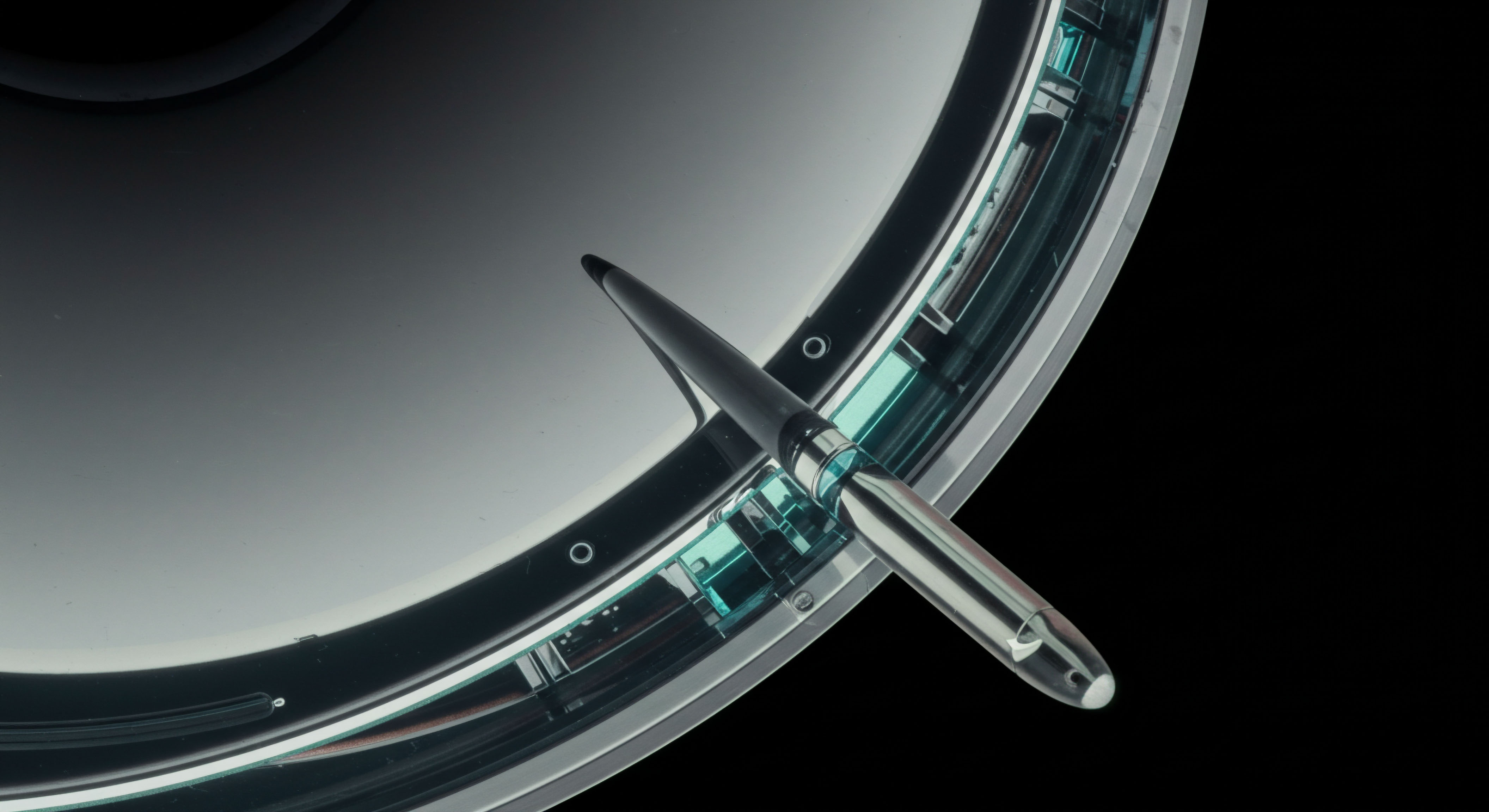

- Physical Deployment and Co-Location ▴ The configured FPGA cards are installed in servers located within the exchange’s co-location data center. Physical placement and network connectivity are meticulously planned to minimize cable lengths and the number of network hops to the exchange’s matching engine.

- System-Level Integration and Monitoring ▴ The hardware component is integrated with the software-based portion of the trading system. A well-defined API allows the software to control and receive data from the FPGA. Continuous, real-time monitoring of the hardware’s performance and health is established to ensure operational stability.

Quantitative Modeling of Latency Reduction

The impact of hardware acceleration is quantifiable and can be modeled through a detailed latency budget. This budget itemizes the time consumed at each step of the quote processing pipeline. The primary goal is to minimize the “tick-to-quote” latency ▴ the time from when a relevant market data packet enters the firm’s infrastructure to when a responsive quote packet is sent back to the exchange. The table below illustrates a comparative latency budget for a typical high-performance trading system, contrasting a software-only path with a hardware-accelerated path.

| Processing Stage | Software-Only Path (Nanoseconds) | FPGA-Accelerated Path (Nanoseconds) | Description |

|---|---|---|---|

| Packet Ingress (NIC to Kernel) | 1,500 – 3,000 | N/A (Bypassed) | Time for the network packet to travel from the NIC through the OS kernel network stack. |

| Kernel to User Space | 1,000 – 2,000 | N/A (Bypassed) | Context switch delay to deliver the packet data to the application. |

| Packet Ingress (NIC to FPGA) | N/A | 50 – 80 | Direct memory access from the NIC to the FPGA, bypassing the CPU and OS. |

| Protocol Decoding | 500 – 1,500 | 80 – 120 | Parsing the market data message (e.g. FIX protocol). Executed in parallel on FPGA. |

| Trading Logic Execution | 1,000 – 5,000+ | 100 – 300 | Applying the quoting logic. Highly variable in software, deterministic in hardware. |

| Order Serialization | 300 – 800 | 60 – 100 | Constructing the outbound quote packet. |

| User Space to Kernel | 800 – 1,500 | N/A (Bypassed) | Handing the outbound packet from the application back to the OS kernel. |

| Packet Egress (FPGA to NIC) | N/A | 40 – 70 | Direct path from the FPGA logic to the network wire. |

| Total Tick-to-Quote Latency | 5,100 – 13,800+ | 330 – 670 | Represents an improvement of over 10-20x. |

The execution of a hardware-accelerated strategy transforms latency from an unpredictable variable into a precisely engineered and minimized constant.

This quantitative breakdown demonstrates how hardware acceleration achieves its performance gains. It eliminates the largest and most variable sources of latency associated with the operating system and software execution. The result is a system that is not only faster by an order of magnitude but also operates with a degree of determinism that software-based systems cannot replicate. This predictability is the ultimate execution advantage in firm quote reporting.

References

- Hasbrouck, Joel. Empirical Market Microstructure ▴ The Institutions, Economics, and Econometrics of Securities Trading. Oxford University Press, 2007.

- Harris, Larry. Trading and Exchanges ▴ Market Microstructure for Practitioners. Oxford University Press, 2003.

- Aldridge, Irene. High-Frequency Trading ▴ A Practical Guide to Algorithmic Strategies and Trading Systems. 2nd ed. Wiley, 2013.

- Lehalle, Charles-Albert, and Sophie Laruelle. Market Microstructure in Practice. World Scientific Publishing, 2013.

- Narang, Rishi K. Inside the Black Box ▴ A Simple Guide to Quantitative and High-Frequency Trading. 2nd ed. Wiley, 2013.

- Budish, Eric, et al. “The High-Frequency Trading Arms Race ▴ Frequent Batch Auctions as a Market Design Response.” The Quarterly Journal of Economics, vol. 130, no. 4, 2015, pp. 1547-1621.

- “FPGA-Based Acceleration in Electronic Trading ▴ A Technical Overview.” Xilinx White Paper (WP428), 2018.

- O’Hara, Maureen. Market Microstructure Theory. Blackwell Publishing, 1995.

Reflection

The Co-Design of Strategy and Infrastructure

The integration of hardware acceleration into a firm’s quoting system is a profound operational shift. It moves the firm’s technological base from a collection of software applications to a cohesive, high-performance machine. The infrastructure is no longer a passive utility supporting a trading strategy; it becomes an active, integral component of the strategy itself.

This reality necessitates a new perspective ▴ the co-design of trading logic and the physical hardware that executes it. The most advanced firms no longer ask, “How can our hardware run this strategy faster?” They now ask, “What new strategies become possible with this hardware?”

This perspective reframes the investment in FPGAs and specialized hardware. It ceases to be a simple capital expenditure and becomes an investment in strategic capability. The ability to control latency at the nanosecond level, to process market data with absolute determinism, and to guarantee a response time for every quote provides a durable competitive advantage.

It allows the firm to build strategies that are simply untenable on conventional, software-based systems. As markets continue to evolve in speed and complexity, the firms that will lead are those that view their technology not as a support function, but as the very foundation of their ability to compete.

Glossary

Firm Quote Reporting

Market Data

Adverse Selection

Firm Quote

Trading Logic

Quote Reporting

Determinism

Hardware Acceleration

Fpga

Latency Arbitrage